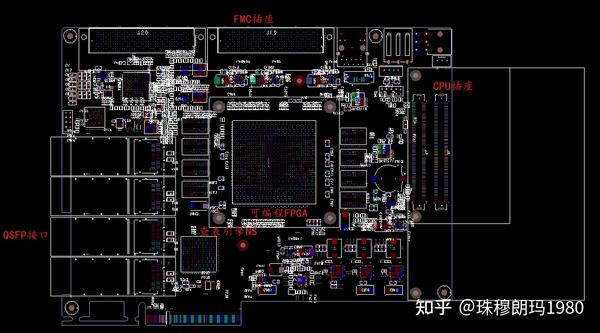

基于国产FPGA研制了软件定义智能网卡FIA原型验证卡,原型验证卡主要由国产FPGA和国产查表引擎NS组成,提供了PCIE3.0 x8金手指,提供了FMC扩展插座,左边是QSFP接口,右边是CPU插座。

主要技术指标:

1)核心硬件:国产FPGA;

2)系统接口:PCIe 3.0 x 8;

3)网络接口:4路QSFP28接口,含2路QSFP;

4)CPU接口:FT2000/4 Type6/7;

5)扩展接口:10Gbps x 10 FMC插座;

6)存储:DDR3 64GB;

7)结构尺寸:全高半长PCIe卡。

主要应用场景:

1)智能网卡;

2)FPGA加速卡(加解密、压缩/解压缩、NFV、防火墙/分流器);

3)FPGA阵列。

研制过程中切实感受到了芯片产能的紧张,价格的飞涨。

基于国产FPGA的40GE、100GE接口正在紧张验证ing。

module xlmac_hsec_top #(

parameter SERDES_WIDTH = 64,

parameter [15:0] MAX_WAIT_VALUE = 19_669 * ( 1 << log2(SERDES_WIDTH)) / SERDES_WIDTH

)

(

input wire AN_clk,

input wire AN_resetn,

input wire ctl_autoneg_enable,

input wire ctl_autoneg_bypass,

input wire [7:0] ctl_AN_nonce_seed,

input wire ctl_AN_pseudo_sel,

input wire ctl_restart_negotiation,

input wire ctl_AN_local_fault,

input wire ctl_AN_PAUSE,

input wire ctl_AN_ASMDIR,

input wire ctl_AN_ability_1GKX,

input wire ctl_AN_ability_10GKX4,

input wire ctl_AN_ability_10GKR,

input wire ctl_AN_ability_40GKR4,

input wire ctl_AN_ability_40GCR4,

input wire ctl_AN_ability_100GCR10,

output wire [1:0] stat_AN_link_cntl_1000BASE_KX,

output wire [1:0] stat_AN_link_cntl_10GBASE_KX4,

output wire [1:0] stat_AN_link_cntl_10GBASE_KR,

output wire [1:0] stat_AN_link_cntl_40GBASE_KR4,

output wire [1:0] stat_AN_link_cntl_40GBASE_CR4,

output wire [1:0] stat_AN_link_cntl_100GBASE_CR10,

output wire stat_AN_FEC_Enable,

output wire stat_AN_TX_PAUSE_Enable,

output wire stat_AN_RX_PAUSE_Enable,

output wire stat_AN_autoneg_complete,

output wire stat_AN_parallel_detection_fault,

input wire ctl_AN_FEC_request,

input wire ctl_AN_FEC_ability_override,

output wire stat_AN_lp_ability_1GKX,

output wire stat_AN_lp_ability_10GKX4,

output wire stat_AN_lp_ability_10GKR,

output wire stat_AN_lp_ability_40GKR4,

output wire stat_AN_lp_ability_40GCR4,

output wire stat_AN_lp_ability_100GCR10,

output wire stat_AN_lp_PAUSE,

output wire stat_AN_lp_ASM_DIR,

output wire stat_AN_lp_RF,

output wire stat_AN_lp_FEC_ability,

output wire stat_AN_lp_FEC_Request,

output wire stat_AN_lp_autoneg_able,

output wire stat_AN_lp_Ability_Valid,

input wire ctl_AN_loc_np,

output wire stat_AN_loc_np_ack,

input wire [47:0] AN_loc_np_data,

output wire stat_AN_lp_np,

input wire ctl_AN_lp_np_ack,

output wire [47:0] AN_lp_np_data,

input wire ctl_lt_training_enable,

input wire ctl_lt_restart_training,

input wire [4-1:0] ctl_lt_rx_trained,

output wire [4-1:0] stat_lt_signal_detect,

output wire [4-1:0] stat_lt_training_fail,

output wire [4-1:0] stat_lt_frame_lock,

output wire [4-1:0] stat_lt_preset_from_rx,

output wire [4-1:0] stat_lt_initialize_from_rx,

output wire [4-1:0] stat_lt_training,

output wire [4-1:0] stat_lt_rx_sof,

output wire [1:0] stat_lt_k_p1_from_rx0,

output wire [1:0] stat_lt_k0_from_rx0,

output wire [1:0] stat_lt_k_m1_from_rx0,

output wire [1:0] stat_lt_stat_p1_from_rx0,

output wire [1:0] stat_lt_stat0_from_rx0,

output wire [1:0] stat_lt_stat_m1_from_rx0,

input wire [10:0] ctl_lt_pseudo_seed0,

output wire [1:0] stat_lt_k_p1_from_rx1,

output wire [1:0] stat_lt_k0_from_rx1,

output wire [1:0] stat_lt_k_m1_from_rx1,

output wire [1:0] stat_lt_stat_p1_from_rx1,

output wire [1:0] stat_lt_stat0_from_rx1,

output wire [1:0] stat_lt_stat_m1_from_rx1,

input wire [10:0] ctl_lt_pseudo_seed1,

output wire [1:0] stat_lt_k_p1_from_rx2,

output wire [1:0] stat_lt_k0_from_rx2,

output wire [1:0] stat_lt_k_m1_from_rx2,

output wire [1:0] stat_lt_stat_p1_from_rx2,

output wire [1:0] stat_lt_stat0_from_rx2,

output wire [1:0] stat_lt_stat_m1_from_rx2,

input wire [10:0] ctl_lt_pseudo_seed2,

output wire [1:0] stat_lt_k_p1_from_rx3,

output wire [1:0] stat_lt_k0_from_rx3,

output wire [1:0] stat_lt_k_m1_from_rx3,

output wire [1:0] stat_lt_stat_p1_from_rx3,

output wire [1:0] stat_lt_stat0_from_rx3,

output wire [1:0] stat_lt_stat_m1_from_rx3,

input wire [10:0] ctl_lt_pseudo_seed3,

input wire [4-1:0] ctl_lt_preset_to_tx,

input wire [4-1:0] ctl_lt_initialize_to_tx,

input wire [1:0] ctl_lt_k_p1_to_tx0,

input wire [1:0] ctl_lt_k0_to_tx0,

input wire [1:0] ctl_lt_k_m1_to_tx0,

input wire [1:0] ctl_lt_stat_p1_to_tx0,

input wire [1:0] ctl_lt_stat0_to_tx0,

input wire [1:0] ctl_lt_stat_m1_to_tx0,

input wire [1:0] ctl_lt_k_p1_to_tx1,

input wire [1:0] ctl_lt_k0_to_tx1,

input wire [1:0] ctl_lt_k_m1_to_tx1,

input wire [1:0] ctl_lt_stat_p1_to_tx1,

input wire [1:0] ctl_lt_stat0_to_tx1,

input wire [1:0] ctl_lt_stat_m1_to_tx1,

input wire [1:0] ctl_lt_k_p1_to_tx2,

input wire [1:0] ctl_lt_k0_to_tx2,

input wire [1:0] ctl_lt_k_m1_to_tx2,

input wire [1:0] ctl_lt_stat_p1_to_tx2,

input wire [1:0] ctl_lt_stat0_to_tx2,

input wire [1:0] ctl_lt_stat_m1_to_tx2,

input wire [1:0] ctl_lt_k_p1_to_tx3,

input wire [1:0] ctl_lt_k0_to_tx3,

input wire [1:0] ctl_lt_k_m1_to_tx3,

input wire [1:0] ctl_lt_stat_p1_to_tx3,

input wire [1:0] ctl_lt_stat0_to_tx3,

input wire [1:0] ctl_lt_stat_m1_to_tx3,

output wire stat_rx_truncated,

input wire ctl_FEC_RX_Enable,

output wire [4-1:0] stat_FEC_inc_correct_count,

output wire [4-1:0] stat_FEC_inc_cant_correct_count,

output wire [4-1:0] stat_FEC_lock_error,

output wire [4-1:0] stat_FEC_rx_lock,

input wire ctl_FEC_TX_Enable,

// MAC PORT LIST

input wire rx_resetn,

input wire dcm_reset,

input wire mmcm_reset,

input wire refclk0_i,

input wire dclk,

input wire ctl_rx_force_resync,

input wire ctl_rx_ignore_fcs,

input wire ctl_rx_delete_fcs,

input wire ctl_rx_enable,

output wire stat_rx_hi_ber,

input wire rx_serdes_data_n0,

input wire rx_serdes_data_p0,

input wire rx_serdes_data_n1,

input wire rx_serdes_data_p1,

input wire rx_serdes_data_n2,

input wire rx_serdes_data_p2,

input wire rx_serdes_data_n3,

input wire rx_serdes_data_p3,

input wire clk,

output wire [512-1:0] rx_dataout,

output wire rx_enaout,

output wire rx_sopout,

output wire rx_eopout,

output wire rx_errout,

output wire [6-1:0] rx_mtyout,

output wire [4-1:0] stat_rx_synced,

output wire [4-1:0] stat_rx_synced_err,

output wire [4-1:0] stat_rx_mf_len_err,

output wire [4-1:0] stat_rx_mf_repeat_err,

output wire [4-1:0] stat_rx_mf_err,

output wire [4-1:0] stat_rx_block_lock,

output wire stat_rx_aligned,

output wire stat_rx_status,

output wire stat_rx_misaligned,

output wire stat_rx_aligned_err,

output wire stat_rx_bip_err_0,

output wire [2-1:0] stat_rx_vl_number_0,

input wire [63:0] ctl_rx_vl_marker_id0,

output wire stat_rx_framing_err_valid_0,

output wire [4-1:0] stat_rx_framing_err_0,

output wire stat_rx_bip_err_1,

output wire [2-1:0] stat_rx_vl_number_1,

input wire [63:0] ctl_rx_vl_marker_id1,

output wire stat_rx_framing_err_valid_1,

output wire [4-1:0] stat_rx_framing_err_1,

output wire stat_rx_bip_err_2,

output wire [2-1:0] stat_rx_vl_number_2,

input wire [63:0] ctl_rx_vl_marker_id2,

output wire stat_rx_framing_err_valid_2,

output wire [4-1:0] stat_rx_framing_err_2,

output wire stat_rx_bip_err_3,

output wire [2-1:0] stat_rx_vl_number_3,

input wire [63:0] ctl_rx_vl_marker_id3,

output wire stat_rx_framing_err_valid_3,

output wire [4-1:0] stat_rx_framing_err_3,

input wire [15:0] ctl_rx_vl_length_minus1,

input wire [14:0] ctl_rx_max_packet_len,

input wire [7:0] ctl_rx_min_packet_len,

input wire ctl_local_loopback,

input wire ctl_tx_test_pattern,

input wire ctl_rx_test_pattern,

output wire [3-1:0] stat_rx_total_packets,

output wire stat_rx_total_good_packets,

output wire [8-1:0] stat_rx_total_bytes,

output wire [14-1:0] stat_rx_total_good_bytes,

output wire [3-1:0] stat_rx_packet_small,

output wire stat_rx_jabber,

output wire stat_rx_packet_large,

output wire stat_rx_oversize,

output wire [3-1:0] stat_rx_undersize,

output wire stat_rx_toolong,

output wire [3-1:0] stat_rx_fragment,

output wire stat_rx_packet_64_bytes,

output wire stat_rx_packet_65_127_bytes,

output wire stat_rx_packet_128_255_bytes,

output wire stat_rx_packet_256_511_bytes,

output wire stat_rx_packet_512_1023_bytes,

output wire stat_rx_packet_1024_1518_bytes,

output wire stat_rx_packet_1519_1522_bytes,

output wire stat_rx_packet_1523_1548_bytes,

output wire [3-1:0] stat_rx_bad_fcs,

output wire stat_rx_packet_bad_fcs,

output wire [3-1:0] stat_rx_stomped_fcs,

output wire stat_rx_packet_1549_2047_bytes,

output wire stat_rx_packet_2048_4095_bytes,

output wire stat_rx_packet_4096_8191_bytes,

output wire stat_rx_packet_8192_9215_bytes,

output wire stat_rx_unicast,

output wire stat_rx_multicast,

output wire stat_rx_broadcast,

output wire stat_rx_vlan,

output wire stat_rx_pause,

output wire stat_rx_user_pause,

output wire stat_rx_inrangeerr,

output wire stat_rx_remote_fault,

output wire stat_rx_local_fault,

output wire stat_rx_internal_local_fault,

output wire stat_rx_received_local_fault,

input wire ctl_rx_process_lfi,

input wire ctl_rx_check_sfd,

input wire ctl_rx_check_preamble,

output wire [3-1:0] stat_rx_bad_code,

output wire [2-1:0] stat_rx_test_pattern_mismatch,

output wire stat_rx_bad_preamble,

output wire stat_rx_bad_sfd,

output wire stat_rx_got_signal_os,

output wire [4-1:0] stat_rx_vl_demuxed,

// MAC PORT LIST

input wire tx_resetn,

output wire tx_ovfout,

output wire tx_unfout,

output wire tx_rdyout,

input wire [512-1:0] tx_datain,

input wire tx_enain,

input wire tx_sopin,

input wire tx_eopin,

input wire tx_errin,

input wire [6-1:0] tx_mtyin,

output wire tx_serdes_data_n0,

output wire tx_serdes_data_p0,

output wire tx_serdes_data_n1,

output wire tx_serdes_data_p1,

output wire tx_serdes_data_n2,

output wire tx_serdes_data_p2,

output wire tx_serdes_data_n3,

output wire tx_serdes_data_p3,

input wire [63:0] ctl_tx_vl_marker_id0,

input wire [63:0] ctl_tx_vl_marker_id1,

input wire [63:0] ctl_tx_vl_marker_id2,

input wire [63:0] ctl_tx_vl_marker_id3,

input wire ctl_tx_enable,

input wire ctl_tx_fcs_ins_enable,

input wire ctl_tx_ignore_fcs,

input wire ctl_tx_send_rfi,

input wire ctl_tx_send_idle,

input wire [15:0] ctl_tx_vl_length_minus1,

output wire stat_tx_total_packets,

output wire [7-1:0] stat_tx_total_bytes,

output wire stat_tx_total_good_packets,

output wire [14-1:0] stat_tx_total_good_bytes,

output wire stat_tx_packet_64_bytes,

output wire stat_tx_packet_65_127_bytes,

output wire stat_tx_packet_128_255_bytes,

output wire stat_tx_packet_256_511_bytes,

output wire stat_tx_packet_512_1023_bytes,

output wire stat_tx_packet_1024_1518_bytes,

output wire stat_tx_packet_1519_1522_bytes,

output wire stat_tx_packet_1523_1548_bytes,

output wire stat_tx_packet_small,

output wire stat_tx_packet_large,

output wire stat_tx_packet_1549_2047_bytes,

output wire stat_tx_packet_2048_4095_bytes,

output wire stat_tx_packet_4096_8191_bytes,

output wire stat_tx_packet_8192_9215_bytes,

output wire stat_tx_unicast,

output wire stat_tx_multicast,

output wire stat_tx_broadcast,

output wire stat_tx_vlan,

output wire stat_tx_pause,

output wire stat_tx_user_pause,

output wire stat_tx_bad_fcs,

input wire ctl_rx_enable_gcp,

input wire ctl_rx_check_mcast_gcp,

input wire ctl_rx_check_ucast_gcp,

input wire [47:0] ctl_rx_pause_da_ucast,

input wire ctl_rx_check_sa_gcp,

input wire [47:0] ctl_rx_pause_sa,

input wire ctl_rx_check_etype_gcp,

input wire [15:0] ctl_rx_etype_gcp,

input wire ctl_rx_check_opcode_gcp,

input wire [15:0] ctl_rx_opcode_min_gcp,

input wire [15:0] ctl_rx_opcode_max_gcp,

input wire ctl_rx_enable_pcp,

input wire ctl_rx_check_mcast_pcp,

input wire ctl_rx_check_ucast_pcp,

input wire [47:0] ctl_rx_pause_da_mcast,

input wire ctl_rx_check_sa_pcp,

input wire ctl_rx_check_etype_pcp,

input wire [15:0] ctl_rx_etype_pcp,

input wire ctl_rx_check_opcode_pcp,

input wire [15:0] ctl_rx_opcode_min_pcp,

input wire [15:0] ctl_rx_opcode_max_pcp,

input wire ctl_rx_enable_gpp,

input wire ctl_rx_check_mcast_gpp,

input wire ctl_rx_check_ucast_gpp,

input wire ctl_rx_check_sa_gpp,

input wire ctl_rx_check_etype_gpp,

input wire [15:0] ctl_rx_etype_gpp,

input wire ctl_rx_check_opcode_gpp,

input wire [15:0] ctl_rx_opcode_gpp,

input wire ctl_rx_enable_ppp,

input wire ctl_rx_check_mcast_ppp,

input wire ctl_rx_check_ucast_ppp,

input wire ctl_rx_check_sa_ppp,

input wire ctl_rx_check_etype_ppp,

input wire [15:0] ctl_rx_etype_ppp,

input wire ctl_rx_check_opcode_ppp,

input wire ctl_rx_forward_control,

input wire [15:0] ctl_rx_opcode_ppp,

input wire [8:0] ctl_rx_pause_ack,

input wire ctl_rx_check_ack,

output wire [8:0] stat_rx_pause_req,

output wire [8:0] stat_rx_pause_valid,

output wire [15:0] stat_rx_pause_quanta0,

output wire [15:0] stat_rx_pause_quanta1,

output wire [15:0] stat_rx_pause_quanta2,

output wire [15:0] stat_rx_pause_quanta3,

output wire [15:0] stat_rx_pause_quanta4,

output wire [15:0] stat_rx_pause_quanta5,

output wire [15:0] stat_rx_pause_quanta6,

output wire [15:0] stat_rx_pause_quanta7,

output wire [15:0] stat_rx_pause_quanta8,

input wire [8:0] ctl_tx_pause_req,

input wire [15:0] ctl_tx_pause_refresh_timer0,

input wire [15:0] ctl_tx_pause_refresh_timer1,

input wire [15:0] ctl_tx_pause_refresh_timer2,

input wire [15:0] ctl_tx_pause_refresh_timer3,

input wire [15:0] ctl_tx_pause_refresh_timer4,

input wire [15:0] ctl_tx_pause_refresh_timer5,

input wire [15:0] ctl_tx_pause_refresh_timer6,

input wire [15:0] ctl_tx_pause_refresh_timer7,

input wire [15:0] ctl_tx_pause_refresh_timer8,

input wire [15:0] ctl_tx_pause_quanta0,

input wire [15:0] ctl_tx_pause_quanta1,

input wire [15:0] ctl_tx_pause_quanta2,

input wire [15:0] ctl_tx_pause_quanta3,

input wire [15:0] ctl_tx_pause_quanta4,

input wire [15:0] ctl_tx_pause_quanta5,

input wire [15:0] ctl_tx_pause_quanta6,

input wire [15:0] ctl_tx_pause_quanta7,

input wire [15:0] ctl_tx_pause_quanta8,

input wire [47:0] ctl_tx_da_gpp,

input wire [47:0] ctl_tx_sa_gpp,

input wire [15:0] ctl_tx_ethertype_gpp,

input wire [15:0] ctl_tx_opcode_gpp,

input wire [47:0] ctl_tx_da_ppp,

input wire [47:0] ctl_tx_sa_ppp,

input wire [15:0] ctl_tx_ethertype_ppp,

input wire [15:0] ctl_tx_opcode_ppp,

input wire ctl_tx_resend_pause,

output wire [9-1:0] stat_tx_pause_valid,

input wire [8:0] ctl_rx_pause_enable,

input wire [8:0] ctl_tx_pause_enable,

output wire stat_tx_underflow_err,

output wire stat_tx_overflow_err,

output wire stat_tx_local_fault,

output wire stat_tx_frame_error

);作者:珠穆朗玛2048

来源:https://zhuanlan.zhihu.com/p/361302104更多FPGA智能网卡相关技术干货请关注FPGA加速器技术专栏。