相比Verilog HLD,数字IC设计(RTL开发)人员会觉得SVA学习起来比较复杂。如果一个设计人员不得不书写超过3行的SVA代码,这个工作肯定会迅速转到验证工程师身上。

所以,我们需要搞清楚2个问题:

1、什么样的断言由设计人员添加,什么样的断言由验证人员添加?

2、设计人员和设计人员应通过什么样的方式添加断言?

一个比较建议的做法是,设计人员直接在RTL内部添加low‐level and simple 断言、由验证人员通过bind方式添加higher‐level and complex 断言。验证人员通过bind方式添加断言的方式能够避免修改RTL带来的风险。

对于书写的断言,最好能够遵循下列几个建议:

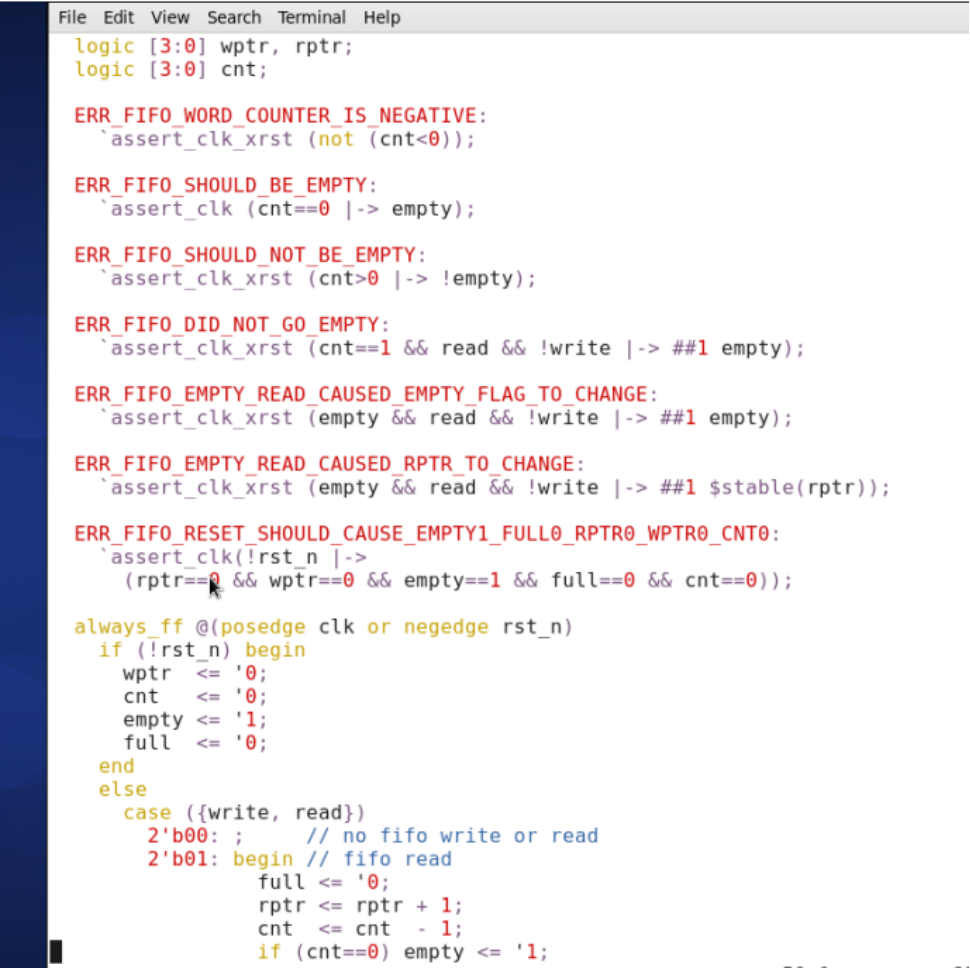

1、当断言比较复杂,或者比较多的时候,书写在单独的SV文件中。避免像下面这样头重脚轻,无法快速分析需要综合的RTL代码。

2、 尽量使用并发断言,因为现在大部分的电路都是同步设计,并发断言能够减少采样次数,提高仿真效率。

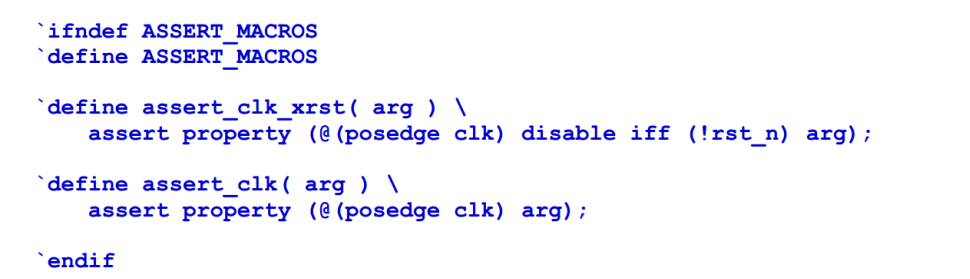

3、 使用一个宏文件定义assert property。因为就像前文提到的“如果一个设计人员不得不书写超过3行的SVA代码,这个工作肯定会迅速转到验证工程师身上”。正确的做法应该如下图所示:

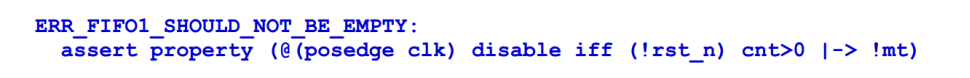

通过上述这个宏定义,就可以将断言

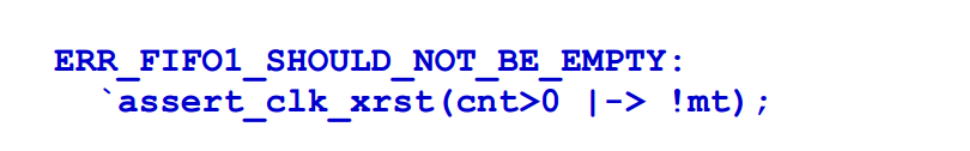

书写成

看似小小的改变,实际上能够减少我们很多书写3对“()”的编译错误,提高编译调试效率。

原文链接:https://mp.weixin.qq.com/s/9bkR8WNTOdXa9-p6xSC7iQ

授权转自数字芯片实验室公众号,请勿二次转载。

推荐阅读

更多数字IC设计技术干货等请关注数字芯片实验室专栏。