VSCode && Python软件安装包

Vscode && Python

提取码:6fvp

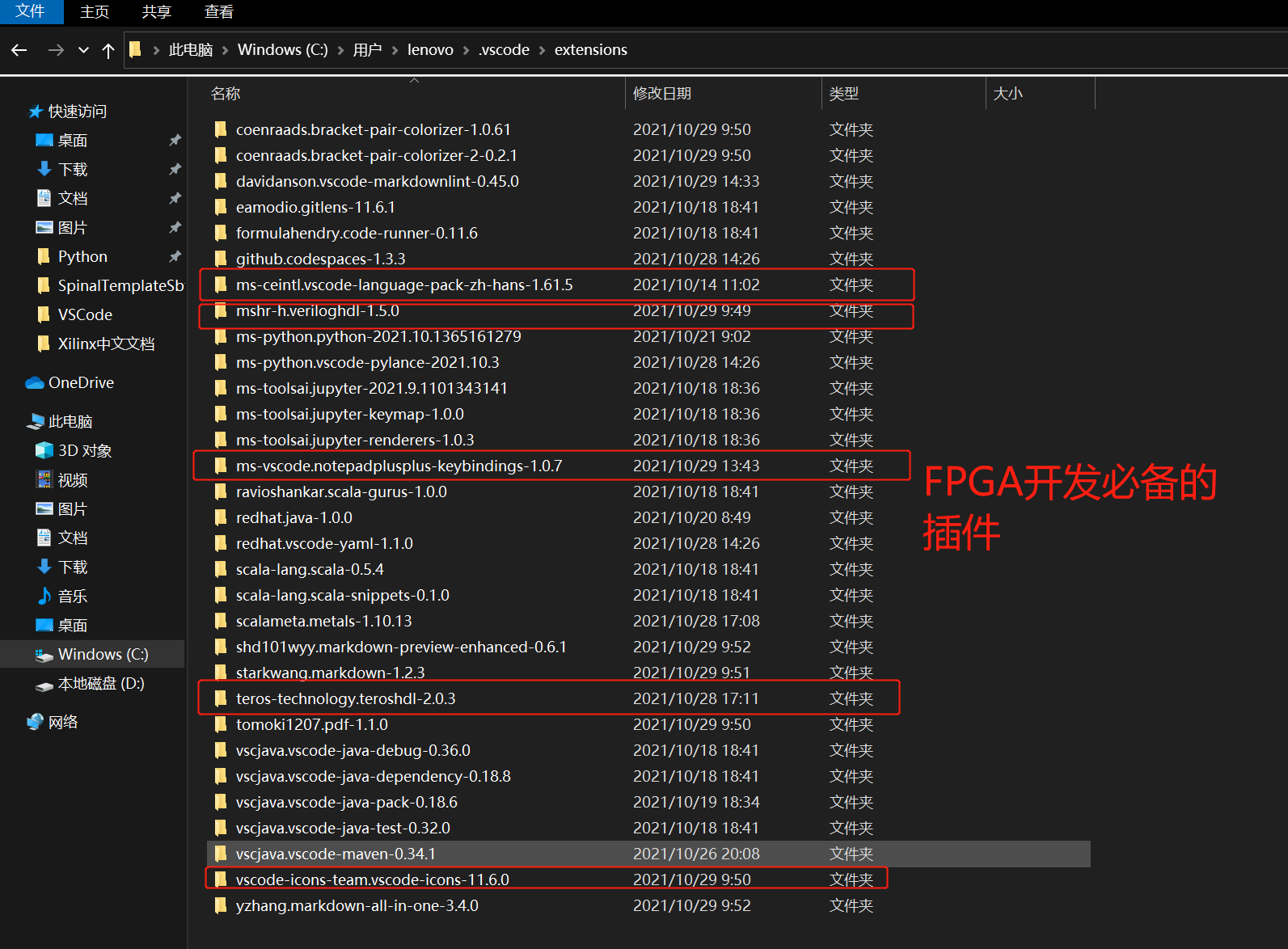

安装插件

将extensions.zip解压到路径“C:\Users\用户名.vscode\extenstion”,完成插件安装,插件自带语法高亮和自动补齐功能。已经安装的插件暂时不用也可以选择disable,因为插件太多影响速度。

VSCode设置

- VScode编码规则设置

- VSCode信任设置

- 插件设置

python依赖库安装

通过cmd进入shell,输入相应pip install path\xxx.whl指令,安装所需要的依赖库

语法检查

使用vivado的检查工具-xvlog来检查vscode编辑的代码错误,其他语法检查工具比如iverilog、verilator等,网上有教程可以根据需要安装。将Vivado安装版本的bin文件夹所在路径添加到环境变量中,打开xxx.v 就可以语法检查了,注意每次需要保存才会弹出语法错误效果如下:

悬停显示

格式对齐

模块例化、生成testbench

在一个编辑好的代码里面,点击右上角选的按钮,这样之后例化就会在剪贴板了,然后粘贴在你需要例化的代码位置即可

网表图或原理图

文档说明

模块内信号跳转与格式化

点这个就会打开xxx.v ,实际上原理是搜索你的关联路径的的下级目录找到这个文件并打开,有快捷键F12就会进入定义的位置。

选中代码块右键选择格式化文档,即可格式化对齐

用户代码片段

将文件拷贝路径C:\Users\用户名\AppData\Roaming\Code\User\snippets\verilog.code-snippets中即可

{

// Place your Global snippets here. Each snippet is defined under a snippet name and has a scope, prefix, body and

// description. Add comma separated ids of the languages where the snippet is applicable in the scope field. If scope

// is left empty or omitted, the snippet gets applied to all languages. The prefix is what is

// used to trigger the snippet and the body will be expanded and inserted. Possible variables are:

// $1, $2 for tab stops, $0 for the final cursor position, and ${1:label}, ${2:another} for placeholders.

// Placeholders with the same ids are connected.

// Example:

// "Print to console": {

// "scope": "javascript,typescript",

// "prefix": "log",

// "body": [

// "console.log('$1');",

// "$2"

// ],

// "description": "Log output to console"

// }

"NWEFILE":{

"prefix": "newfile",

"body": [

"`timescale 1ns/1ps",

"///////////////////////////////////////////////////////////////////////////////////",

"// Company : $0" ,

"// Engineer : $1" ,

"// " ,

"// Create Date : $2" ,

"// Design Name : $3" ,

"// Module Name : $4" ,

"// Project Name : $5" ,

"// Target Devices : $6" ,

"// Tool Versions : $7" ,

"// Description : $8" ,

"// " ,

"// Revision : $9" ,

"// " ,

"// Additional Comments : $10",

"// " ,

"///////////////////////////////////////////////////////////////////////////////////"

],

"description": "newfile Keywords"

},

"DEFINE": {

"prefix": "define",

"body": [

"`define C_ = ;$0"

],

"description": "define keywords"

},

"PARAMETER": {

"prefix": "parameter",

"body": [

"parameter C_ = ;$0"

],

"description": "parameter keywords"

},

"WIRE": {

"prefix": "wire",

"body": [

"wire ${1| s_,[ : 0] s_|};$0"

],

"description": "wire keywords"

},

"REG": {

"prefix": "reg",

"body": [

"reg ${1| s_ = 'd0,[ : 0] s_ = 'd0|};$0"

],

"description": "reg keywords"

},"LOCALPARAM": {

"prefix": "localparam",

"body": [

"localparam C_ = ;$0"

],

"description": "localparam keywords"

},

"ASSIGN": {

"prefix": "assign",

"body": [

"assign $0;"

],

"description": "assign keywords"

},

"GENVAR": {

"prefix": "genvar",

"body": [

"genvar $0;"

],

"description": "genvar keywords"

},

"GENERATE": {

"prefix": "generate",

"body": [

"generate",

"\t",

"endgenerate",

"$0",

"$0"

],

"description": "generate keywords"

},

"GENERATEIF": {

"prefix": "generateif",

"body": [

"generate",

"if ( $1 )",

"begin : GENERATEIF",

"\t",

"end",

"endgenerate",

"$0",

"$0"

],

"description": "generateif keywords"

},

"GENERATEFOR": {

"prefix": "generatefor",

"body": [

"genvar i;",

"generate",

"for ( i=0;i<C_GENETARE_NUM;i=i+1 )",

"begin : GENERATEFOR",

"\t",

"end",

"endgenerate",

"$0",

"$0"

],

"description": "generatefor keywords"

},

"INPUT": {

"prefix": "input",

"body": [

"input ${1|wire i_,wire [ : 0] i_|},$0"

],

"description": "INPUT statement"

},

"INOUT": {

"prefix": "inout",

"body": [

"inout ${1|wire b_,wire [ : 0] b_|},$0"

],

"description": "INOUT statement"

},

"OUTPUT": {

"prefix": "output",

"body": [

"output ${1|wire o_,wire [ : 0] o_,reg o_,reg [ : 0] o_|},$0"

],

"description": "output statement"

},

"BEGIN": {

"prefix": "begin",

"body": [

"begin",

"\t$0",

"end"

],

"description": "begin statement"

},

"IF": {

"prefix": "if",

"body": [

"if ( $1 )",

"begin",

"\t$0",

"end"

],

"description": "if statement"

},

"IFELSE": {

"prefix": "ifelse",

"body": [

"if ( $1 )",

"begin",

"\t$2",

"end",

"else",

"begin",

"\t$0",

"end"

],

"description": "if else statement"

},"ELSEIF": {

"prefix": "elif",

"body": [

"else if ( $1 )",

"begin",

"\t$0",

"end"

],

"description": "else if statement"

},

"ELSE": {

"prefix": "else",

"body": [

"else",

"begin",

"\t$0",

"end"

],

"description": "else statement"

},

"ELSEBEGIN": {

"prefix": "elseBegin",

"body": [

"else",

"begin",

"\t$0",

"end"

],

"description": "else begin statement"

},

"case": {

"prefix": "case",

"body": [

"case $1",

"\t$0",

"endcase"

],

"description": "case statement"

},

"alwayscase": {

"prefix": "always @ case",

"body": [

"always @ ( posedge clk )",

"begin",

"\tcase $2",

"\t\t$0",

"\tendcase",

"end"

],

"description": "always case statement"

},

"DEFAULT": {

"prefix": "default",

"body": [

"default : $1",

"begin",

"\t$0",

"end"

],

"description": "always case statement"

},

"alwaysclkasyncrst": {

"prefix": "alwaysclkasyncrst",

"body": [

"always @ ( posedge clk or posedge rst )$0",

"begin",

"\tif ( rst == 1'd1 )",

"\tbegin",

"\t\t$0",

"\tend",

"\telse if ( )",

"\tbegin",

"\t\t$1",

"\tend",

"\telse",

"\tbegin",

"\t\t$2",

"\tend",

"end"

],

"description": "alwaysclkasyncrst statement"

},

"alwaysclksyncrst": {

"prefix": "alwaysclksyncrst",

"body": [

"always @ ( posedge clk )$0",

"begin",

"\tif ( rst == 1'd1 )",

"\tbegin",

"\t\t$0",

"\tend",

"\telse if ( )",

"\tbegin",

"\t\t$1",

"\tend",

"\telse",

"\tbegin",

"\t\t$2",

"\tend",

"end"

],

"description": "alwaysclksyncrst statement"

},

"alwaysclk": {

"prefix": "alwaysclk",

"body": [

"always @ ( posedge clk )$0",

"begin",

"\tif ( )",

"\tbegin",

"\t\t$1",

"\tend",

"\telse",

"\tbegin",

"\t\t$2",

"\tend",

"end"

],

"description": "alwaysclk statement"

},

"MODULE":{

"prefix": "module",

"body": [

"module $TM_FILENAME_BASE $1(",

"\t${0}",

");",

"\nendmodule //$TM_FILENAME_BASE"

]

},

"MODULEWITHPARAM":{

"prefix": "modulewithparam",

"body": [

"module $TM_FILENAME_BASE # (",

"\t${0}",

")(",

"\t${1}",

");",

"\nendmodule //$TM_FILENAME_BASE"

]

}

}VSCode与Vivado关联

1.打开Vivado软件,点击Tools -> Settings 来打开设置。

2.点击Text Editor,在右侧下拉菜单中选择 Custom Editor…

3.在弹出的窗口中以下格式的文本:Vscode绝对路径 + 空格 + [file name] + 空格 + -[line number]

4.点击OK即可。