在软件行业,DevOps实践通过自动化CI/CD、基础设施即代码和协同协作,彻底重塑了开发流程,实现了快速迭代与高质量交付。然而,传统FPGA逻辑开发仍多依赖手动的、孤立的流程,存在效率瓶颈与环境一致性问题。为将敏捷性与可靠性赋能硬件开发,并大幅提升逻辑部作为平台部门的整体交付效能与标准化水平,我们亟需构建新一...

阐述CPU性能瓶颈问题如何破解,FPGA如何突围

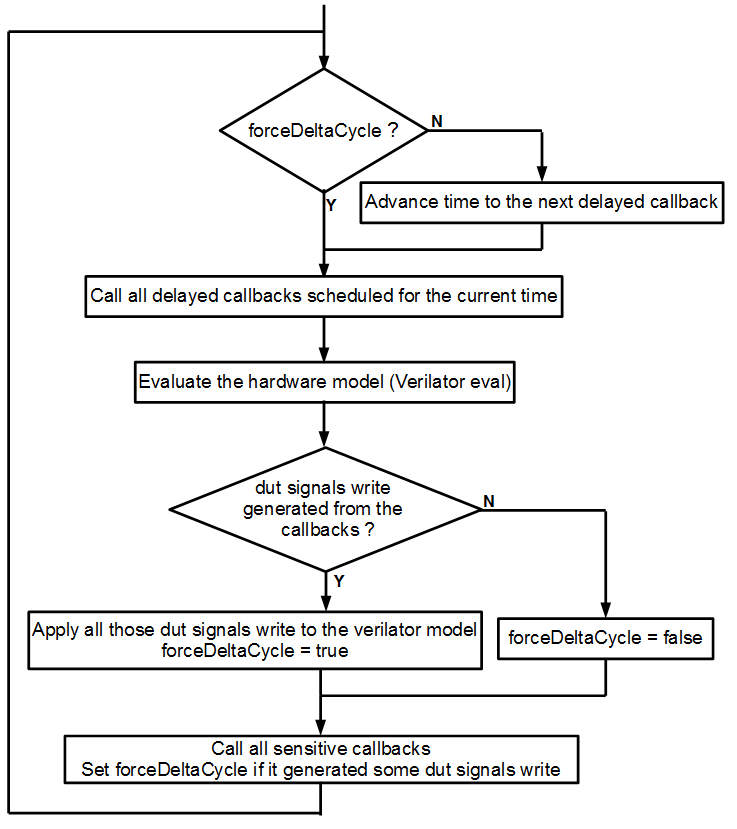

之后你可以调用compile(rtl)函数对硬件编译并为仿真器做准备。这个函数会返回SimCompiled实例。在这个SimCompiled实例中你可以用以下函数运行你的仿真:

开源Wi-Fi芯片openwifi项目相关技术进展,欢迎加入

前瞻性的眼光,和持之以恒的学习~

这一章会介绍SpinalHDL如何把名字从scala代码传递到产生的硬件中。知道这些能帮助你更好地了解如何保留名字, 以尽可能增加生成的网表的可读性。

SpinalHDL编译器会做很多设计检查,来确保生成的VHDL/Verilog是可仿真的可综合的。基本上,SpinalHDL不会生成破损的VHDL/Verilog设计。以下是SpinalHDL检查的简要概括:

SpinalHDL 是 Scala 语言的一个库,SpinaHDL 环境搭建所需的软件开发 Scala 需要使用 IDEA 软件;JDK17采用开源软件TencentKona-17.0.3.b1,Scala2.12.16,SBT1.6.2;仿真工具使用 verilator+gtkwave, 在 windows 系统需要使用 msys64 软件进行安装。

Arm相关的技术文档资料下载汇总专栏,欢迎收藏关注点赞。

想成为 IC 工程师 / 业余 FPGA,历史学,计算机网络爱好者

最有深度的半导体新媒体,实讯、专业、原创、深度,50万半导体精英关注。专注观察全球半导体最新资讯、技术前沿、发展趋势。

订阅极术公开课,即时获取最新技术公开课信息

发布瑞芯微电子最新的芯资讯及技术动态。

主要交流IC以及SoC设计流程相关的技术和知识

海思AI芯片(Hi3519A/3559A)方案学习系列笔记,欢迎关注。

含极术社区WebinarPPT下载及回放,线下活动技术干货PPT,欢迎关注

FPGAer