写在前面

笔者在工作中需要包个 PCIe wrapper,正在努力飞快学习 PCIe ing.

本文系转载,略做格式调整与增加解释(使用斜体表示),转自:

PCIe扫盲系列博文连载目录篇(第一阶段)-Felix-电子技术应用-AET-中国科技核心期刊-最丰富的电子设计资源平台

转载正文

PCIe总线事务层入门(一)

在介绍事务层之前,首先简单地了解一下PCIe总线的通信机制。

假设某个设备要对另一个设备进行读取数据的操作,首先这个设备(称之为Requester)需要向另一个设备发送一个Request,然后另一个设备(称之为Completer)通过Completion Packet返回数据或者错误信息。

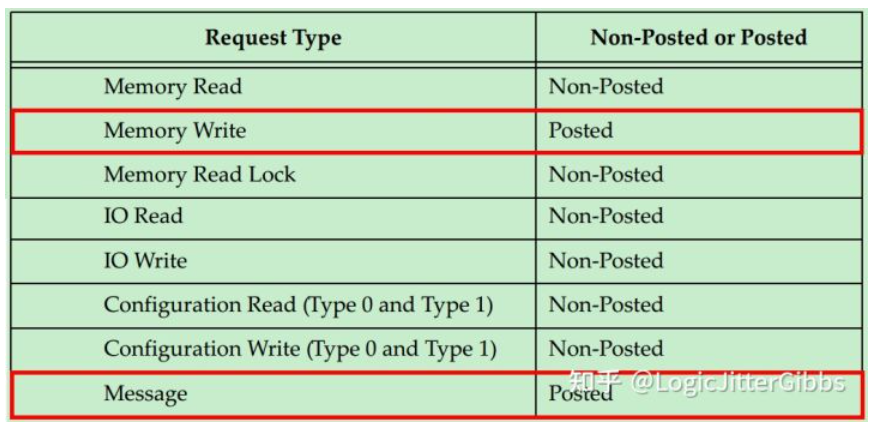

在PCIe Spec中,规定了四种类型的请求(Request):Memory、IO、Configuration和Messages。其中,前三种都是从PCI/PCI-X总线中继承过来的,第四种Messages是PCIe新增加的类型。详细的信息如下表所示:

从表中我们可以发现,只有Memory Write和Message是Posted类型的,其他的都是Non-Posted类型的。

所谓Non-posted,就是Requester发送了一个包含Request的包之后,必须要得到一个包含Completion的包的应答,这次传输才算结束,否则会进行等待。

所谓Posted,就是Requester的请求并不需要Completer通过发送包含Completion的包进行应答,当然也就不需要进行等待了。很显然,Posted类型的操作对总线的利用率(效率)要远高于Non-Posted型。

那么为什么要分为Non-Posted和Posted两种类型呢?

对于Memory Writes来说,对效率要求较高,因此采用了Posted的方式。但是这并不意味着Posted类型的操作完全不需要Completer进行应答,Completer仍然可采用另一种应答机制——Ack/Nak的机制(在数据链路层实现的)。

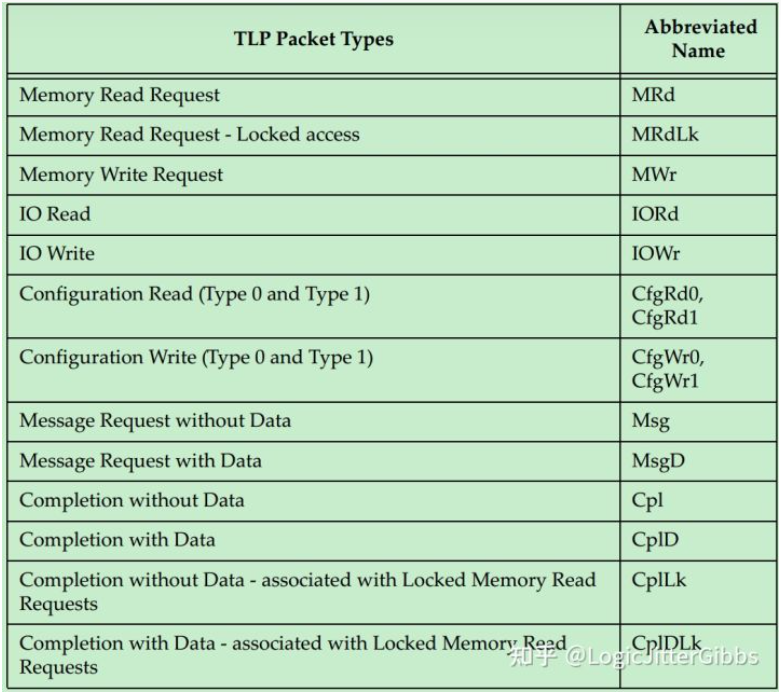

PCIe的TLP包共有一下几种类型:

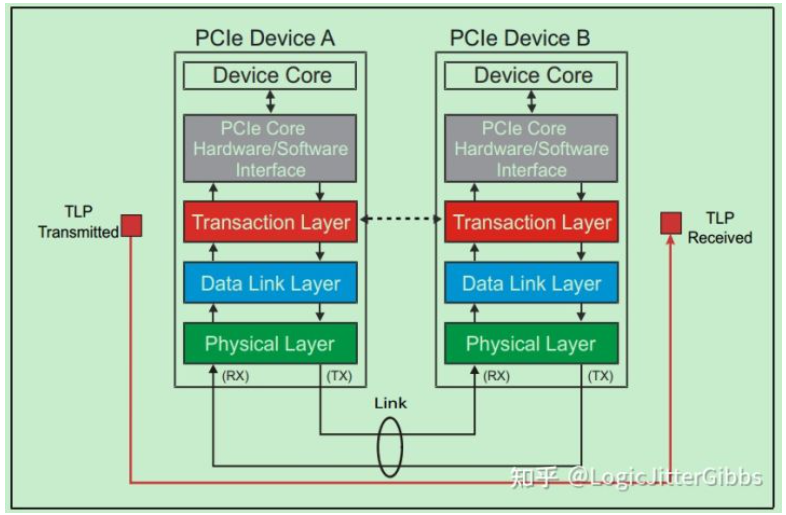

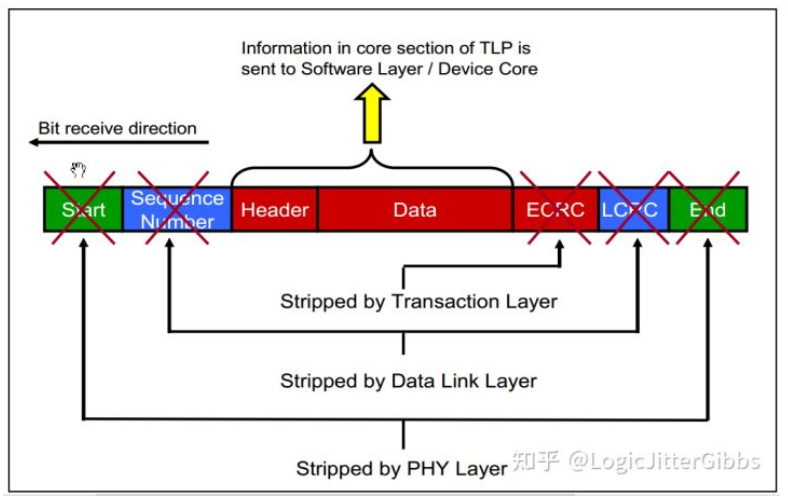

TLP传输的示意图如下图所示:

TLP在整个PCIe包结构的位置如以下两张图所示:(第一张为发送端,第二张为接收端)

发送端

接收端

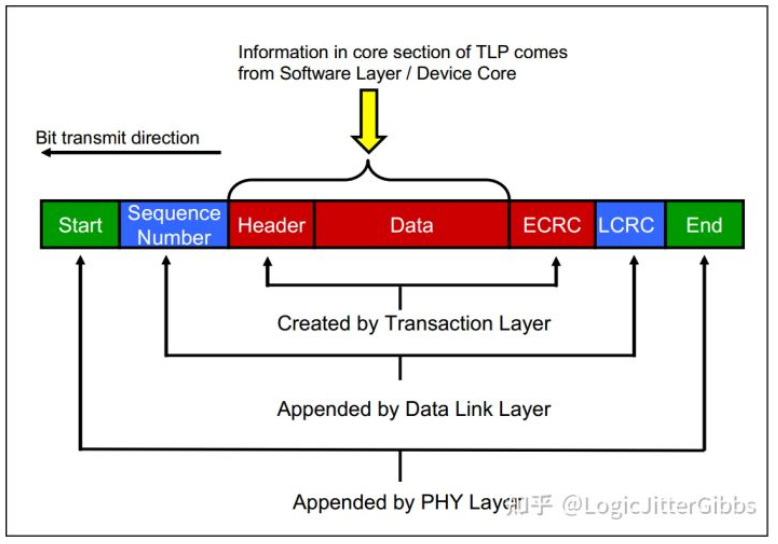

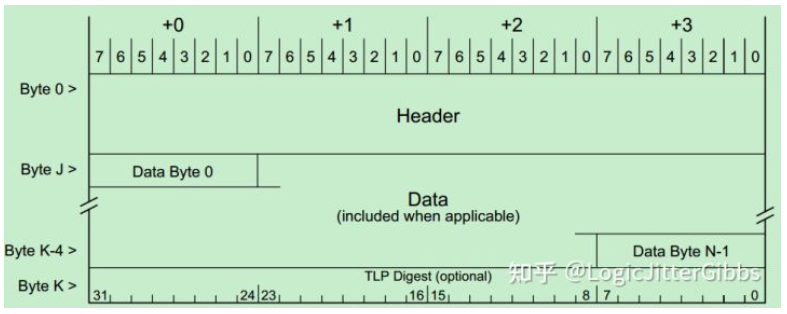

其中,TLP包的结构图如下图所示:

图中的TLP Digest即 ECRC(End-to-End CRC),是可选项。

此外,TLP的长度(包括其中的Header、Data和ECRC)是以DW(双字,即四个字节)为单位的。

PCIe总线事务层入门(二)

前面的文章介绍了TLP的几种类型以及TLP的包结构。

这篇文章来详细地聊一聊Non-Posted Transaction(包括Ordinary Read、Locked Read和IO/Configuration Writes)与Posted Writes(包括Memory Writes和Message Writes)。

Non-Posted Transaction

o Ordinary Reads

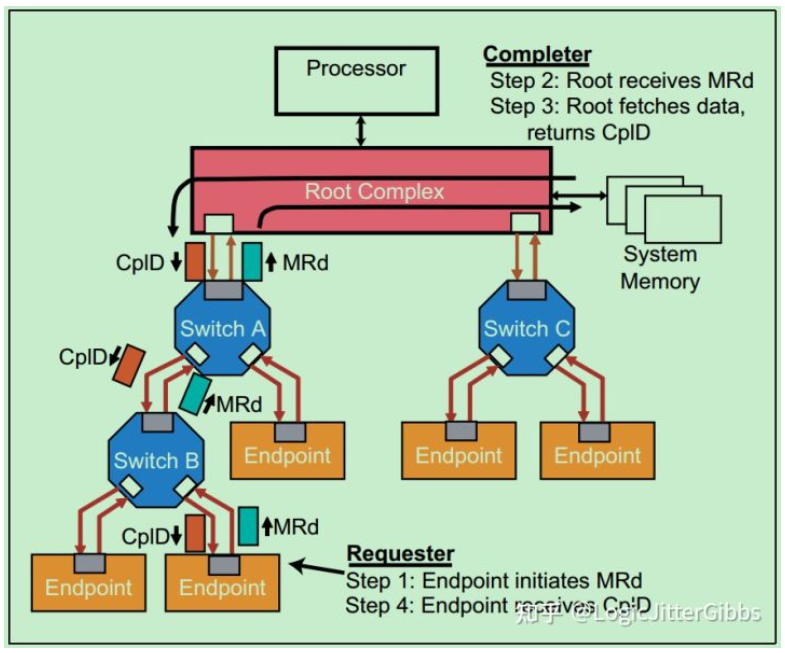

下图显示的是一个Endpoint向System Memory发送读请求(Read Request)的例子。

在这个例子中,Endpoint的读请求通过了两个Switch,然后到达其目标,即Root。

Root对读请求的包进行解码后,并从中识别出操作的地址,然后锁存数据,并将数据发送至Endpoint,即包含数据的Completion包,ClpD。

需要注意的是,PCIe允许每个包的最大数据量(Max Data Payload)为4KB,但实际上设计者往往会采用较小的Max Payload Size(比如128,256,512,1024和2048)。因此,常常一个读请求会对应多个ClpD,即将大于Max Payload Size的数据分成多个包发送。

如果遇到错误,则Root会通过Completion包告知相应的Endpoint。

注:Root向发送请求的Endpoint发送Completion包,是通过Request包中的BDF信息(Bus,Device和Function)进行查找对应的Endpoint的。关于BDF,会在后面的文章详细地介绍。

注:每个CplD的大小还受到RCB的影响,具体会在后面的文章中详细介绍。

o Locked Reads

Locked请求实际上是PCIe为了兼容早期的PCI总线而设置的一种方式,对于非PCI兼容的设计中,是不允许使用Locked操作的。

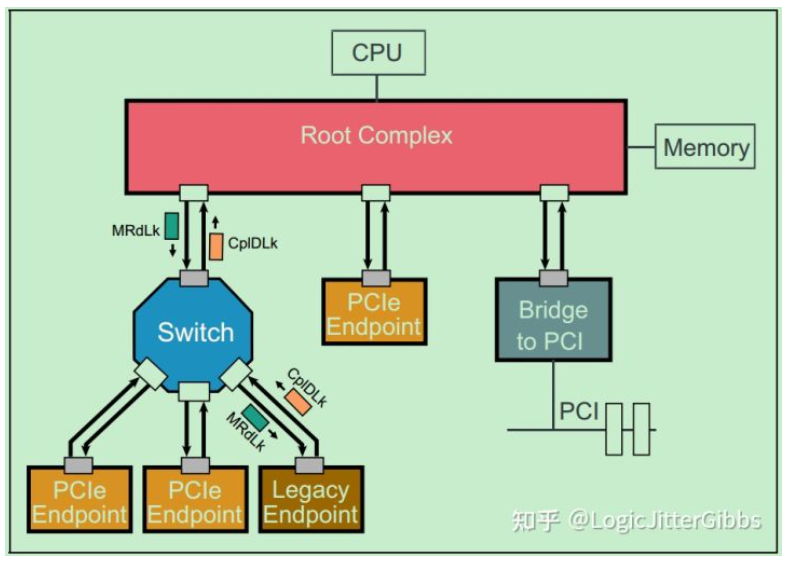

并且也只有Root可以发起Locked请求操作,Endpoint是不可以发起Locked请求操作的。下图显示的是一个简单的Locked Read请求操作:

Locked Read主要用于支持一种叫做Atomic Read-Modify-Write操作,这是一种高优先级且不可被打断的操作。主要用于测试链路状况等任务(针对PCI设备,PCIe设备禁止使用Locked操作)。

此外,Locked操作采用的是目标存储寻址(Target Memory Address)来寻找Legacy Endpoint(PCI设备),而不是采用前面介绍的BDF。

o IO/Configuration Writes

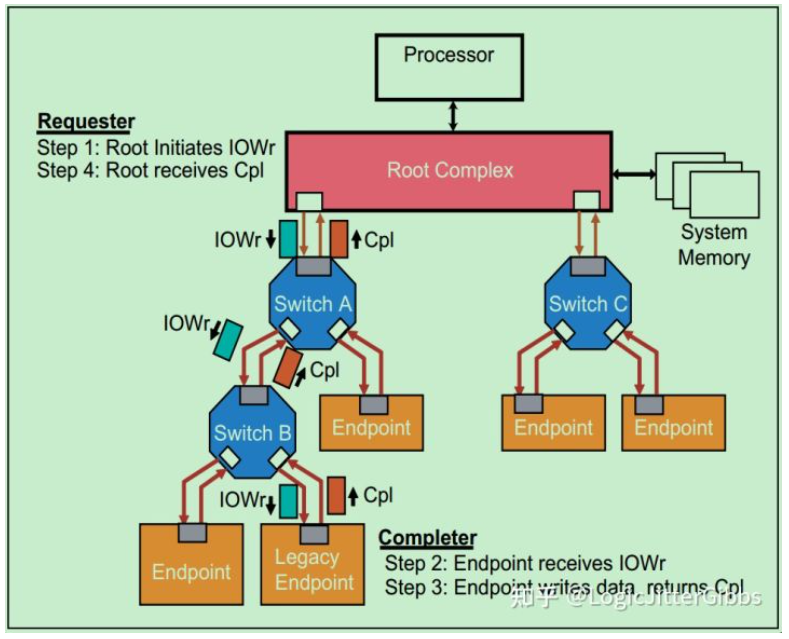

下图是一个Non-Posted IO写操作的例子。和Locked操作一样,IO操作也是为了兼容早期的PCI设备,在PCIe设备中也是不建议使用。

Posted Writes

o Memory Writes

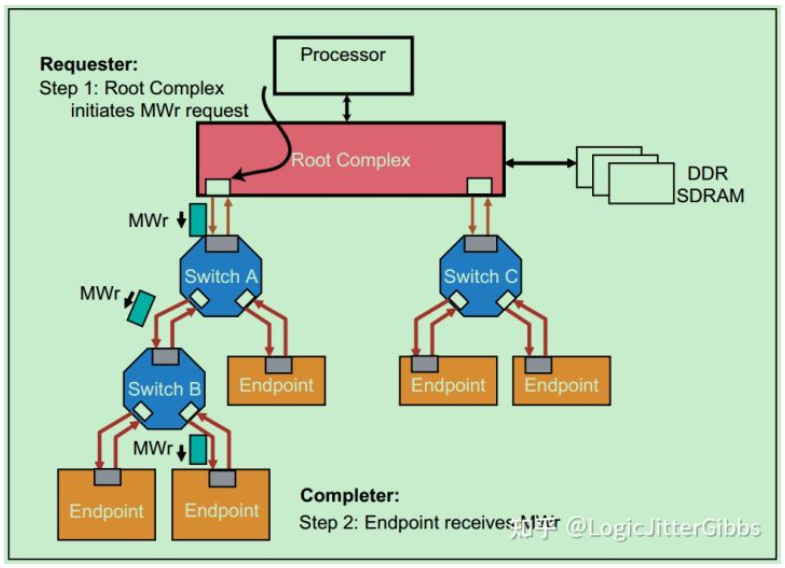

前面的文章有所提及,PCIe中的Memory写操作都是Posted的,因此Requester并不需要来自Completer的Completion。一个简单的Memory Writes例子如下图所示:

因此没有返回Completion,所以当发生错误时,Requester也不会知道。但是,此时Completer会将错误记录到日志(Log),然后向Root发送包含错误信息的Message。

o Message Writes

和其他的几种类型不太一样,Message支持多种Routing方式。比如Requester可以将Message发送至一个指定的Completer,但是不管指定的Completer是不是Root,Root都会自动的收到来自任何一个Endpoint发送的Message。

此外,当Requester是Root的时候,Requester还可以向所有的Endpoint进行广播发送Message。

不得不说,Message机制的提出帮助PCIe总线省去了很多PCI总线中的边带信号。PCI中很多用于中断、功耗管理、错误报告的边带信号,在PCIe中都通过了Message来进行实现了。

PCIe总线事务层入门(三)

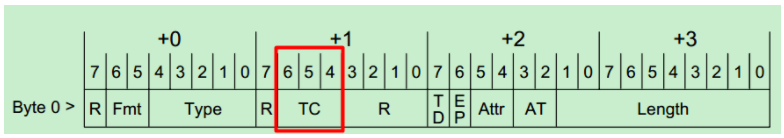

PCIe总线设计之初,充分考虑到了音频和视频传输等这些对时间要求特别敏感的应用。为了保证这些特殊应用的数据包能够得到优先发送,PCIe Spec中为每一个包都分配了一个优先级,通过TLP的Header中的3位(即TC,Traffic Class)。如下图所示:

TC值越大,表示优先级越高,对应的包也就会得到优先发送。

一般来说,支持QoS(Quality of Service)的PCIe总线系统,对于每一个TC值都会有一个独立Virtual Channel(VC)与之对应。这个Virtual Channel实际上就是一个Buffer,用于缓存数据包。

注:当然也有那些只有一个VC Buffer的,此时不管包的TC值如何,都只能缓存在同一个VC Buffer中,自然也就没有办法保证按优先级传输了。这样的PCIe设备称之为不支持QoS的PCIe设备。

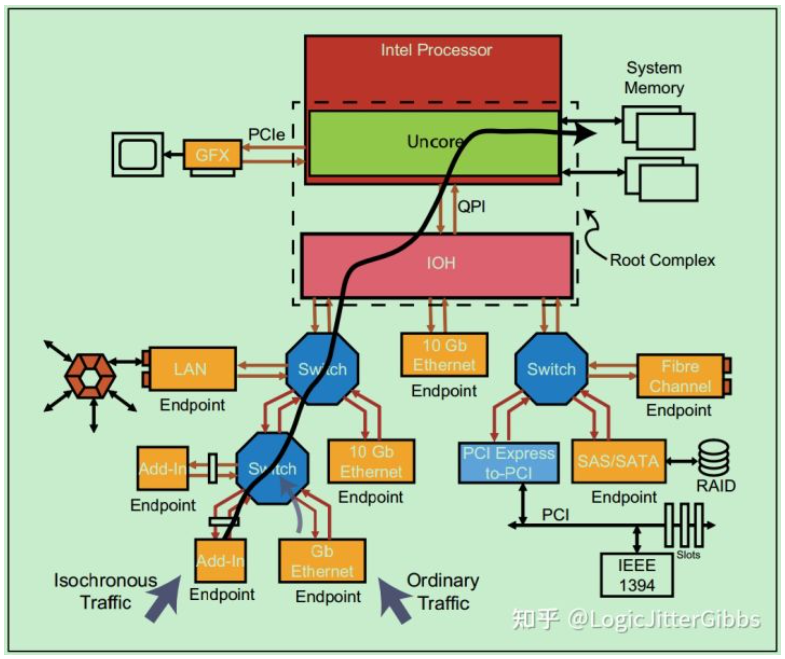

一个简单的QoS的例子如下图所示:

图中左下角的Endpoint(即Isochronous Traffic)的优先级比右边的Endpoint(即Ordinary Traffic)的优先级要高。因此,在Switch中,来自左边的Endpoint的包会得到优先传输。而Switch的这种判决操作叫做端口仲裁(Port Arbitration)。

默认情况下,VC Buffer中的数据包是按照包达到的时间顺序,依次放入VC Buffer中的。但是也并不是总是这样,PCIe总线继承了PCI/PCI-X总线关于Transaction-Ordering和Relaxed-Ordering的架构,但也只是针对相同的TC值才有效。关于Transaction-Ordering和Relaxed-Ordering,大家可以去参考PCI-X的Spec,这里不再详细地介绍。

对于大部分的串行传输协议而言,发送方能够有效地将数据发送至接收方的前提是,接收方有足够的接收Buffer来接收数据。在PCI总线中,发送方在发送前并不知道接收法是否有足够的Buffer来接收数据(即接收方是否就绪),因此经常需要一些Disconnects和Retries的操作,这将会严重地影响到总线的传输效率(性能)。

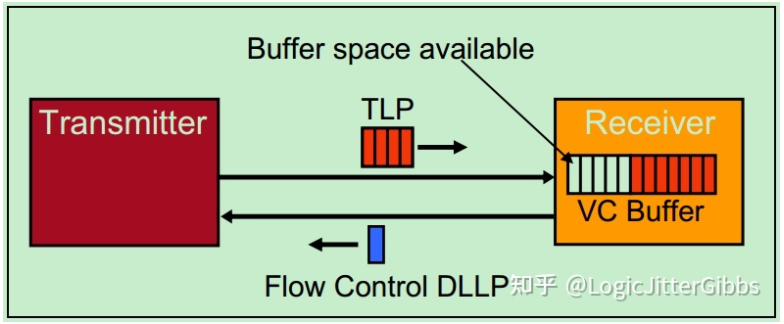

PCIe总线为了解决这一问题,提出了Flow Control的概念,如下图所示。PCIe总线中要求接收方必须经常(在特定时间)向发送方报告其VC Buffer的使用情况。

而报告的方式是,接收方向发送方发送Flow Control的DLLP(数据链路层包),且这种DLLP的收发是由硬件层面上自动完成的,并不需要人为的干预。需要注意的是,虽然这一操作旨在数据链路层之间进行,但是这些VC Buffer的使用情况对于应用层(软件层)也是可见的。

采用Flow Control机制的PCIe总线,相对于PCI总线获得了更高的总线利用率。虽然增加了Flow Control DLLP,但是这些DLLP对带宽的占用极小,几乎对总线利用率没有什么影响。

版权声明

版权声明:本文为 AET 博主「Felix」的原创文章,转载请附上原文出处链接及本声明。

原文链接:http://blog.chinaaet.com/justlxy/p/5100053328

转载自:知乎

作者:Felix

推荐阅读

更多招聘及面经请关注FPGA的逻辑。