使用Verilog可以方便地实现复杂的设计。现在,设计复杂性增加,设计需要针对低功率、高速和最小面积进行优化。

任务和函数在Verilog中用于描述常用的功能行为。与其在不同的地方复制相同的代码,不如根据需求使用函数或任务,这是一种良好且常见的做法。为了便于代码维护,最好使用子例程之类的函数或任务。

从给定字符串中计算1的个数

以下示例描述用于从给定字符串中计算1的个数任务。以下是使用任务时需要记住的要点:

- 任务可以由时间控制语句甚至延迟操作符组成。

- 任务可以有输入和输出声明。

- 任务可以由函数调用组成,但函数不能由任务组成。

- 任务可以有输出参数,在调用时不用于返回值。

- 任务可用于调用其他任务。

- 在编写可综合RTL时,不建议使用任务。

- 任务用于编写行为或可仿真模型。

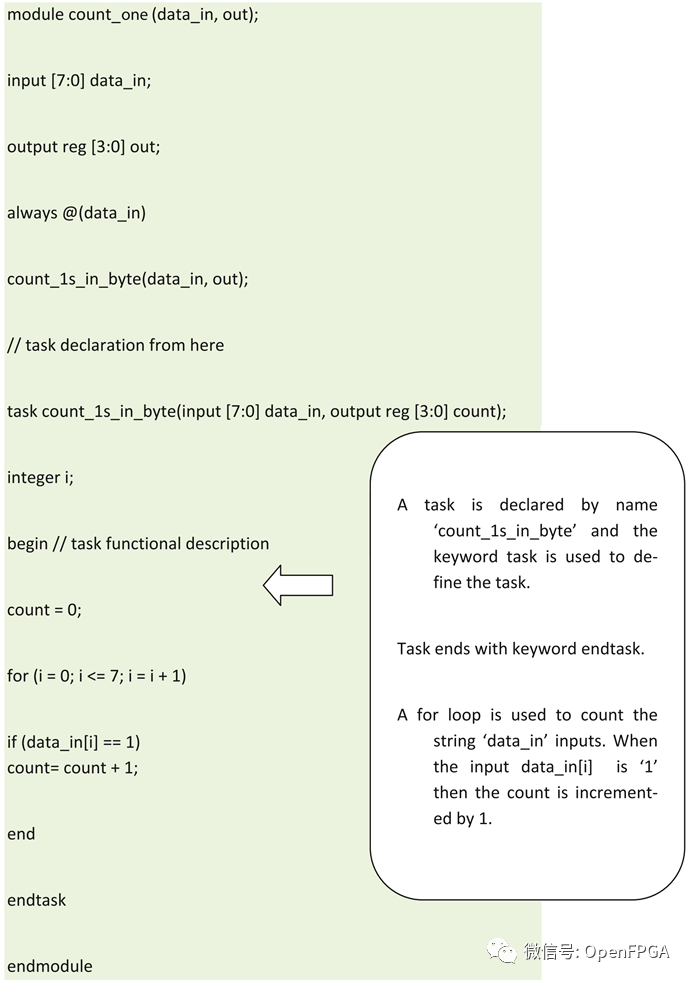

示例7.6是从给定字符串中计算1的个数的说明。在本例中,任务与参数“data_in”、“out”一起使用,任务的名称为“count_1s_in_byte”。在大多数协议描述中,需要对输入字符串执行一些操作。在此示例中,字符串为8位输入“data_in”,输出结果为4位“out”。不建议使用任务生成综合逻辑。

示例7.6任务的Verilog RTL

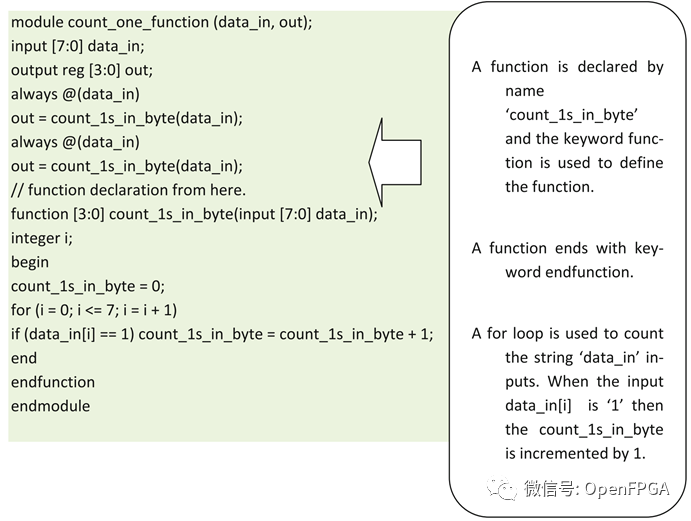

使用函数计数1的个数的模块

以下示例描述用于从给定字符串中计算1的个数函数。以下是使用该功能时需要记住的要点:

- 函数不能由时间控制语句甚至延迟运算符组成。

- 函数至少有一个输入参数声明。

- 函数可以由函数调用组成,但函数不能由任务组成。

- 函数在零模拟时间内执行,并在调用时返回单个值。

- 在编写可综合 RTL时,不建议使用函数。

- 函数用于编写行为或可仿真模型。

- 函数不应具有非阻塞赋值。

示例7.7是从给定字符串中计算1个数的说明。在本例中,函数与参数“data_in”一起使用。函数名为“count_1s_in_byte”。在大多数协议描述中,需要对输入字符串执行一些操作。在此示例中,字符串为8位输入“data_in”,输出结果为4位“out”。不建议使用该函数生成综合逻辑。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。