FPGA中仿真概念

需要对输入Verilog或VHDL的设计进行仿真,以检查设计的功能正确性。对于HDL RTL功能,需要使用不可综合的Verilog结构编写测试台。

阻塞和非阻塞赋值的仿真

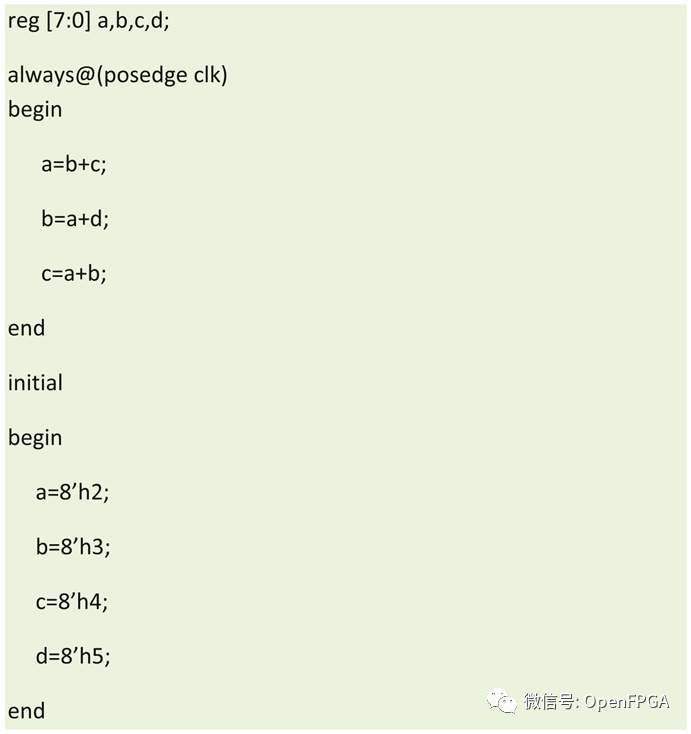

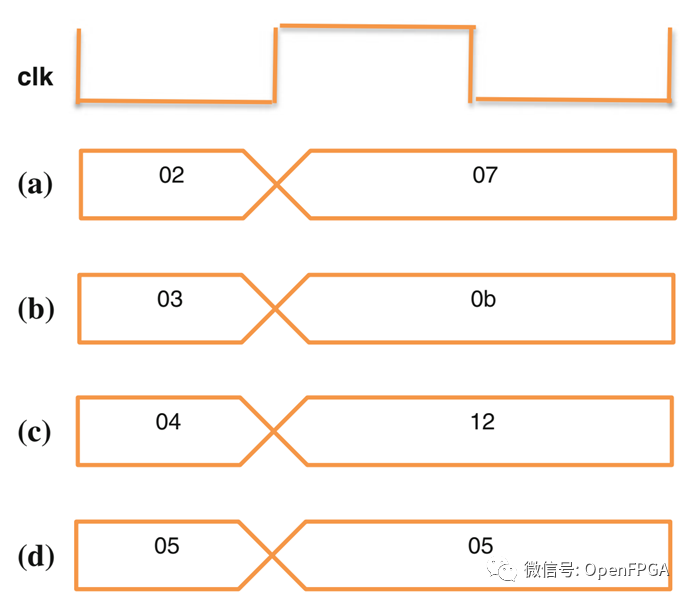

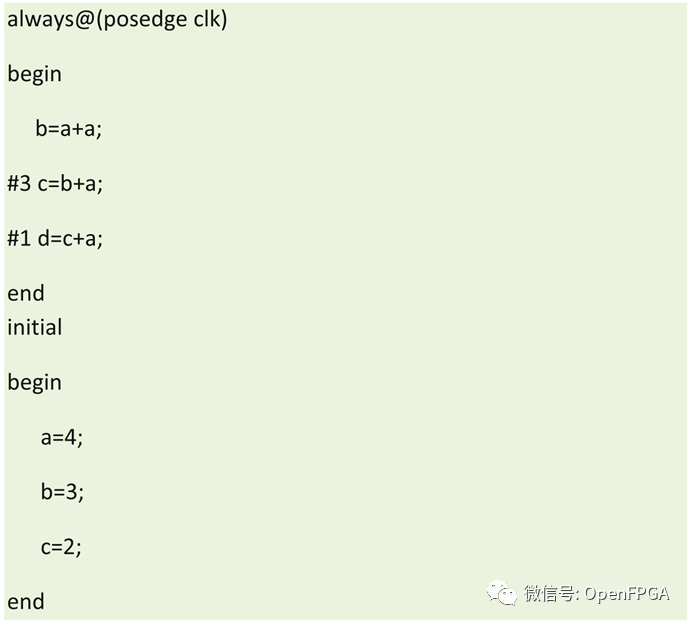

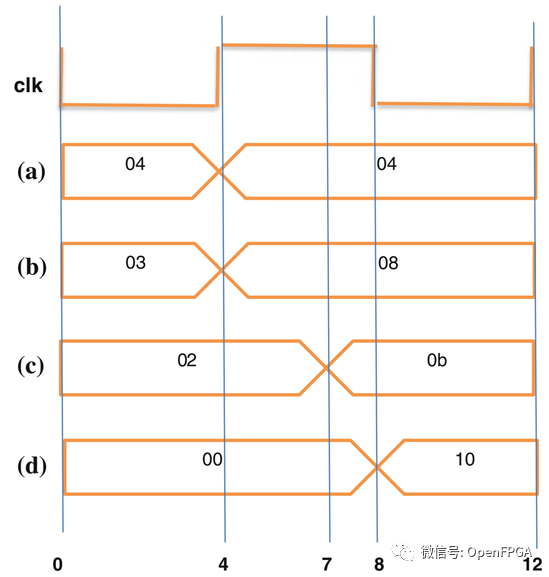

不可综合Verilog RTL由示例9.1中所示的阻塞赋值组成。

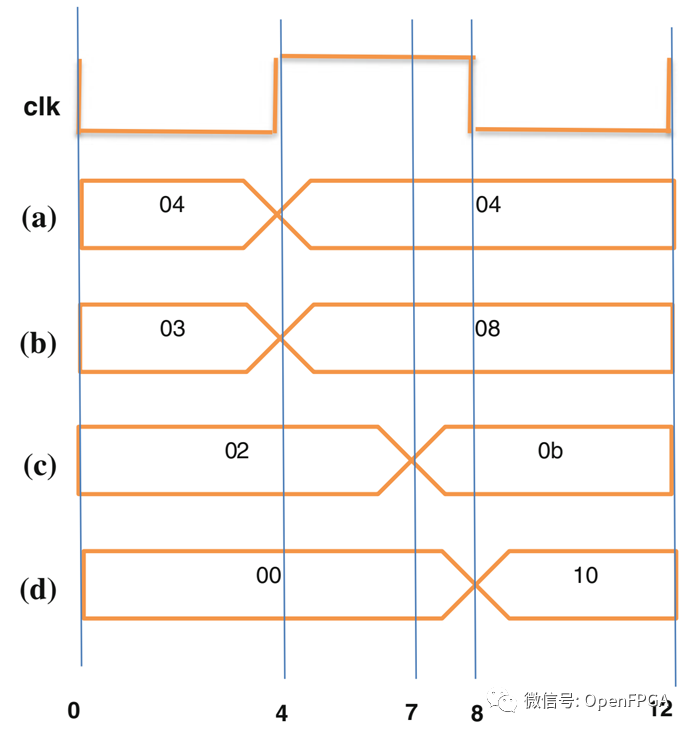

在本例中,程序“always”块每次在时钟“clk”上的事件上执行,“initial”块仅执行一次,用于将值赋值给“a”、“b”、“c”和“d”。非阻塞赋值的仿真结果如波形9.1所示。

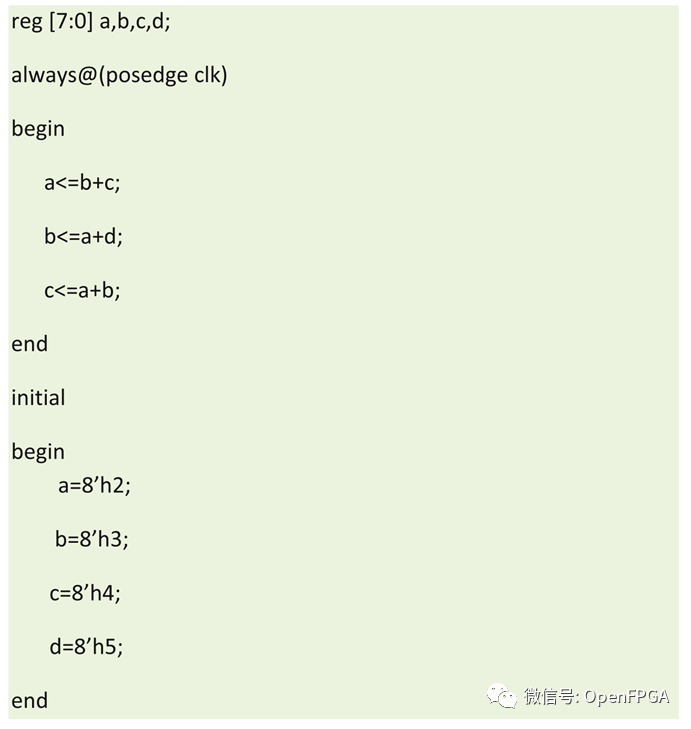

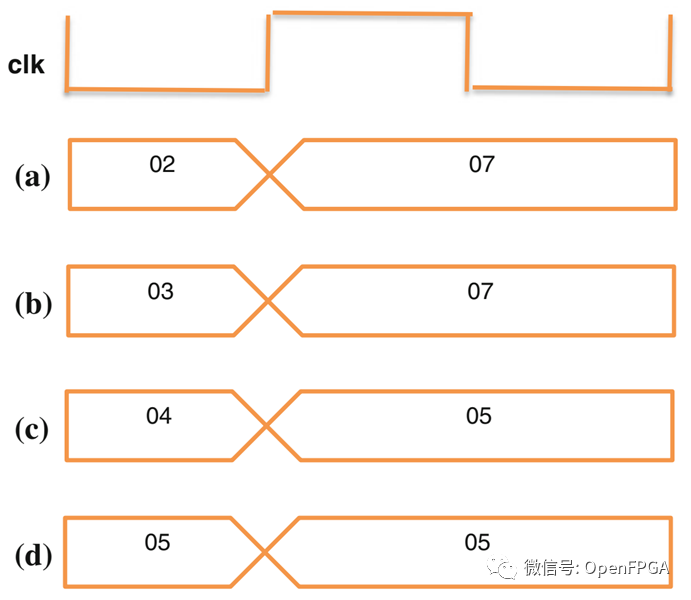

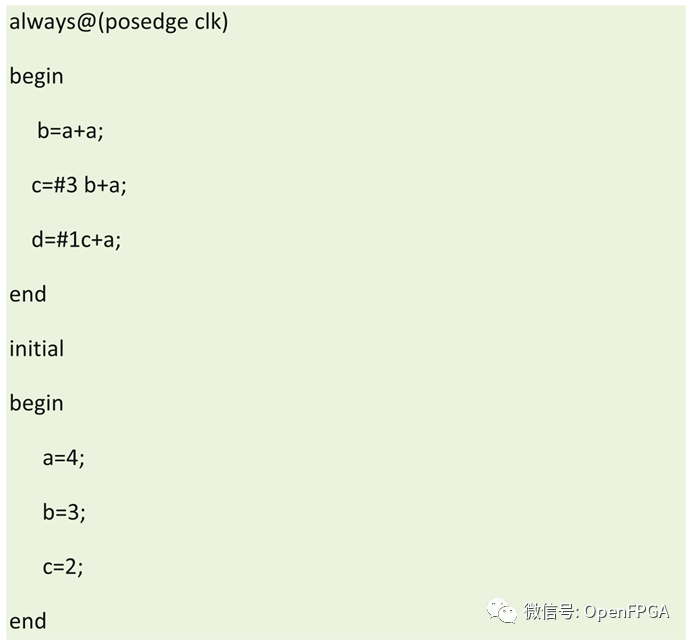

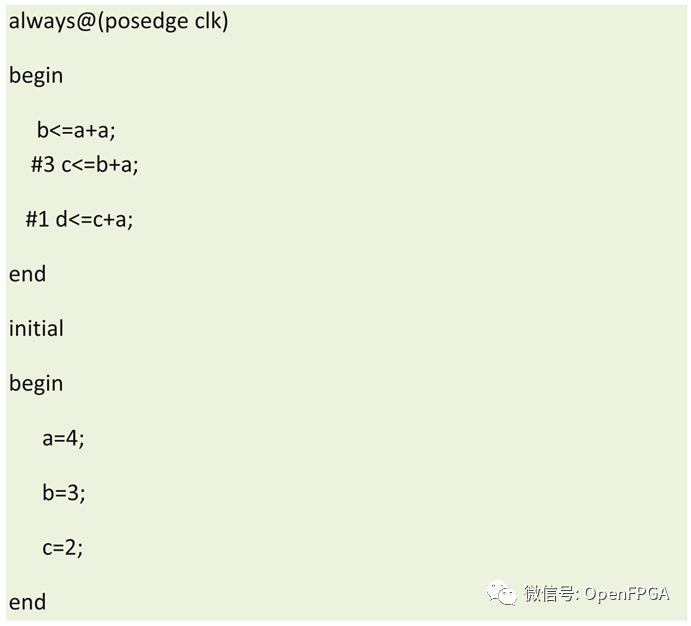

考虑Verilog RTL由示例9.2中所示的非阻塞赋值组成。

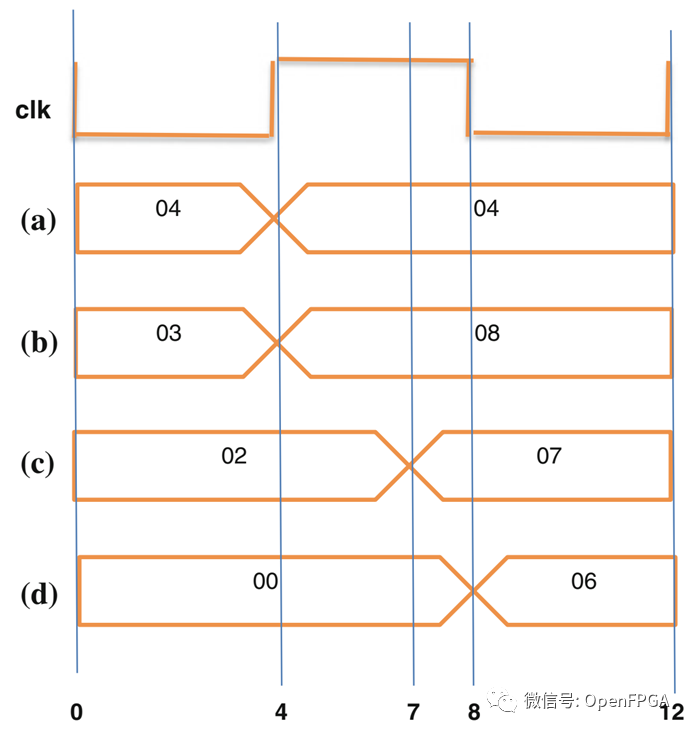

使用非阻塞的上述Verilog代码的仿真结果如波形9.2所示。

示例9.1 Verilog阻塞赋值的仿真

波形9.1 Verilog阻塞赋值的仿真结果

示例9.2 Verilog非阻塞赋值的仿真

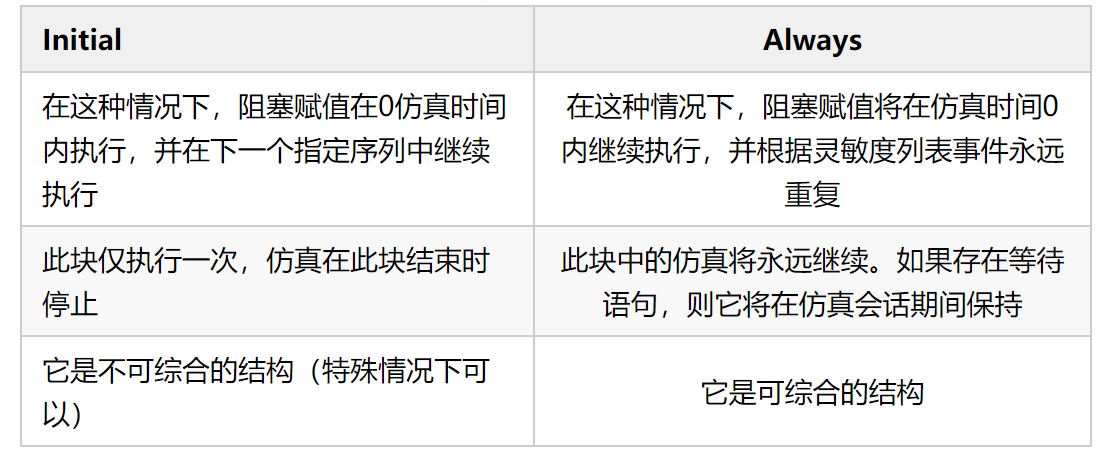

表9.1 always和initial之间的差异

表9.1中描述了always和initial块之间的差异。

具有赋值延迟的阻塞赋值

内部赋值延迟了阻塞赋值,延迟了赋值的评估和赋值的更新。

考虑下面示例9.3中所示的Verilog代码。

波形9.3给出了具有赋值延迟的阻塞赋值的仿真结果。

示例9.3具有赋值延迟的Verilog阻塞赋值

具有内部赋值延迟的阻塞赋值

内部赋值延迟阻塞赋值,延迟赋值的评估,但不延迟赋值的更新。

考虑下面示例9.4中所示的Verilog代码。

波形9.4给出了具有内部赋值延迟的阻塞赋值的仿真结果。

示例9.4具有内部赋值延迟的Verilog阻塞赋值

波形9.4具有内部赋值延迟的Verilog阻塞赋值的仿真结果

具有赋值间延迟的非阻塞赋值

内部赋值延迟和非阻塞赋值延迟赋值的评估和赋值的更新。

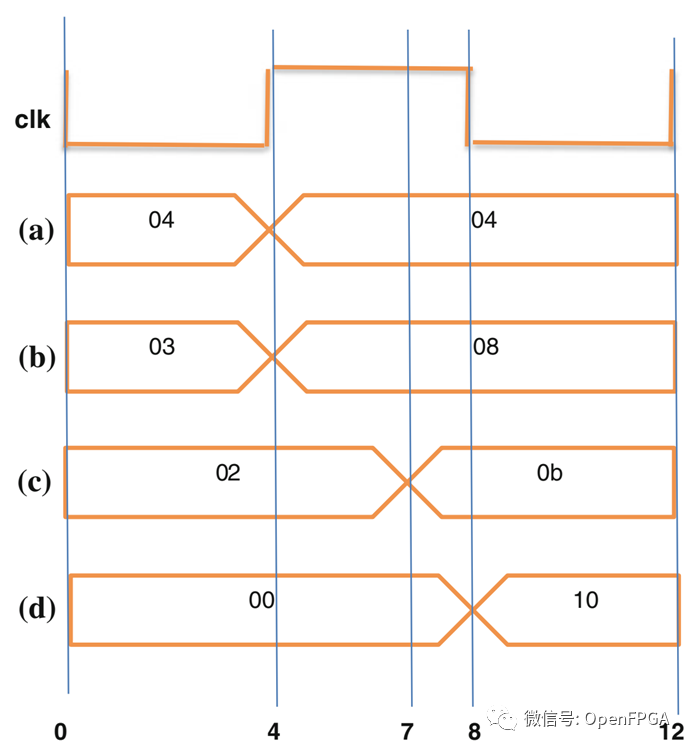

考虑下面示例9.5中所示的Verilog代码。

波形9.5给出了具有赋值间延迟的非阻塞赋值的仿真结果。

示例9.5具有赋值间延迟的Verilog非阻塞赋值

波形9.5具有赋值间延迟的Verilog非阻塞赋值的仿真结果

具有内部赋值延迟的非阻塞赋值

内部赋值延迟阻塞赋值、赋值更新,但不延迟赋值评估。

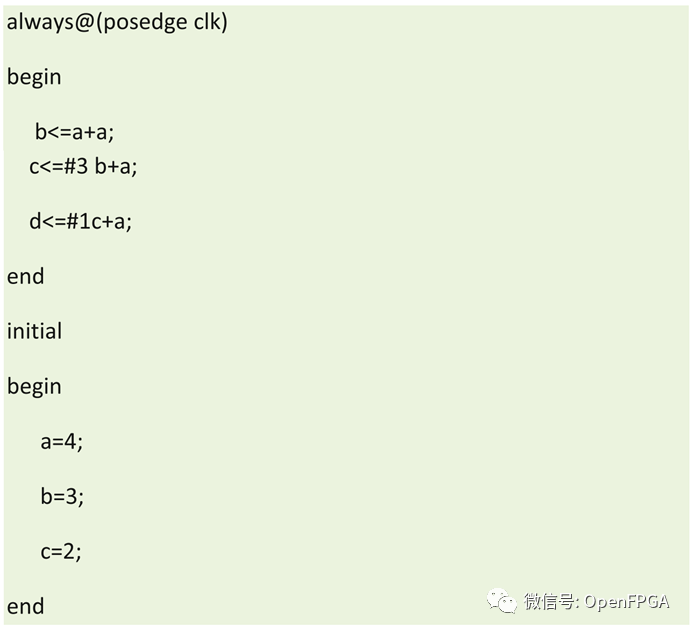

考虑下面示例9.6中所示的Verilog代码。

波形9.6给出了具有内部赋值延迟的阻塞赋值的仿真结果。

示例9.6具有内部赋值延迟的Verilog非阻塞赋值

波形9.6具有内部赋值延迟的Verilog非阻塞赋值的仿真结果

使用Verilog进行仿真

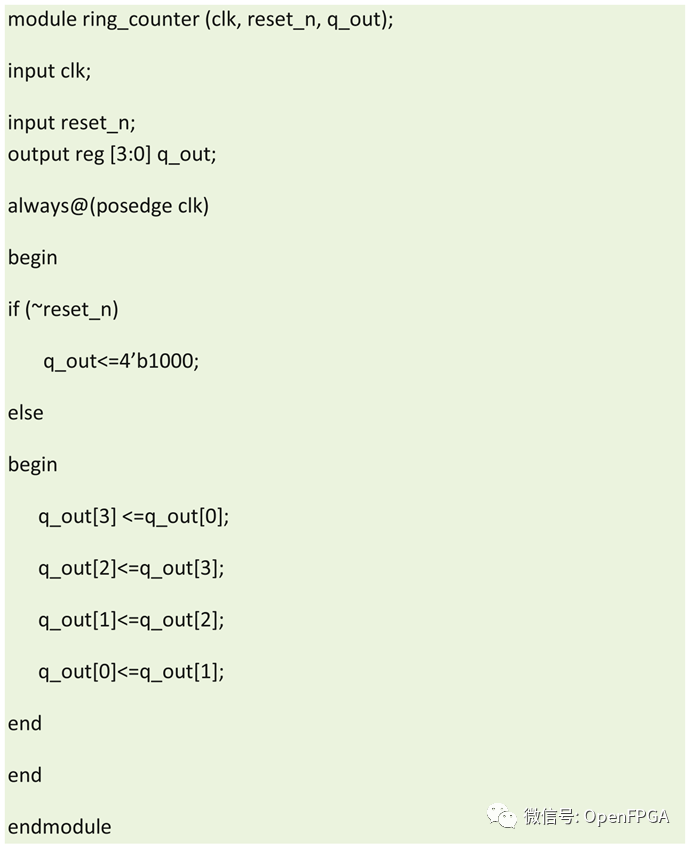

之前,我们讨论了详细设计综合和硬件推断。Verilog HDL对于设计的仿真功能非常强大。通过使用非综合结构,可以验证Verilog验证下设计(DUV),以确定设计的功能正确性。考虑具有输入为“clk”和“reset_n”的环形计数器的简单Verilog设计,并且计数器具有四位输出“q_out [3:0]”,在示例9.7中示出了环形计数器的RTL描述

示例9.7使用Verilog HDL的四位环形计数器

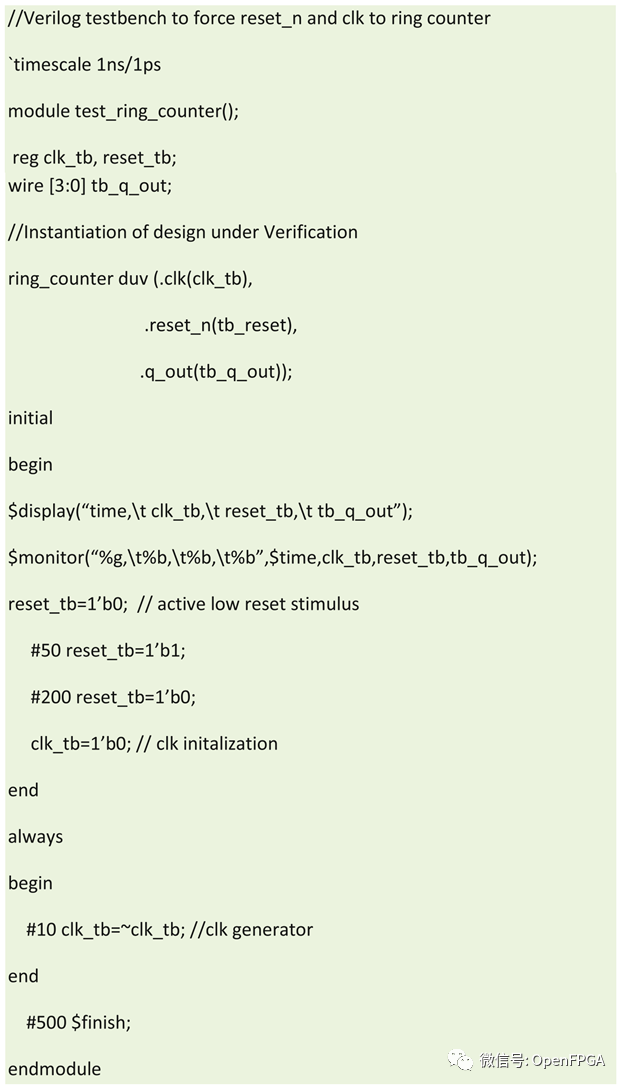

示例9.8描述了环形计数器的testbench,并将激励施加到DUV上。

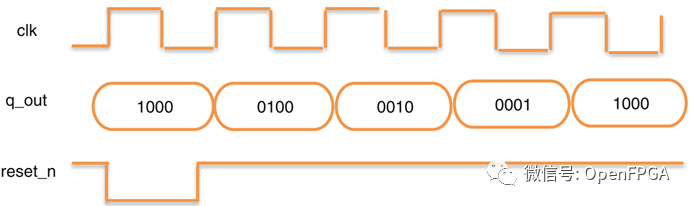

上述testbench产生波形9.7所示的结果。

如上所述,基本仿真可以通过编写testbench来执行,该testbench可以强制激励被测试的设计。对于复杂度较低的FPGA设计,这种方法是可行的。但是对于大型SOC设计模块,使用复杂的自检测试台是必不可少的。验证工程师必须了解测试用例、测试计划和测试向量的创建。即使是最好的行业实践也是通过使用驱动程序、监视器和检查器来使用验证体系结构。此讨论超出了基于FPGA的设计范围。

示例9.8 Verilog环形计数器的testbench

波形9.7环形计数器的仿真结果

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。