绪论

在前两篇专栏文章中介绍到了当前集成电路老化监测、缓和与自适应的手段,其中最主要的就是In-Situ Sensors(原位传感器)方法,通过在目标关键路径中插入原位传感器来实时监测电路参数,而Razor触发器则是原位传感器中时序违例监测的典型代表。

开天辟地之Razor

在2003年和2004年MICRO上发表的两篇文章[1][2]首次提出了Razor Flip-flop这个概念,从此Razor触发器相关的论文开始迅速发展,并且几乎发表在集成电路领域的顶会/顶刊上(例如ISSCC、JSSC、MICRO)。

Motivation

这两篇开山之作的Motivation是为了优化DVS,达到更加激进的效果(more-aggressive power reduction),从而降低芯片的功耗。电路的延迟受到多个因素的影响,其中包含电路老化、温度、电压、工艺等等,DVS能够使芯片的电源电压在适当的时候降低从而减少功耗,但是降低电压带来的负面影响就是电路延迟的上升,电路延迟上升则可能带来电路的时序违例。那么在电路的功耗与正确率之间存在着一个trade-off,在Razor触发器发明之前,芯片的设计阶段为了保证芯片的正确性,预留了较大的时序余量给低功耗模式,电压并没有降低到最优值,造成了不必要的浪费,因此Razor触发器的诞生就是为了压榨每一滴时序余量,将电压降至最低从而达到最低的功耗。

工作原理

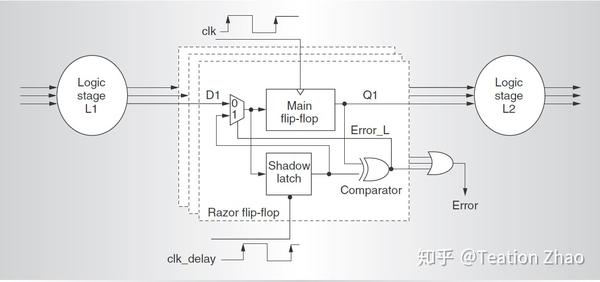

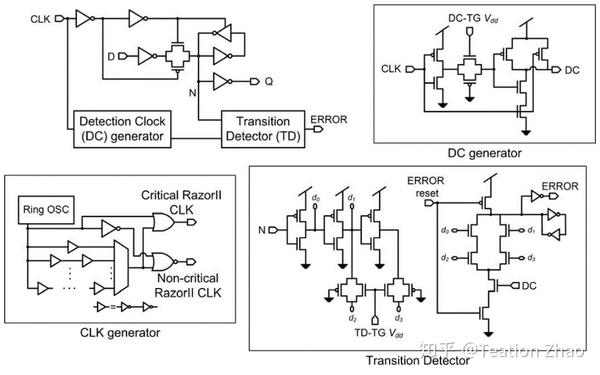

Razor触发器是在标准触发器的基础上增加了一个Shadow latch、时钟延迟、输入MUX以及一个异或门用于错误检测。

Razor Flip-flop

其基本原理是由于Shadow latch的时钟clk\_delay相较于 clk有一定的延迟,因此Shadow latch总能保存正确的D1,而Main flip-flop却可能因为路径延迟过大而采样到错误值,然后通过对比latch与Main触发器的输出是否相同来得到是否时序违例。

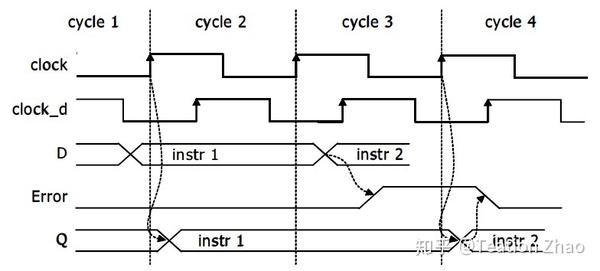

Timing diagram

好处/坏处

Razor触发器作为一个时序违例检测原位传感器,其缺点很清晰:其监测结果是二值的,即时序违例/正常,相对于Ring-Oscillator等路径延迟原位传感器,其监测精度不够。相对的,好处也明显,Razor触发器以牺牲监测精度来换取了更低的面积开销,更少地对原电路的侵入。

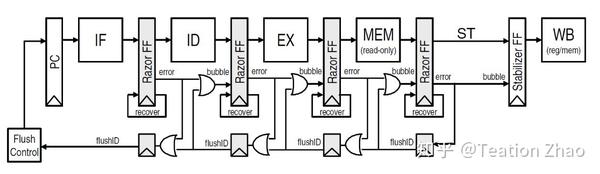

另外,Razor另一个更大的优势在于其Shadow latch总是能够存储正确的值,因此Razor触发器具有EDAC(error detection and correction)功能,其中的EC(Error Correct)是其他原位传感器没有具备的。在流水线中,如果某一级的Razor触发器得到错误,那么Main触发器会在下一个周期将Shadow latch中的正确的值重新读进去,因此不需要flush整个流水线,只需要在流水线中插入一个bubble就可以将错误的那一个数据滤过。

在流水线中插入Bubble以实现纠错

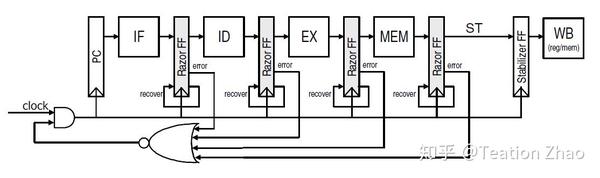

或者如果流水线具有clock gate,那么只需要在发生错误时将clock gate住一个周期,那么正确的结果就能重新从Shadow latch中读出,错误结果就不会随着流水线流下去。

对流水线进行clock gating以实现纠错

猴子猴孙之Razor

随着Razor开天辟地后,各种Razor的改进版本从此遍地开花,其中还是以美国密歇根大学为主。

2008年密歇根、AMD和ARM在JSSC上发表了Razor II[3],他们发现在首次出现错误(The point of first failure,PoFF)的电源电压下,错误率非常低,几乎10 million cycle才发生1个错误,即使随着电压降低错误率呈指数上升。那么由于PoFF的极低错误率,Razor触发器中的EC(Error Correct)功能就成为了累赘,因此Razor II阉割了EC功能,只保留了ED(Error Detect)功能,从而进一步降低面积开销和功耗开销,而EC功能则交给架构级的冗余备份去解决。

Razor II

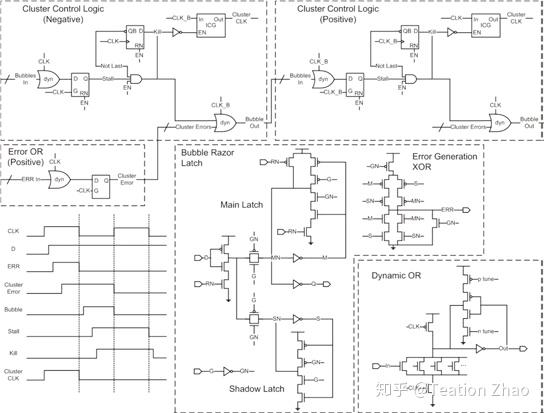

2012年以密歇根主导的一篇ISSCC论文上面介绍了Bubble Razor[4],由于之前的Razor触发器任然对原电路架构具有一定的侵入性,从而导致了没有商业处理器使用,因此他们提出了新的两级latch触发器结构,并且具有local的冗余备份,从而实现了在Cortex-M3处理器的网表代码基础上仅仅通过脚本实现B-Razor触发器的implementation。

Bubble Razor

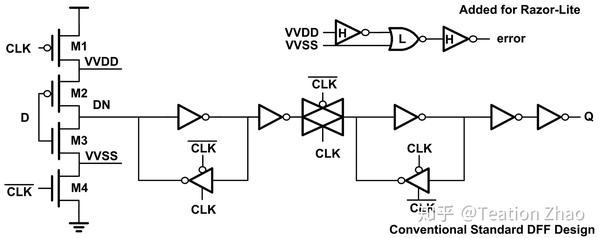

2014年任然以密歇根主导的一篇JSSC论文介绍了Razor-Lite[5],其保留了Razor I的EDAC功能,同时将晶体管数量压缩到了仅仅比正常触发器多8个,从而减低功耗/面积开销。

Razor-Lite

真假美猴王之Razor

除了主流的Razor系列触发器之外,基于时序错误检测的原位老化传感器还有很多,但大都和Razor触发器有着相似的结构,例如:

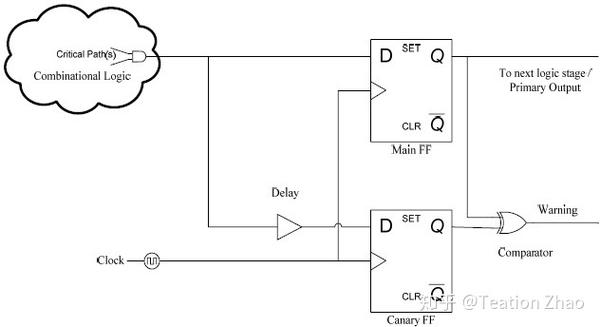

使用Canary Flip-flop替代Shadow latch,使用Delay element代替Delay clk的论文[6]。

Canary Flip-flop

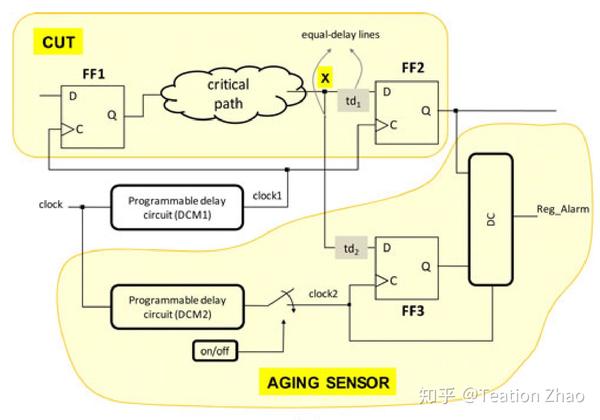

同样使用delay clock但是使用触发器代替shadow latch的用于FPGA老化监测的传感器[7]。

面向FPGA的老化传感器

总结

以Razor触发器为代表的时序违例检测原位传感器因具有较低的面积开销,对原电路架构较低的侵入性能够使其通过脚本实现快速替换,从而被较为广泛的采用。但是其监测精度不够,无法对电路的真实延迟、工作负载等等变量进行监测,作为一种典型的监测类传感器,只能对电路老化结果进行监测,而无法为电路老化预测提供任何有效信息,进而无法为后续更加全面的老化监测、缓和与自适应提供基础,逐渐被替代。

参考

- ^D. Ernst et al., "Razor: a low-power pipeline based on circuit-level timing speculation," Proceedings. 36th Annual IEEE/ACM International Symposium on Microarchitecture, 2003. MICRO-36., San Diego, CA, USA, 2003, pp. 7-18.

- ^D. Ernst et al., "Razor: circuit-level correction of timing errors for low-power operation," in IEEE Micro, vol. 24, no. 6, pp. 10-20, Nov.-Dec. 2004.

- ^S. Das et al., "RazorII: In Situ Error Detection and Correction for PVT and SER Tolerance," in IEEE Journal of Solid-State Circuits, vol. 44, no. 1, pp. 32-48, Jan. 2009.

- ^M. Fojtik et al., "Bubble Razor: An architecture-independent approach to timing-error detection and correction," 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, 2012, pp. 488-490.

- ^I. Kwon, S. Kim, D. Fick, M. Kim, Y. Chen and D. Sylvester, "Razor-Lite: A Light-Weight Register for Error Detection by Observing Virtual Supply Rails," in IEEE Journal of Solid-State Circuits, vol. 49, no. 9, pp. 2054-2066, Sept. 2014.

- ^N. Shah, R. Samanta, M. Zhang, J. Hu and D. Walker, "Built-In Proactive Tuning System for Circuit Aging Resilience," 2008 IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems, Boston, MA, 2008, pp. 96-104.

- ^M. D. Valdes-Peña et al., "Design and Validation of Configurable Online Aging Sensors in Nanometer-Scale FPGAs," in IEEE Transactions on Nanotechnology, vol. 12, no. 4, pp. 508-517, July 2013.

END

知乎:https://zhuanlan.zhihu.com/p/115637239

推荐阅读

更多内容请关注其实我是老莫的网络书场专栏