环形振荡器

当一个单输入单输出的组合逻辑,满足输出与输入反相时,将输出与输入短接后便形成了一个环形振荡器,能够在没有外部时钟驱动的条件下自振荡,振荡频率一个重要的特性就是与电路延迟有关。因此针对其震荡频率进行测量,再对PVT进行修正,就能得到一个归一化的电路延迟信息,那么这个延迟信息就能作为电路老化表征的直接体现,这一特性使得环形振荡器广泛地应用与集成电路可靠性的研究:老化特征的仿真,原位传感器以及金丝雀电路。

环形振荡器震荡频率与电路延迟

这里借用论文[1]里面的表述。

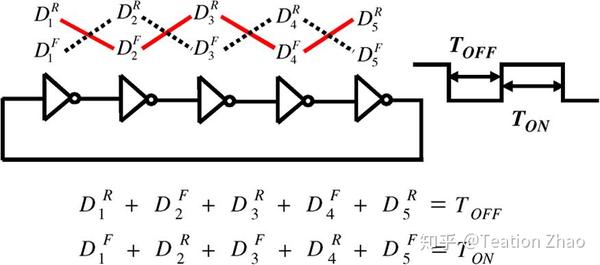

图1 环形振荡器震荡周期

这篇论文主要是为了研究Rise/Fall Gate Delay的测量,将震荡周期拆分为 与 ,这两个都是由各个反相器的Rise/Fall Gate Delay构成,那么只要测出震荡输出的占空比,就能够将延迟中的Rise/Fall Delay进行区分。

但是,在研究电路老化特征时,主要关心的是用电路延迟的变化来表征或预测电路的老化状态,因此不再需要对Rise/Fall Delay进行区分,只关心电路的整体延迟变化,因此将它们做近似相等的处理,这在一些论文中也有所体现[2]。这样进行简化过后,就能得到如下的关系:

这样就得到了震荡频率与电路延迟的关系。

环形振荡器震荡频率与电路老化

在前面的专栏文章中提到了,电路老化主要是造成MOS的阈值电压退化,阈值电压退化就能够表现为电路延迟的退化,通过测量环形振荡器的震荡频率,就能一步一步推回到电路的老化上。

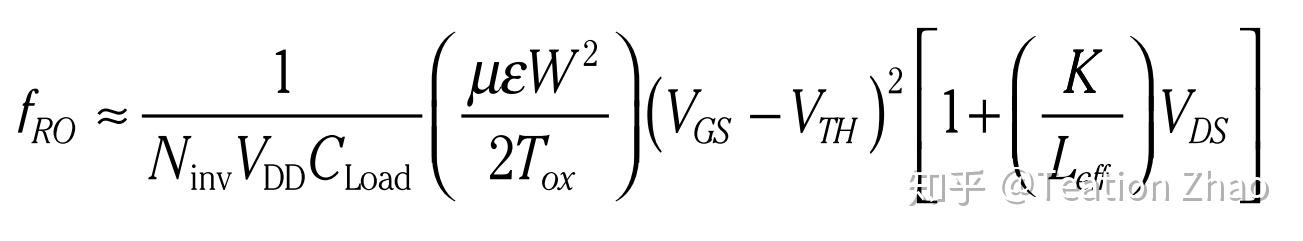

当然,也可以不使用电路延迟为中间桥梁,阈值电压的退化也可以直接表达为环形振荡器的震荡频率的退化,例如论文[3]中:

图2 震荡频率与阈值电压

用于老化仿真的环形振荡器

由于环形振荡器的震荡频率可以作为电路老化的特征,环形振荡器最广泛的使用则是对电路各个老化模型的仿真分析中,在专栏文章集成电路的老化效应中几乎每一篇论文都对环形震荡器模型进行了仿真。

作为备份电路/金丝雀电路的环形振荡器

这其中最典型莫过于这[4][5]两篇论文,作为备份电路的环形振荡器,它的好处是测试精度较高,能够相对准确地对电路延迟信息进行测量。但是它也具有所有备份电路的通病,由于PVT的影响,备份电路的老化并不等同于原电路/主电路的老化,就算能够精确地得出备份电路的老化状态,但是由于备份电路与原电路之间的桥梁被PVT打断,那么监测数据也变得毫无意义。

作为原位传感器的环形振荡器

将环形振荡器的高测试精度融入原位传感器中是部分就能大放异彩呢?是也不是。

在文章开头提到,构成环形振荡器只需要组合逻辑的输入输出反相,并不需要完全是一个反相器链。因此对于电路中的组合逻辑,将关键路径隔离出来后,通过插入一个反相器来保证输入输出反相就能实现这样一个环形振荡器,在这个环形振荡器中,每一级逻辑门都是由关键路径上的逻辑门构成,这个环形振荡器所代表的电路延迟也一定是关键路径真实的电路延迟。

所以,这里的关键问题是如何实现关键路径的隔离。在复杂电路中,关键路径通常会横跨多个模块,隔离出这条关键路径就必须对关键路径上的其他所有输入进行约束,这通常是非常困难的。

论文[6][7][8]使用的就是最基本的方法,直接隔离出关键路径,将其他所有输入信号约束到一个常数值上。

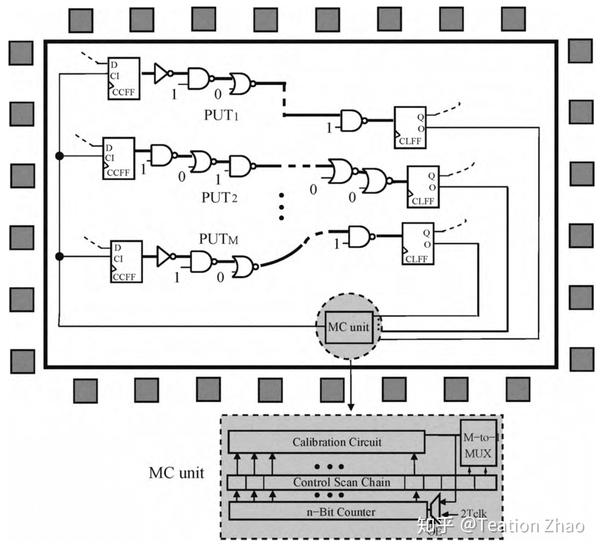

图3 环形振荡器用于原位传感器的一个方法

但是,这种方法虽然能够将测试精度最大化,但是也带来了最大侵入性,这里的侵入性可以和专栏文章In-Situ Sensors: Razor Flip-flop中的Razor Flip-flop做对比。一个包含有关键路径的组合逻辑模块,其时序通常也是最紧张的模块,要将这样一条关键路径隔离出来,就需要在路径的其他每个输入上插入一个与/或门实现测试约束,这样一来电路的布局布线将会受到非常大的影响,并且其工作量也非常巨大。

论文[9]中使用了另一种方法:将这个组合逻辑电路模块隔离,再通过对模块的输入进行约束,保证测试状态下只有关键路径被激活,以形成环形振荡器。

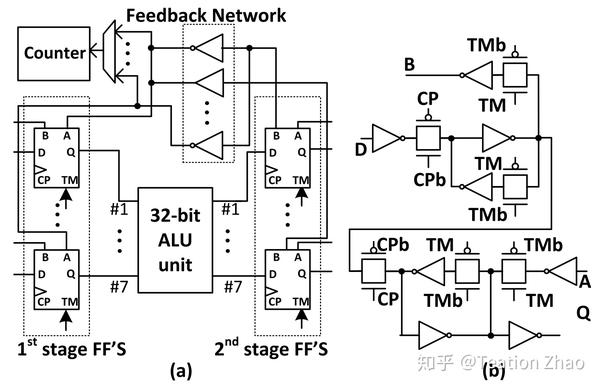

图4 环形振荡器用于原位传感器的另一种方法

这种方法看似解决了上一种方法造成的侵入性问题,用这种整个模块隔离的方法不会对模块本身的时序或者布局布线造成影响,并且通过特定的D触发器也对输入约束逻辑进行了优化。但是,真实的电路中,这种看似完美的模块并不大量存在,一个模块内通常既有时序逻辑也有组合逻辑,在这种情况下,直接隔离整个模块的方法就失效。想要继续使用这种方法,就需要对整个模块进行重新封装,将包含关键路径的组合逻辑全部封装到一个组合逻辑模块中去,这也是非常困难的。

结论

环形振荡器最大的特点是能够高精度地测量电路延迟进而对电路老化进行表征。其用于电路中老化监测的道路其实已经走到了死胡同,作为备份电路本身的问题以及作为原位传感器对原电路极大的侵入性问题。但是环形振荡器任然是老化模型仿真时的必备手段。

参考

- ^B. P. Das and H. Onodera, "On-Chip Measurement of Rise/Fall Gate Delay Using Reconfigurable Ring Oscillator," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 61, no. 3, pp. 183-187, March 2014.

- ^T. Nigam, "Impact of Transistor Level degradation on product reliability," 2009 IEEE Custom Integrated Circuits Conference, Rome, 2009, pp. 431-438.

- ^M. Nourani and A. Radhakrishnan, "Testing On-Die Process Variation in Nanometer VLSI," in IEEE Design & Test of Computers, vol. 23, no. 6, pp. 438-451, June 2006.

- ^J. Keane, D. Persaud and C. H. Kim, "An all-in-one silicon Odometer for separately monitoring HCI, BTI, and TDDB," 2009 Symposium on VLSI Circuits, Kyoto, Japan, 2009, pp. 108-109.

- ^Keane, John P., et al. "Process and reliability sensors for nanoscale cmos." IEEE Design & Test of Computers 29.5 (2012): 8-17.

- ^X. Wang, M. Tehranipoor and R. Datta, "Path-RO: A novel on-chip critical path delay measurement under process variations," 2008 IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, 2008, pp. 640-646.

- ^X. Wang, M. Tehranipoor and R. Datta, "A novel architecture for on-chip path delay measurement," 2009 International Test Conference, Austin, TX, 2009, pp. 1-10.

- ^X. Wang, M. Tehranipoor, S. George, D. Tran and L. Winemberg, "Design and Analysis of a Delay Sensor Applicable to Process/Environmental Variations and Aging Measurements," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 20, no. 8, pp. 1405-1418, Aug. 2012.

- ^J. Li and M. Seok, "Robust and in-situ self-testing technique for monitoring device aging effects in pipeline circuits," 2014 51st ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, 2014, pp. 1-6.

END

知乎:https://zhuanlan.zhihu.com/p/129701086

推荐阅读

更多内容请关注其实我是老莫的网络书场专栏