Q:前有Optane DIMM,后有CXL Memory,内存层级更多了怎么用好?

目录

-CXL设备类型

-三星CXL Type 3内存

-CXL内存池化

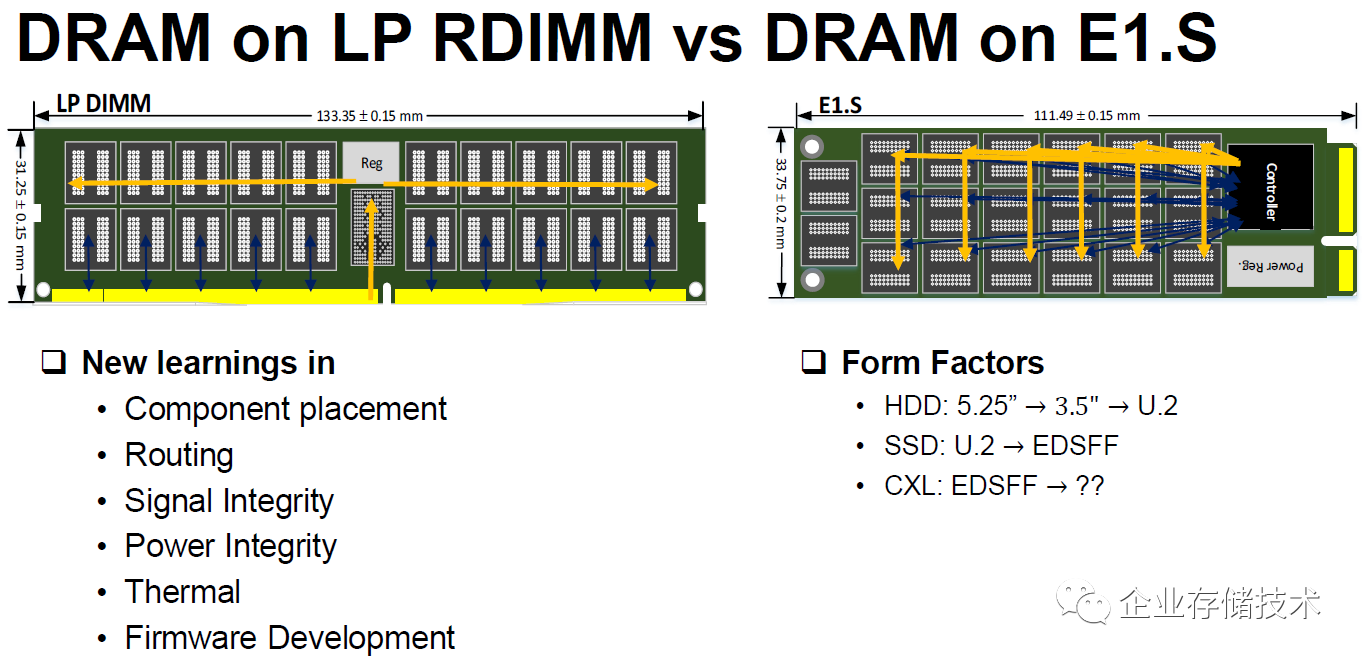

-尺寸:LP RDIMM vs. E1.S上的DRAM内存

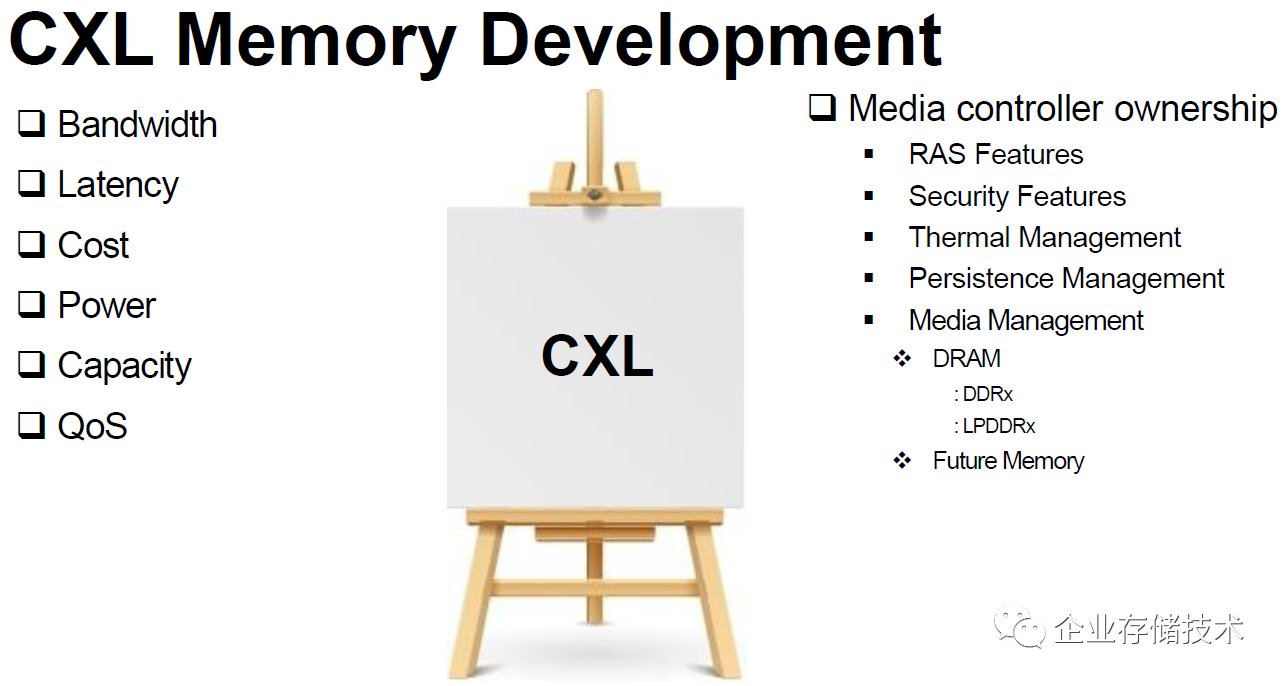

-CXL发展

-SMDK (Scalable Memory Development Kit)

-结论

扩展阅读:《CXL、GenZ、CCIX架构以及未来的PM、内存和SSD形态》

《AMD EPYC Genoa‘7004’:若DDR5换OMI,CXL.mem服务器内存池化》

本文参考自OCP HPC会议资料《Samsung CXL Update》。

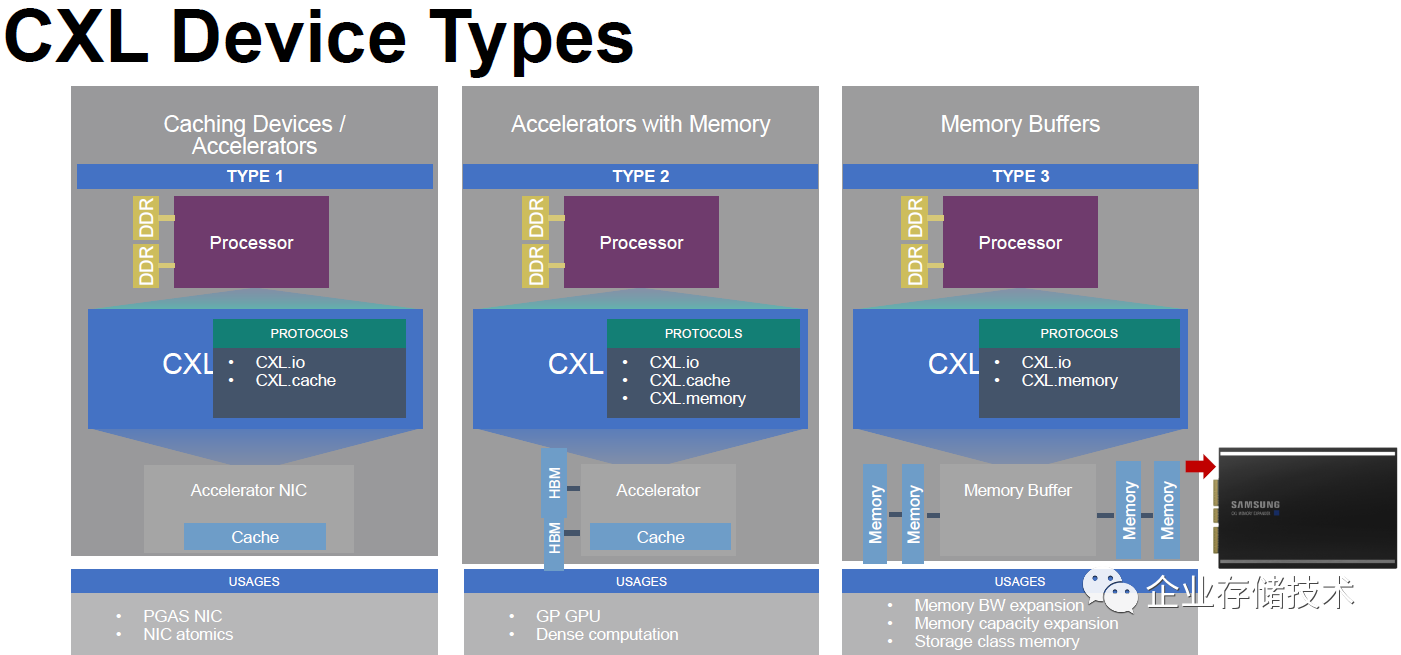

如上图,我在以前的文章中曾介绍过CLX设备的3种类型:

- Type 1- Caching Device / Accelerators__:加速器上的缓存,比如智能网卡、计算型存储器;

- Type 2 - Accelerators with Memory:带有内存的加速器,比如GPGPU、深度学习计算卡;

- Type 3 - Memory Bufffer:用于内存带宽、容量扩展,以及连接存储级内存(SCM)。

三星的CXL内存就属于Type 3。我之前看到的样品图片都是上面这样E3.S尺寸的,尺寸较小的E1.S和加大的E3.L应该也在规划中。

扩展阅读:《数据中心NVMe SSD__和EDSFF__前瞻:来自Intel__、HPE__、Dell & SNIA__等》

三星CXL DDR5内存,从起步容量点128GB来看,定位市场与Intel未来的CXL接口Optane持久内存多少会有竞争吧?当然它们的性能和价格水平也不一样。

三星写的目标应用是HPC和AI工作负载,这类应用的计算数据集往往比较大,容易有大内存、内存池化的需求。而从下文中会介绍的Demo来看,内存数据库等应该也是目标领域。

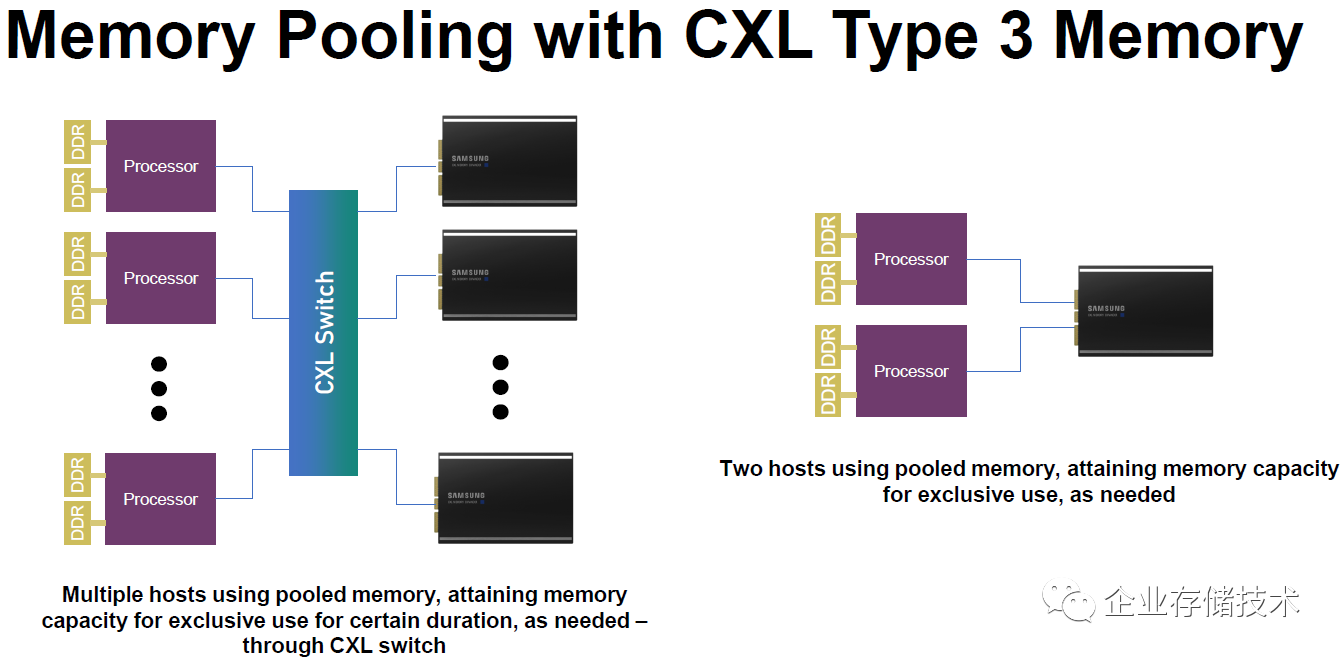

关于双端口这一点,EDSFF模块的连接器最初为PCIe定义,起步就支持2个PCIe x4 lane,CXL上面的协议不同但物理层也借用过来了。双端口意味着CXL内存可以同时连接多个主机,或者连接到多个CXL Switch以实现多路径?但从下面一张图就能看出,这个与SCSI、NVMe的双端口有明显区别。

无论是CXL内存连接2个Host、还是经过CXL交换机的多CXL内存+多主机内存池化,在内存容量的划分上都是排他的原则。这一点与SSD块存储设备支持共享访问是不一样的。

从上图基本可以确定三星也在做E1.S的CXL内存吧。CXL比普通DDR5 RDIMM成本要高,因为多一颗CXL接口的内存控制器芯片。这多少有点以前PCI(PCIe)接口内存控制器的感觉,当然三星的集成度和功耗应该做的还不错。

我以前在写CXL时曾经提到“350ns缓存一致性协议”,CXL初期的带宽、延时性能还是受限于PCIe 5.0。CXL内存的硬件核心技术主要在这颗Media Controller芯片上,我理解对于另外几家主要的DRAM内存供应商来说,倒是没有很高的技术门槛。而软件生态也很重要——三星就搞了个SMDK。

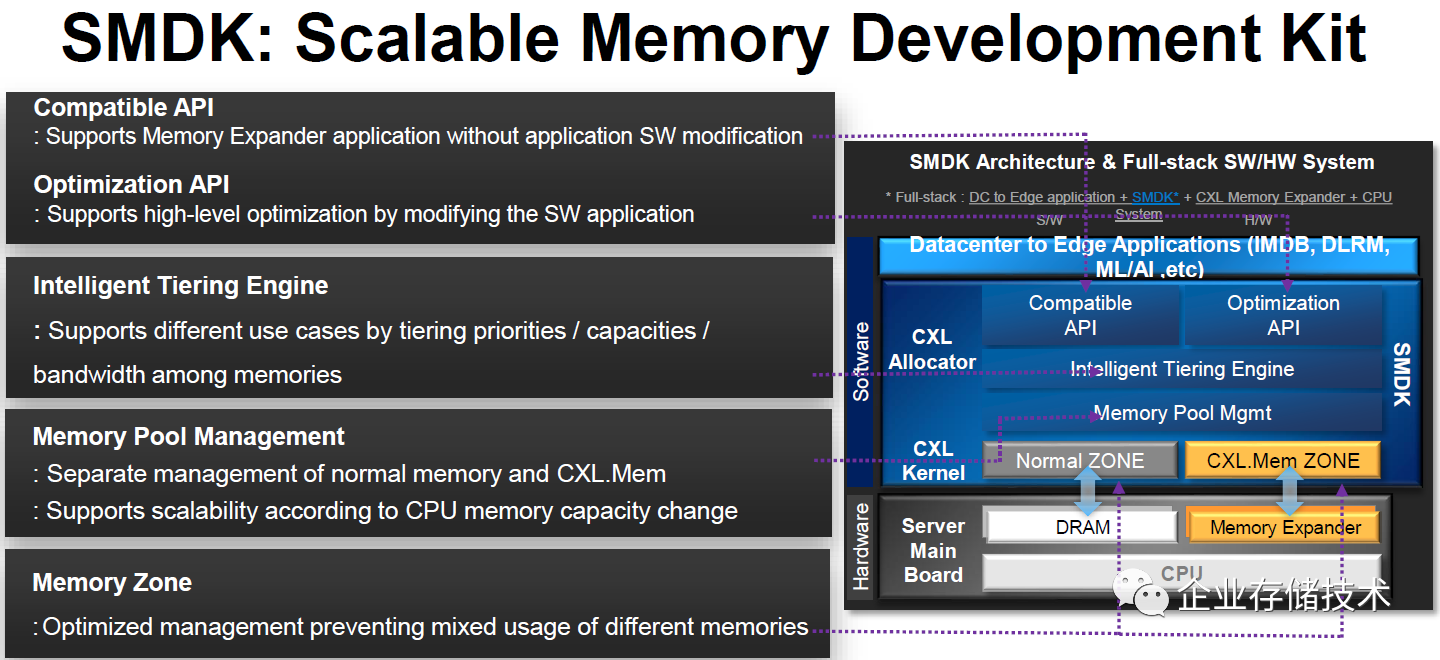

SMDK(Scalable Memory Development Kit)主要实现CXL Kernel和内存分配器,具体模块包括兼容API、优化API、智能分层引擎、内存池管理、Memory Zone分区等。

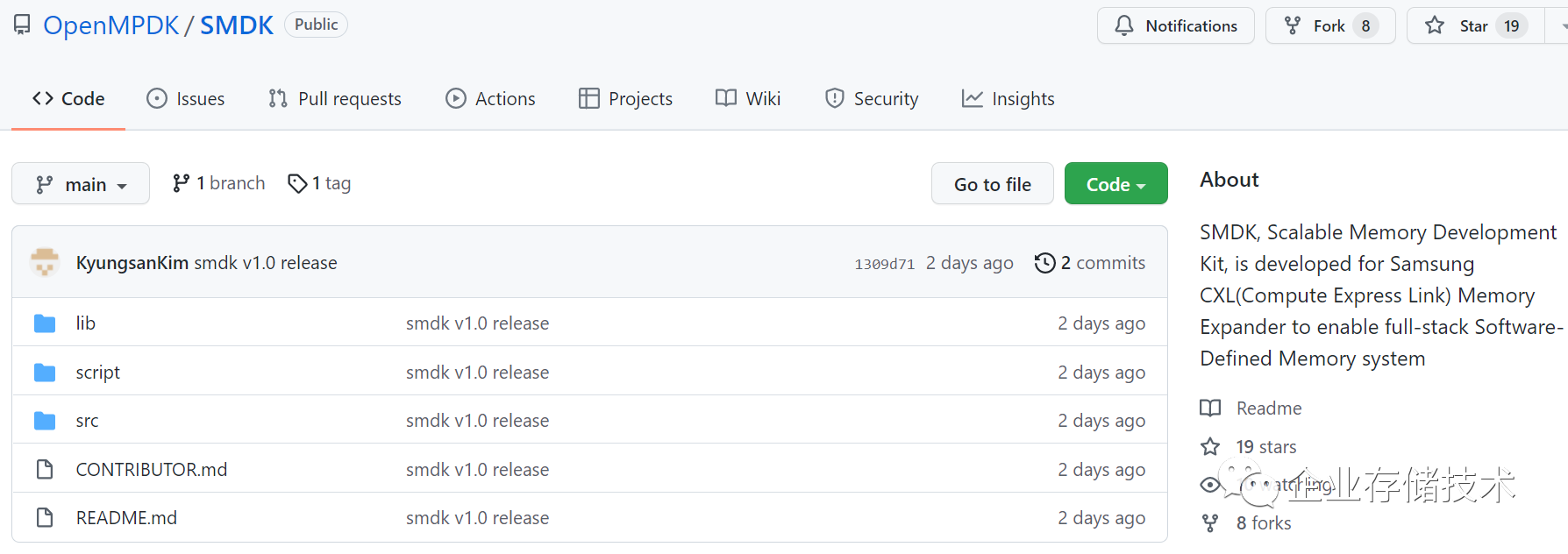

除了三星官网之外,我也看到国内网站发过SMDK的新闻《全面开源:三星电子推出CXL可扩展内存开发套件》

上图就截自SMDK的开源网址https://github.com/OpenMPDK/SMDK。提到做生态,三星比Intel还是显得单薄些,我倒是希望更多大厂一起参与到CXL内存和SMDK的贡献中来。

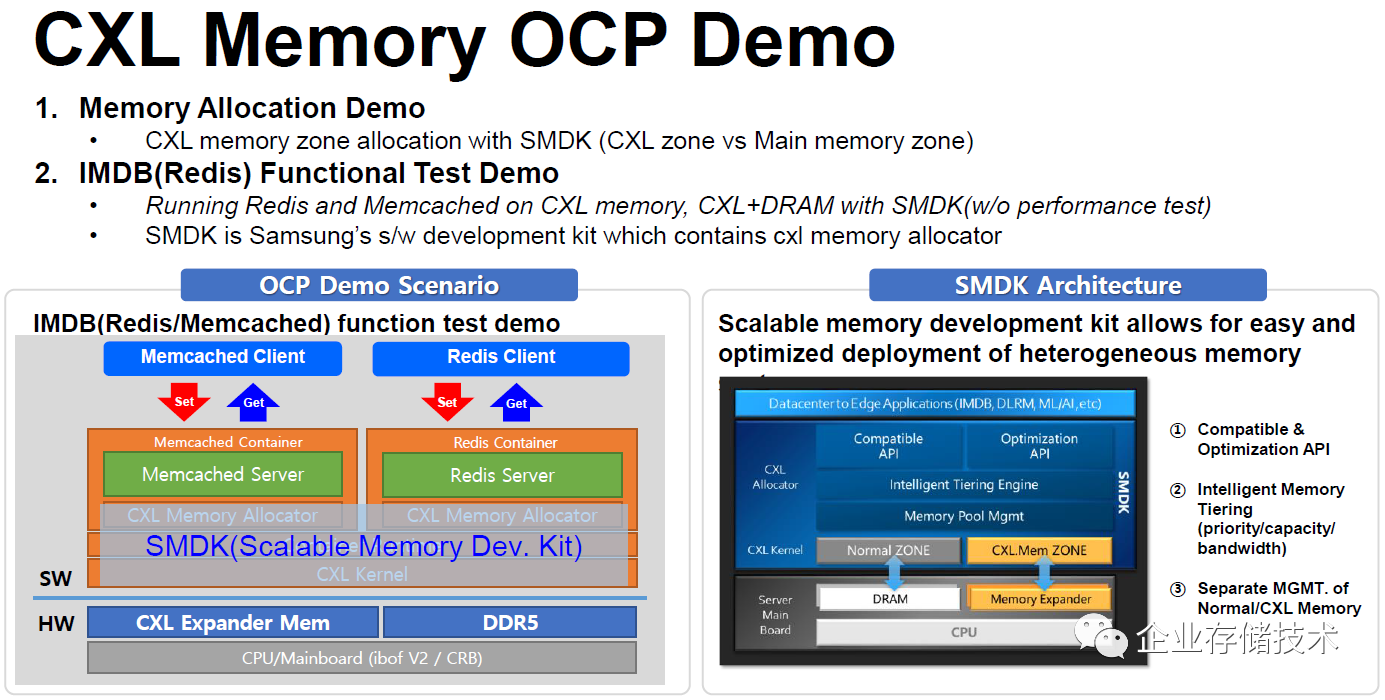

上图介绍了CXL内存在OCP会议上的Demo,第一个就是用SMDK把主内存和CXL分配到两个Zone。

第二个是内存数据库功能测试。这个应该是把CXL和DRAM主内存统一在一起(但还没有做性能测试),经过SMDK分配之后上面跑了Memcached和Redis两个容器。

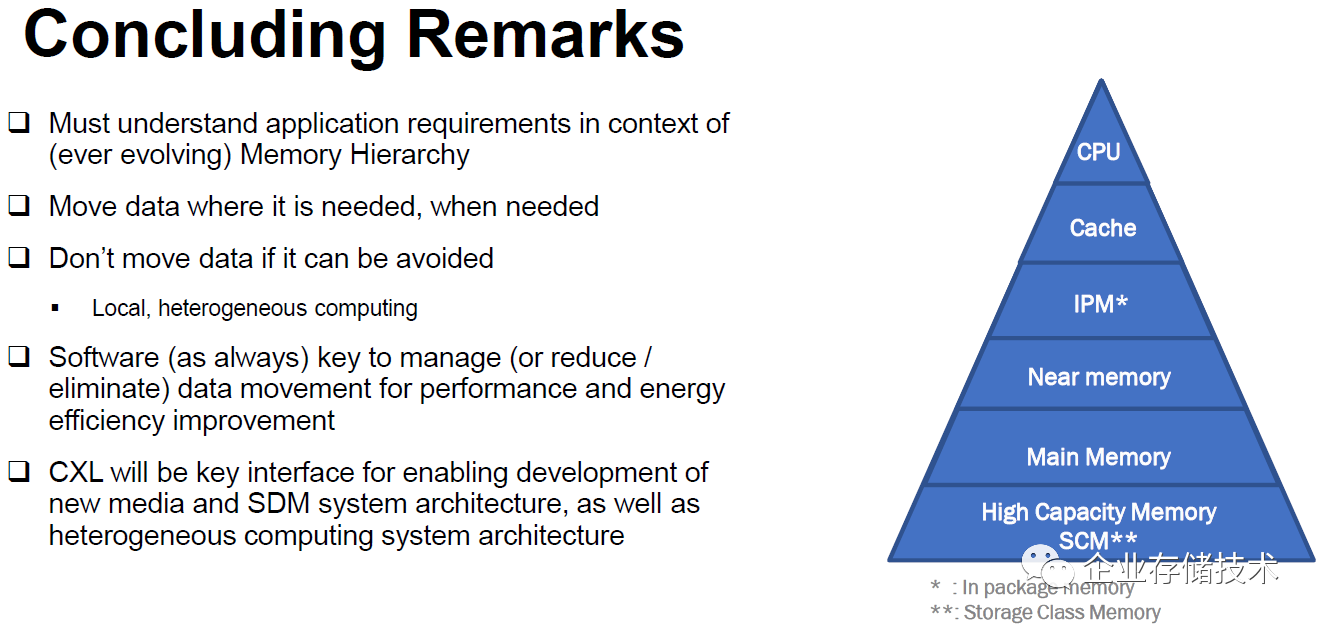

前有Intel Optane DC Persistent Memory在DIMM插槽上引入新介质,三星CXL内存又要随着代号Sapphire Rapids的Xeon服务器更新对DRAM进行扩展,再加上Intel还要在CPU Package上增加HBM Cache(部分型号)。未来的内存层级将变得更为复杂,利用好才是关键,我觉得有必要把这几条结论翻译给大家:

o必须理解(不断发展的)内存层次结构中的应用程序需求

o在需要时将数据移动到需要的地方

o如果可以避免,请不要移动数据

- 本地、异构计算(比如在CPU主内存和GPU内存之间)

o软件(一如既往)是管理(或减少/消除)数据移动以提高性能和能源效率的关键

oCXL将成为支持新介质和SDM(软件定义内存)系统架构以及异构计算系统架构发展的关键接口

三星最后还提到了UCIe,倒也是跟CXL相关的一个热点。Samsung有DRAM、HBM、NAND、Arm、半导体代工等,加入UCIe并不意外,本文我先不展开讨论了。

作者:唐僧 huangliang

原文:企业存储技术

推荐阅读

欢迎关注企业存储技术极术专栏