SystemVerilog常用可综合IP模块库

想拥有自己的SystemVerilog IP库吗?设计时一个快捷键就能集成到自己的设计,酷炫的设计你也可以拥有!

每个公司应该都会维护属于自己公司风格的IP库,作为个人学习或者持续使用的方式,这种方法很有用。今天肯定不是分享我司的IP库,而是一个开源库,每个人都可以使用、维护或者修改,当然作为学习(多人维护)也是不可多得的资料。把该库集成到自己常用的文本编辑器(Sublime\VScode\Vim等等)可以很快完成代码设计。

简介

这是verilog/systemverilog 可综合模块的集合。

所有代码在典型的 FPGA 和主流 FPGA 供应商中都具有高度可重用性。

本项目是几个常用可综合模块集合的集合,下面分别介绍这些项目。

工程链接

❝

https://github.com/suisuisi/b...

详细介绍

basic_verilog

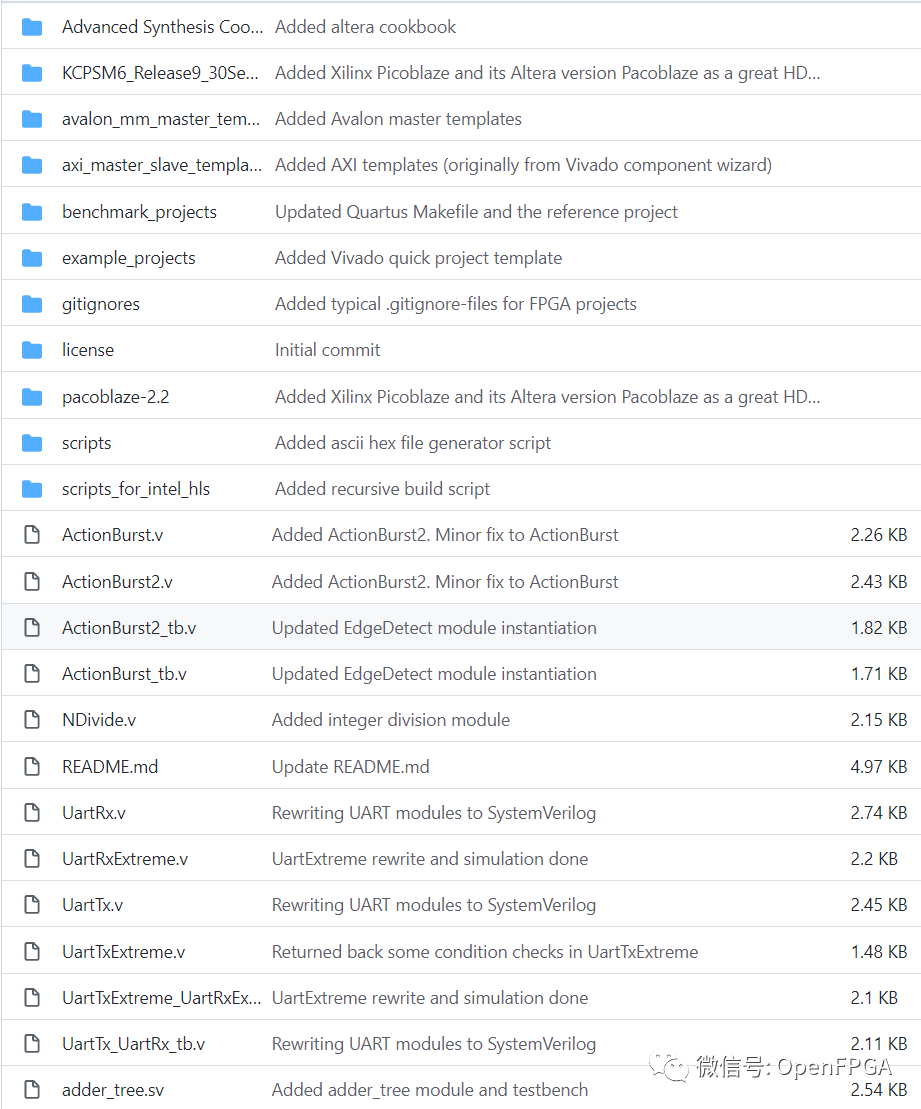

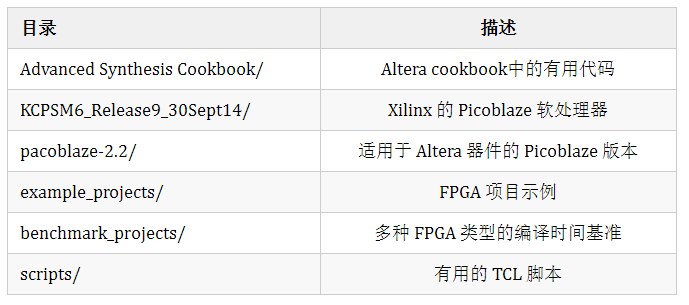

文件夹外的文件根据文件名很容易判断其用途,下面着重介绍文件夹内部文件:

注1:cookbook:类似技巧大全的意思

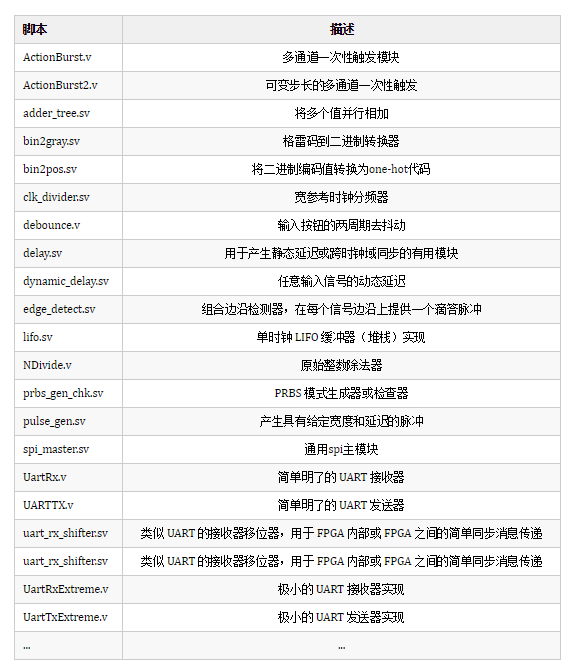

这里还有一个TCL脚本文件,再简单介绍一下:

注2:Avalon:ALTERA公司FPGA内部使用的总线,下图是典型Altera FPGA系统

其他模块说明

generic_systemverilog_designs_library

- binary_counter

SystemVerilog 中具有异步复位的 n 位二进制计数器。

- binary_to_gray

SystemVerilog中的n位二进制到格雷码组合转换器电路。

- demultiplexer

具有宽度和输出端口数量参数化的解复用器。

- full_adder

SystemVerilog 中的 n 位全加器

- full_subtractor

SystemVerilog 中的 n 位全减法器

- gray_counter

使用 SystemVerilog 中的二进制计数器和二进制到格雷码组合转换器电路实现的具有异步复位的 n 位格雷码计数器。

- multiplexer

具有宽度和输入端口数量参数化的多路复用器。

SvLibDR

包括串口和SPI接口的可综合IP模块

SystemVerilog-Bitmap-Library-AXI-Image-VIP

描述

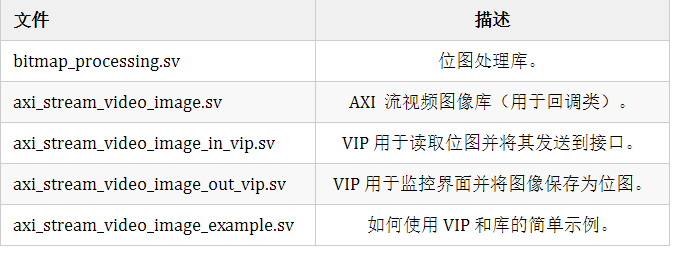

要验证视频或图像处理 IP,可能需要将真实图像读取到设计中,并通过接口发送其数据。然后,从界面获取输出,并将其转换为新图像,保存或比较。

为了解决这个复杂的问题,设计了这个库,它可以帮助您简化设计流程。使用一些简单的 API 可以轻松地在测试台中读取和写入标准位图文件 (.BMP)。并且,使用 AXI-Stream Video Image VIP,可以轻松地将图像发送到与 Xilinx 用户指南 UG934 兼容的标准 AXI-Stream 视频接口,从输出接口接收图像并保存。

位图处理库可以通过 System Verilog 将 Windows 位图文件 (.BMP) 读取和写入位数组(虚拟内存),以进行 IP 验证。该库支持 24 位和 32 位位图读入和 32 位位图写出。

使用位图处理库的 AXI-Stream Video Image VIP。“axi_stream_video_image_in_vip”IP 可以将位图文件读入内存,并通过 AXI-Stream 视频接口(在 Xilinx 用户指南 UG934 中定义)发送。而“axi_stream_video_image_out_vip”IP可以监控一个AXI-Stream接口,获取在接口上传输的帧并保存到位图文件中。

一般信息

支持的位图:

输入:24-bpp/32-bpp RGB/RGBA 位图 输出:32-bpp RGBA 位图

这个库的优势

- 简单的 API

- 开源

- 与流行的 EDA 工具兼容(在 Modelsim 和 Qustasim 上测试)

包中的文件

关于包使用等详细信息,请查看项目介绍。

总结

今天只介绍了一个项目,这个项目可以给大家提供一个思路尤其对于没有工作或者刚入门不久的同行,自己在编写代码时要想着可继承性,这样在以后做类似项目时可以借用,并且长期维护一个代码对于这个模块的理解有很大帮助。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文:OpenFPGA

作者:碎碎思

相关文章推荐

更多FPGA技术干货请关注FPGA 的逻辑技术专栏。