PHY Interface For the PCI Express, SATA, and USB 3.1 Architectures

Version 4.3

©2007 - 2014 Intel Corporation—All rights reserved.

7.1 Clocking

PHY 接口组件中会使用到 3 个时钟信号。第一个时钟信号,CLK,是 PHY 的参考时钟,用于产生内部数据发送接收比特流时钟。协议中没有该时钟的具体定义,定义基于实现时的细节,必须由厂商在实现时定义。对于不同工作模式的 PHY,协议定义会有所不同。CLK 可能拥有扩频调制功能,因为其需满足系统的参考时钟需求。(举例而言,Card Electro Mechanical Specification 可能需要参考时钟具有扩频调制功能)

第二个时钟信号,PCLK,在 “PCLK as PHY Output” 模式下是 PHY 输出给外部逻辑的时钟,在 “PCLK as PHY Input ” 模式下是每个数据通道 PHY 统一使用的外部时钟输入,并行接口使用统一的外部输入时钟来同步各个数据通道的数据。PCLK 的频率取决于数据速率、PCLK 频率选择、以及控制输入以及输出数据位宽的 PHY 工作模式。PCLK 上升沿是数据采样的参考点。PCLK 也可能支持扩频调制。

第三个时钟信号,MAX PCLK,是一个输出频率恒定的时钟信号,频率由 PHY 所支持的最高传输速率决定。 PHY 仅在 “PCLK as PHY Input ” 模式,或者是在所有支持 PCIe 3.0 的模式中需要 MAX PCLK。

7.2 Reset

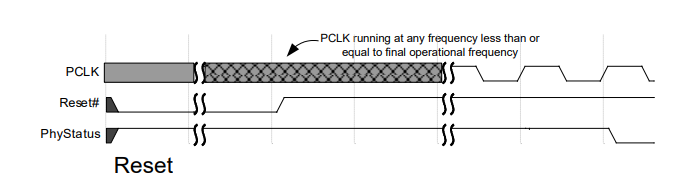

当 MAC 想要复位 PHY 时(比如在上电初始化时),MAC 必须将 PHY 置于复位状态,直到电源和时钟供应稳定。

在 MAC 移除复位信号后,PHY 在输入时钟 PCLK 以及/或者 MAX PCLK 稳定(比如 PCLK 以及/或者 MAX PCLK 到达正常工作频率至少一个时钟周期),并且供电稳定时,通过置低 PhyStatus 信号通知 MAC 其时钟和电源已经达到稳定。

在 PHY 的复位信号 RESET# 有效期间,MAC 发送给 PHY 的 PIPE 信号必须保持以下要求:

- TxDetectRx/Loopback 置低

- TxElecIdle 置高

- TxCompliance 置低

- RxPolarity 置低

- PowerDown = P1 (PCI Express 模式)

- PowerDown = P2 (USB 模式)

- PowerDown set to the default value reported by the PHY (SATA 模式)

- TxMargin = 000b

- TxDeemp = 1

- PHY Mode 设置为 PHY 的实际工作模式

- Rate 设置为 2.5GT/s (PCI Express 模式)

- 5.0 GT/s or 10 GT/s (PHY 最高支持的速率) (USB 模式)

- any rate supported by the PHY (SATA 模式)

- TxSwing 复位默认值基于具体实现

- RxTermination 置高 (USB 3.0 模式)

图 7- 0 PHY 复位释放时序图,关于 PCLK,RESET#以及 PhyStatus

7.3 Power Management – PCI Express Mode

电源管理相关的信号用于指导 PHY 最小化电源的消耗。PHY 必须满足各个电源状态下,_PCI Express Base Specification_ 中关于时钟恢复和链路训练的时序约束。PHY 还需要满足所有的发送和接收机关于终结(termination)的需求。

PCIe 定义了四种电源状态,分别是 P0、P0s、P1 以及 P2。P0 是 PHY 的正常工作状态。当 PHY 从 P0 进入其他低功耗状态时,PHY 最好可以立刻实现各个状态中规定的低功耗措施。PHY 还需要最多实现四种额外的 PHY 专用电源状态。MAC 在满足 PCI Express Base Specification 规定的所有需求的前提下,使用任意的 PHY 专用电源状态。

在 P0、P0s、P1 状态中,PCLK 需要保持运行状态。在上述三种状态之间,以及和 PCLK 保持运行状态的 PHY 专用状态之间,进行状态切换时,PHY 通过置起 PhyStatus 一个周期来表示一次成功的状态切换,切换进入预期的状态。

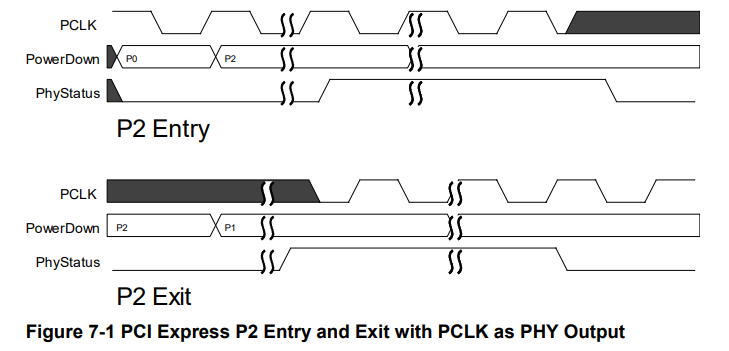

而对于进出 P2 状态,或者其他 PCLK 不再保持运行状态的 PHY 专用状态时,MAC 必须等到 PHY 表示状态已经切换完成后,再进行需要 PCLK 的操作(Operational sequence)或者后续的电源状态切换。

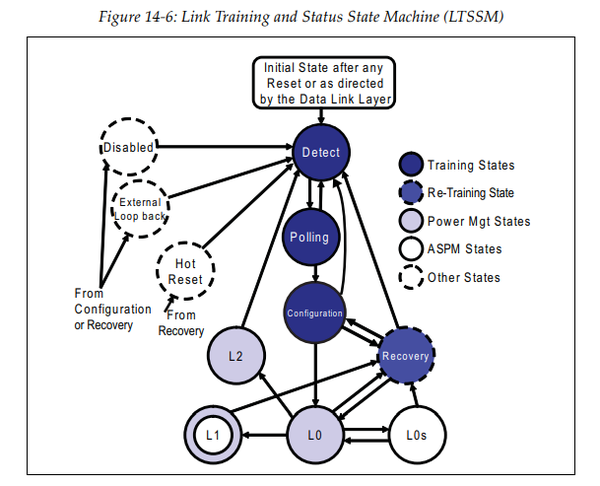

下面讨论了如何将 PHY 电源状态(译注:Px)映射到协议规定的 LTSSM 链路状态中(译注:Lx)。只要 MAC 满足 PCI Express Base Specification 规定的所有需求的前提下,MAC 也可以选择使用 PHY 专用电源状态。

- P0 状态: 所有的内部时钟都在工作。P0 是 PHY 发送接收 PCIe 信号的唯一状态。P0 对应 LTSSM 中大部分的状态,除了下述提到的这些低功耗 PHY 状态以外。

- P0s 状态:PHY PCLK 输出时钟必须保持工作。MAC 只能在发送通道空闲时,将 PHY 转移进入该状态。P0s 状态对应 LTSSM 中的发送机 Tx_L0s.Idle 状态。

- 当 PHY 处于 P0 或者 P0s 状态时,如果接收机检测到接收方向上的电气空闲,PHY 的接收机部分逻辑可以采取对应的省电措施。但注意到,当接收通道上接收信号恢复后,PHY 必须能够在 PHY 规定的时间(N_FTS with/without common clock)内重新完成比特以及符号同步锁定。当然,这项规定只对 PHY 曾经在先前的 P0 或者 P0s 状态,完成过符号或者比特同步锁定的情况而言。

- P1 状态:PHY 部分选定的内部时钟可以被关闭,但是 PCLK 必须保持工作。MAC 只能在发送和接收通道都空闲时,才能将 PHY 转移进入该状态。PHY 在 PCLK 稳定以及工作电压(DC common mode voltage)稳定并电压值满足协议要求之后,才能宣称进入了 P1 状态(通过置高 PhyStatus 信号)。P1 对应于 LTSSM 中的 Disabled 状态,所有 Detect 状态以及 L1.idle 状态。

- P2 状态: PHY 部分选定的内部时钟可以被关闭,并行总线均处于异步模式,PCLK 也被关闭。

PCLK as PHY Output: 该模式下,当 PHY 状态转移为 P2 时,PHY 必须在 PCLK 关闭前置高 PhyStatus,在 PCLK 完全关闭,PHY 进入 P2 状态后,置低 PhyStatus。在 PHY 从 P2 状态退出时,PHY 需要尽可能快地置高 PhyStatus,并且保持置高状态,直至 PCLK 稳定。

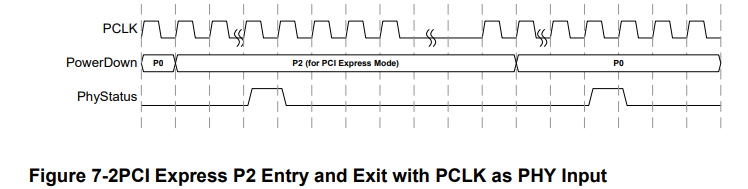

PCLK as PHY Input: 该模式下,当 PHY 状态转移为 P2 时,PHY 需要置高 PhyStatus 一个输入时钟周期,表示其准备好关闭 PCLK。在 PHY 从 P2 状态退出时,PHY 需要尽可能快地置高 PhyStatus 一个输入时钟周期,表示进入 P0 状态,并为重新工作做好准备。

当 PHY 从一种 PCLK 停止工作的状态,转移到另一种 PCLK 同样不工作的状态时,PHY 需要在状态转移完成后置高 PhyStatus,并保持置高直到 MAC 置高 AsyncPowerChangeAck 信号,之后 PHY 置低 PhyStatus。

PHY 在设计实现中应该尽可能降低 P2 状态中的功耗,因为 PHY 此时需要工作在协议规定的 Vaux 电压范围内(参阅 PCI Express Base Specification)

P2 状态对应于 LTSSM 的 L2.Idle 状态以及 L2.TransmitWake 状态。

图 7-1 PCLK as PHY Output 模式下,PCIe P2 状态的进入与退出时序图

图 7-2 PCLK as PHY Input 模式下,PCIe P2 状态的进入与退出时序图

MAC 控制下的 PHY 状态转移行为是有限制的,基于 PCIe 协议中规定的 LTSSM 状态转移图,以及前一段中叙述的 PHY 状态与 LTSSM 的状态关系映射,可以得到合法的状态转移有那么几种:

- P0 --> P0s

- P0 --> P1

- P0 --> P2

- P0s --> P0

- P1 --> P0

- P2 --> P0

这些状态之间的转移条件,参阅 PCIe 协议。

从上述状态转移到 PHY 专用电源状态,或者从专用电源状态转移到上述状态都是 PIPE 协议允许的(另有规定除外),同时 MAC 也需要保证上述 PHY 专用状态转换满足 PCIe 协议的时序要求。

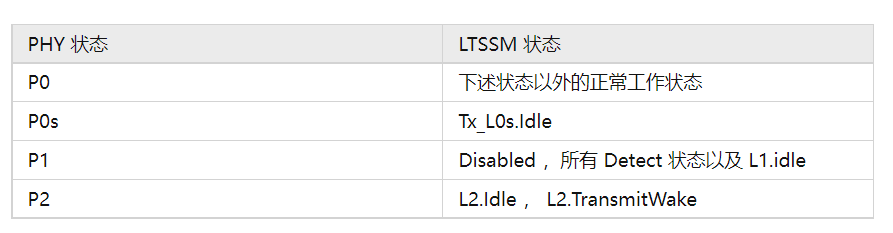

译者供表:PIPE Px 状态与 PCIe 链路状态之间的关系

译者供图:图来自于 Mindshare PCIe 3.0 文档 14-6,LTSSM 状态转移图

7.4 Power Management – USB Mode

翻译暂略

7.5 Power Management – SATA Mode

翻译暂略

原文: Mindshare

译者: Michael ZZY

校对: LJGibbs

文章来源:https://zhuanlan.zhihu.com/p/512366155

《PCI Express Technology 3.0》翻译系列

- PHY Interface :3 PHY/MAC interface & 4

- PHY Interface 协议翻译: 2 Introduction

- PCI Express Technology 3.0 Chapter 6 流量控制 5-7 节

- PCI Express Technology 3.0:Chapter 6 流量控制 1-4 节

- 《PCI Express Technology 3.0 》Chapter 5 第3 节

- 《PCI Express Technology 3.0》Chapter 5

- PCI Express Technology 3.0:Chapter 1 Background/背景

- PCI Express Technology 3.0:PCIe体系结构概述 2.1 节

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3 节(完)

更多IC设计技术干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。

另外为 《Mindshare PCI Express Technology 3.0 一书的中文翻译计划》打个广告,欢迎参与翻译/校对