Verilog之Generate for用法注意事项

Generate for的用法:

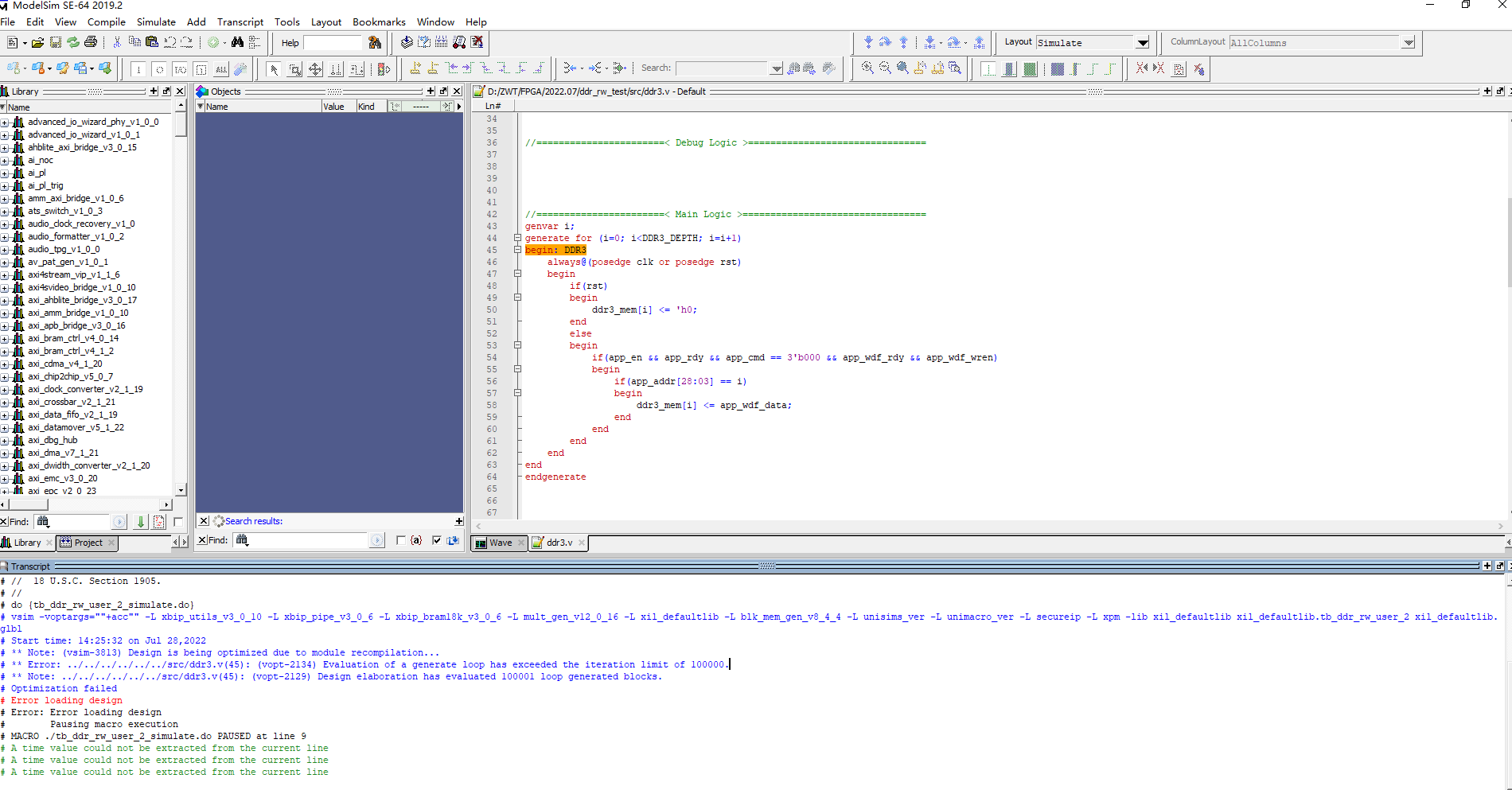

对于FPGA工程师来讲verilog语法可以说是不能再熟悉了,在verilog中generate for可以用来生成重复性的逻辑,比如下面这段代码定义了一个寄存器组ddr3_mem来模拟DDR3,按照地址将数据写入ddr3_mem;

parameter DDR3_DEPTH = 65536;

reg [127:0] ddr3_mem[DDR3_DEPTH-1:0];

genvar i;

generate for (i=0; i<DDR3_DEPTH; i=i+1)

begin: DDR3

always@(posedge clk or posedge rst)

begin

if(rst)

begin

ddr3_mem[i] <= 'h0;

end

else

begin

if(app_en && app_rdy && app_cmd == 3'b000 && app_wdf_rdy && app_wdf_wren)

begin

if(app_addr[28:03] == i)

begin

ddr3_mem[i] <= app_wdf_data;

end

end

end

end

end

endgenerate注意事项

虽然generate for生成的代码是可综合的,但个人更多的在testbench中使用,那么在使用的过程中笔者就发现这个for循环的循环层数是有限制的,最大不能超过100000,如果超过了至少modelsim就会报错,error信息如下。所以我上面的代码中parameter定义成了65536。

# do {tb_ddr_rw_user_2_simulate.do}

# vsim -voptargs=""+acc"" -L xbip_utils_v3_0_10 -L xbip_pipe_v3_0_6 -L xbip_bram18k_v3_0_6 -L mult_gen_v12_0_16 -L xil_defaultlib -L blk_mem_gen_v8_4_4 -L unisims_ver -L unimacro_ver -L secureip -L xpm -lib xil_defaultlib xil_defaultlib.tb_ddr_rw_user_2 xil_defaultlib.glbl

# Start time: 14:25:32 on Jul 28,2022

# ** Note: (vsim-3813) Design is being optimized due to module recompilation...

# ** Error: ../../../../../../src/ddr3.v(45): (vopt-2134) Evaluation of a generate loop has exceeded the iteration limit of 100000.

# ** Note: ../../../../../../src/ddr3.v(45): (vopt-2129) Design elaboration has evaluated 100001 loop generated blocks.

# Optimization failed

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./tb_ddr_rw_user_2_simulate.do PAUSED at line 9