在UVM框架下,使用sequence来产生测试激励的方法非常高效,用户可以根据测试场景来构造和复用不同抽象层次的测试序列(sequence)。

在前面的文章中介绍了sequence基础的使用方法,包括sequence的重要成员和方法、如何产生sequence_item以及如何启动sequence等。

本文将接着介绍当有多个Sequence的时候如何执行和控制,以及virtual sequence和sequence library的使用。

01 多sequence的执行和控制

Sequence的启动通常在这么几个地方做:在某一个component(比如env)的main_phase中,或者测试用例类uvm_test的main_phase中,还可以在已经被启动的sequence的body()方法中。

但不管在什么地方启动,对于同一个Testbench,都建议将根sequence固定放在同一个地方,方便维护和调试。这里说的根sequence,指的是不在其他sequence的body()方法中启动的sequence。

多个sequence被启动之后的执行流,根据串并行关系,大致有这么几种类型:串行执行、并行执行和层次执行,如上图所示。图中黄色框是串行执行,绿色框是并行执行,蓝色框是层次执行。

之所以这么梳理,一方面是为了让读者知道自己可以这么做,另一方面是提醒读者慎重选择一些自己都觉得不可预期的执行方式。比如使用fork+join\_any或者fork+join\_none去发起并行sequence,又或者在sequence的body方法中加入了死循环,就需要考虑与sequencer的握手机制会不会引入异常,以及sequence是不是可以正常执行结束退出。

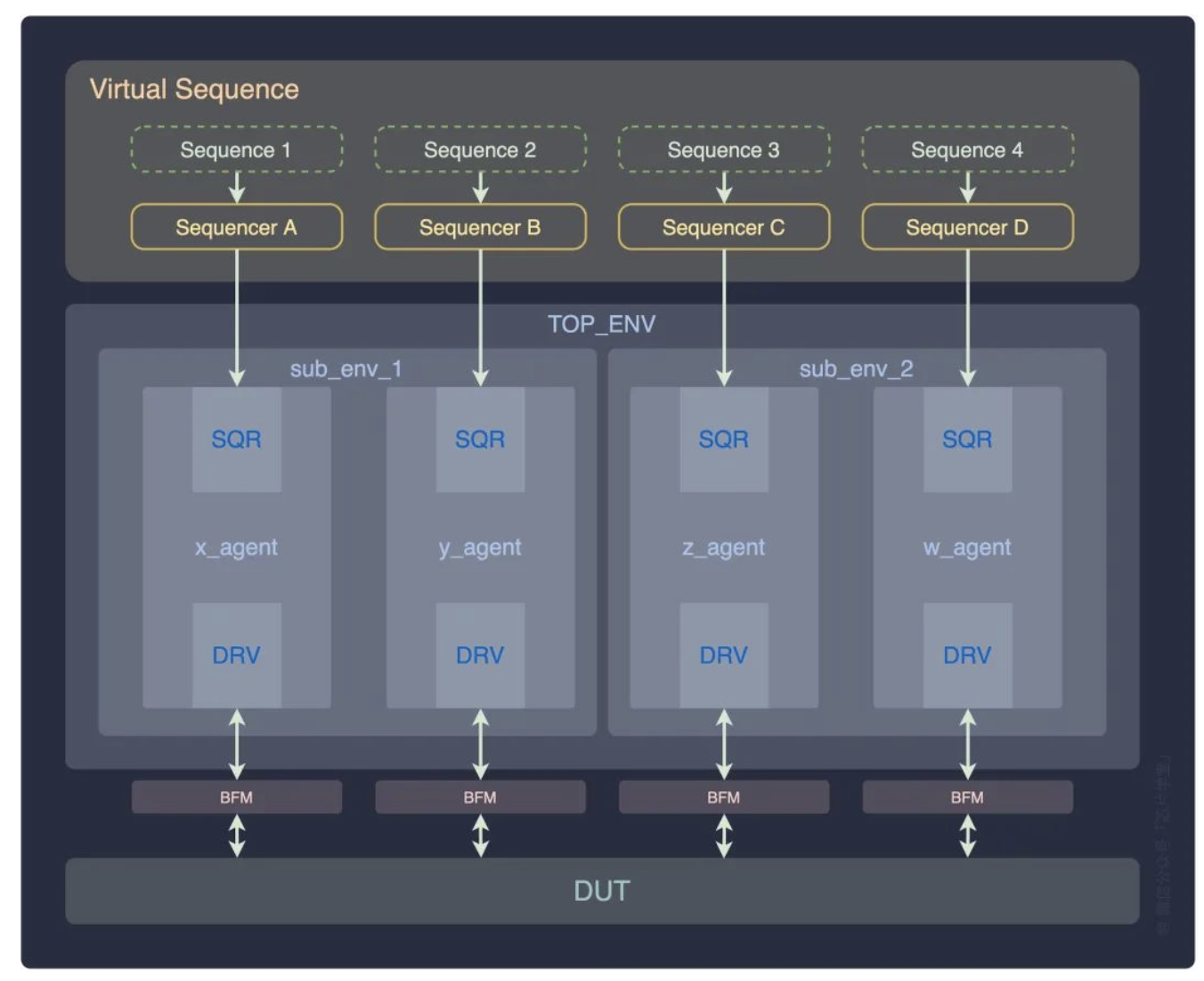

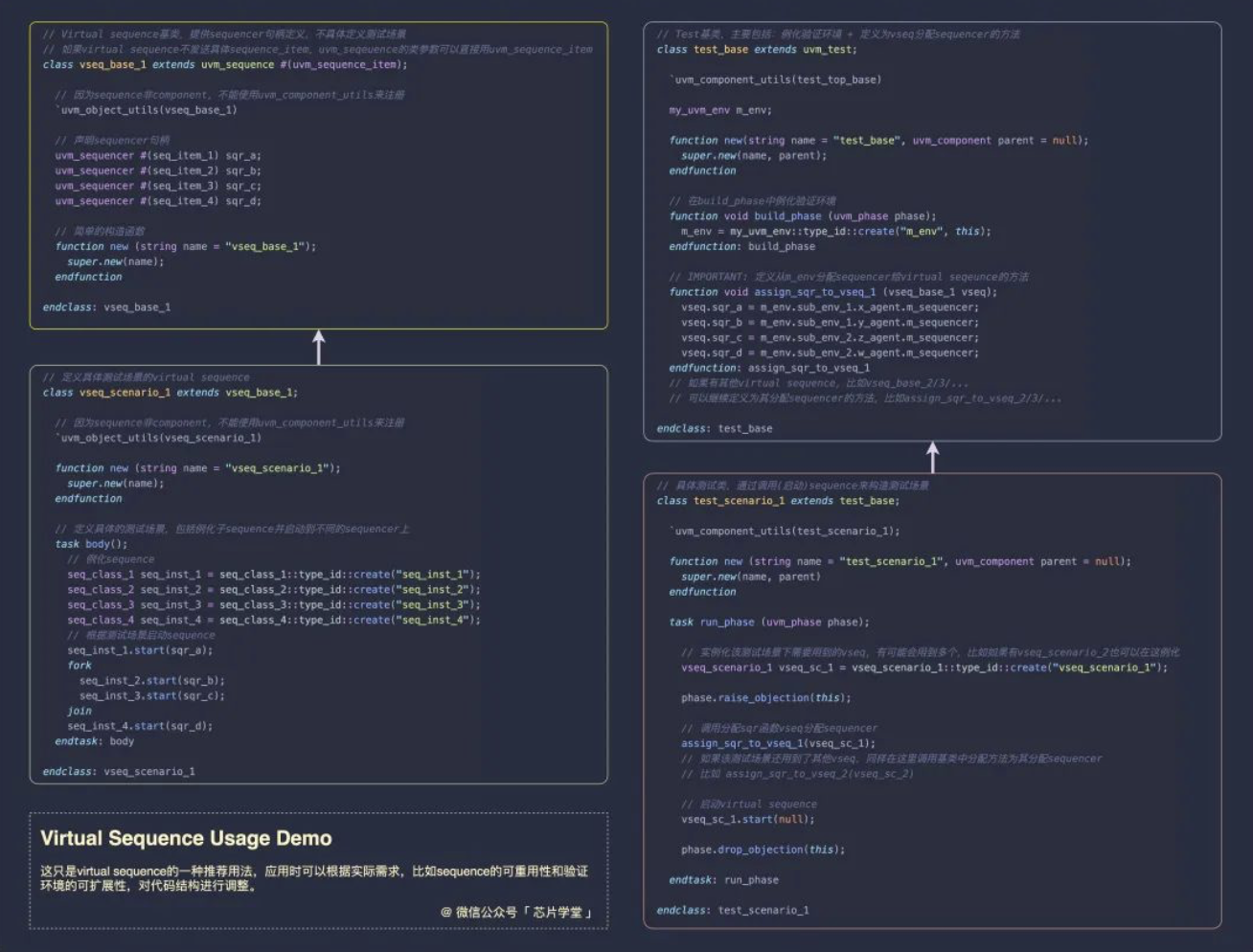

02 Virtual Sequence

Virtual sequence的virtual的含义,跟抽象类或者抽象方法声明时用的关键字不一样,也跟计算机体系结构中的虚拟内存、虚拟主机等概念不一样。Virtual sequence的virtual想表达的意思是:这是一个不发送sequence item,主要用于启动和控制面向不同sequencer的多个sequence的sequence,大家甚至可以称之为top sequence或者master sequence,这样也许会好理解一些。

实际上,代码是自由的,virtual sequence也只是一个名字而已,谁也没有规定叫了这个名字就不能去发送sequence item,也没有谁规定一个验证环境只能有一个virtual sequence。只不过,这种多sequence的管理方法比较好用和科学,才被单独提出来和介绍,一切要根据实际情况去做决定。

上图是使用了virtual sequence的UVM测试结构。可以看到virtual sequence包含了多个sequencer句柄,这些句柄在virtual sequence被实例化的时候需要指向具体的sequencer对象。示例代码如下:

Virtual sequence的常见使用方法就是在test类的run phase中被实例化,完成sequencer句柄的引用分配,最后将其启动。这也只是常用方法,并不是必须要这么用,比如virtual sequence也可以在其他地方被启动,有需要的话它也可以包含其他句柄来引用验证环境中的更多对象。

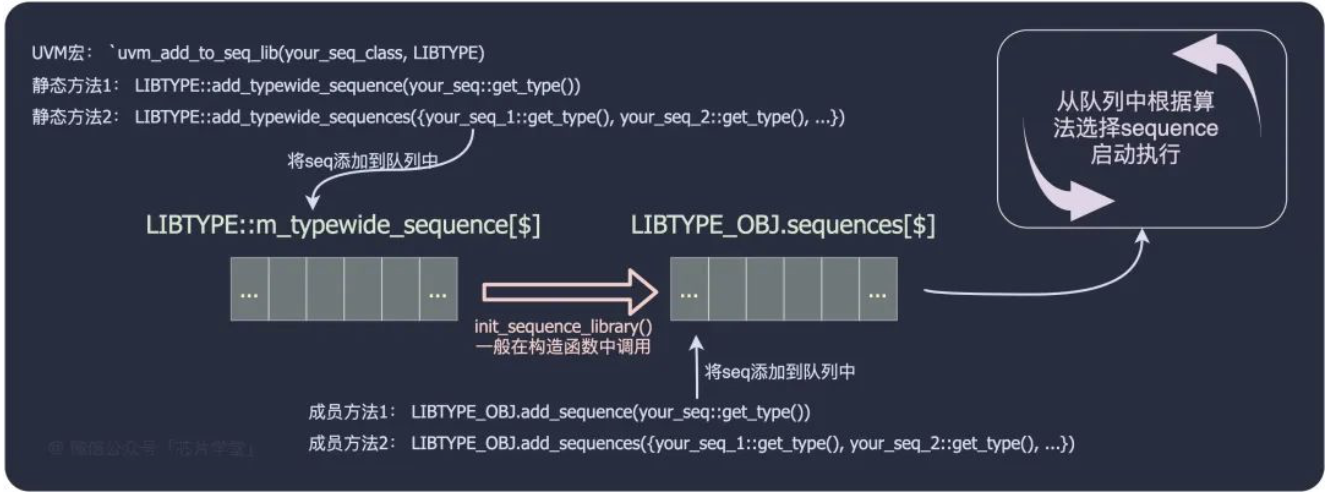

03 Sequence Library

Sequence library是一种可以作为很多sequence的容器的sequence,基类是uvm_sequence_library。当sequence library被启动之后,会根据预设算法(默认是随机执行)和执行次数(默认是执行10次),从注册到该library的sequences队列中选取sequence并启动执行。

关于sequence library,在应用上两个方面需要关注:一个是如何将sequence注册到sequence library;另一个是如何配置或者控制sequence library中sequence。

注册sequence到sequence library

在sequence library类中,有两个队列。一个是通过宏、、\`uvm_sequence_library_utils定义的静态队列m_typewide_sequences[$\],另一个是uvm_sequence_library类成员sequences\[$]。我们最终要使用的是sequences[$]。下面用LIBTYPE表示我们定义的sequence library类名。

第一种方法:在sequence_library类被实例化之前,我们可以在test类的build_phase中,将sequence通过LIBTYPE::add_typewide_sequence或者LIBTYPE::add_typewide_sequences这两个静态方法,逐个或者批量添加到LIBTYPE::m_typewide_sequence[$]队列中,作为候选sequence。

同时,UVM还提供了宏\`\uvm_add_to_seq_lib(TYPE, LIBTYPE)来提供相同的功能,在具体sequence类定义时,跟调用工厂注册宏一起调用。

另外,在sequence library类的构造函数中,需要调用init_sequence_library,该函数会将LIBTYPE::m_typewide_sequence[$\]中的sequence搬到sequence library的sequences\[$]中。

第二种方法:在sequence_library类被示例化之后,通过调用类方法add_sequence或者add_sequences逐个或者批量直接添加到sequences[$]队列中。

对sequence library的控制

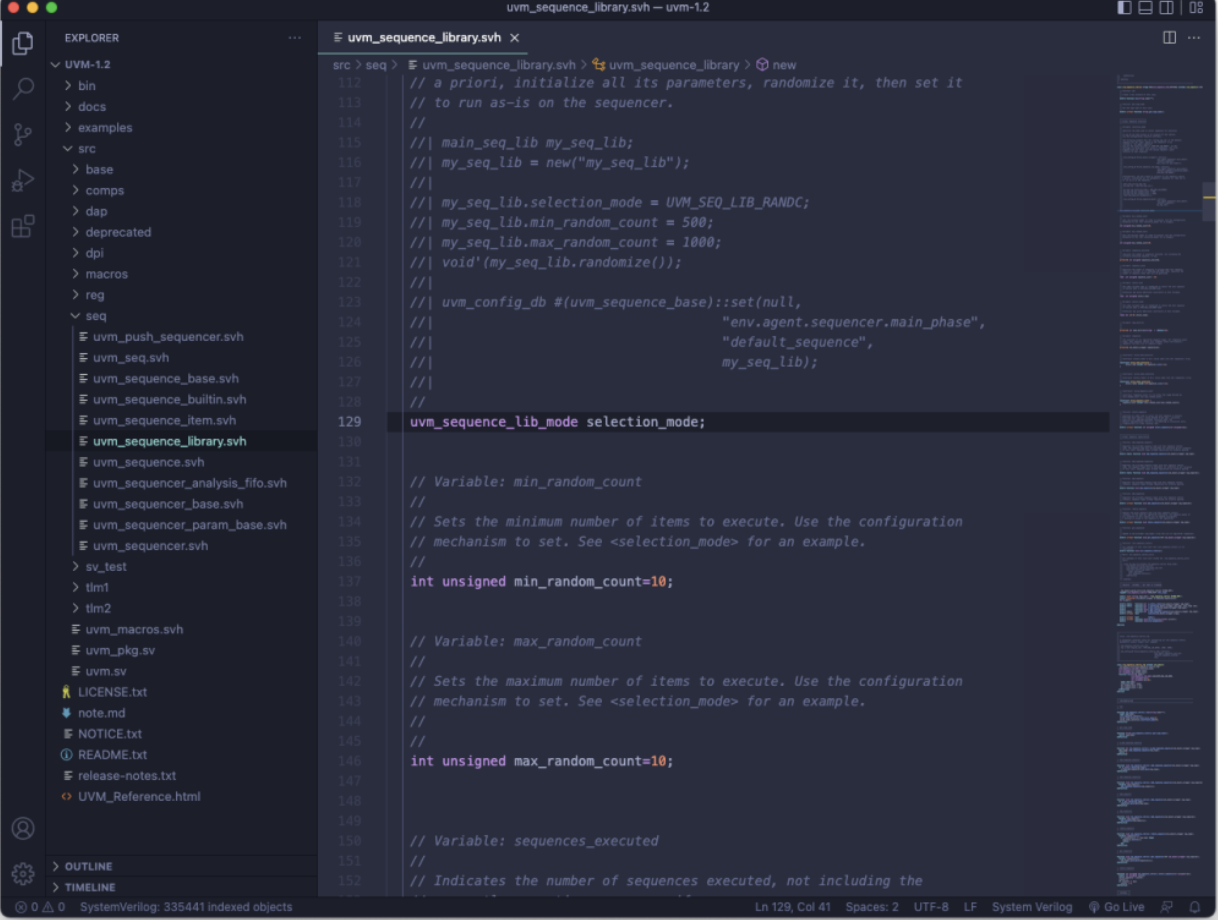

在uvm_sequence_library类中有三个用于控制的成员变量:selection_mode、min_random_count和max_random_count,分别控制从sequences[$]队列中选取sequence的算法、最少执行多少个sequence以及最多执行多少个sequence。

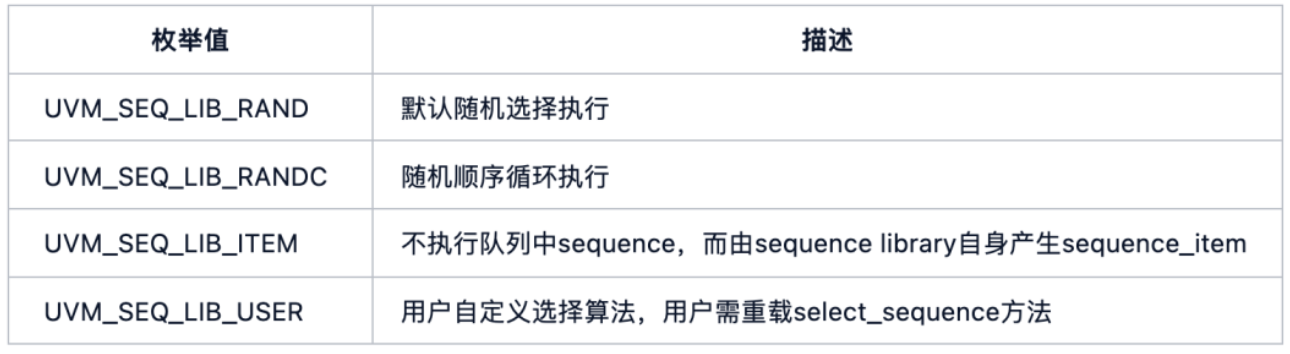

其中max/min_random_count都是int类型,而seleciton_mode是枚举类型uvm_sequence_lib_mode,有四个枚举值:

至于配置方法,可以在例化完sequence library之后直接修改对象中成员变量,也可以在使用default_sequence时通过uvm_config_db来传递配置参数。

作者:JK ZHAN,

本文首发于微信公众号“芯片学堂”(ID:HelloICTalking),芯片技术文章分享平台

推荐阅读

CCIX(九)

CCIX(八)

CPU设计之Cache -- MSHR

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。