本节介绍一个包含存储器,仲裁器,控制器,系统总线和CPU的设计,所有这些设计文件都在工具安装目录底下:

$VCS_HOME/doc/examples/testbench/sv/tutorial

01存储系统

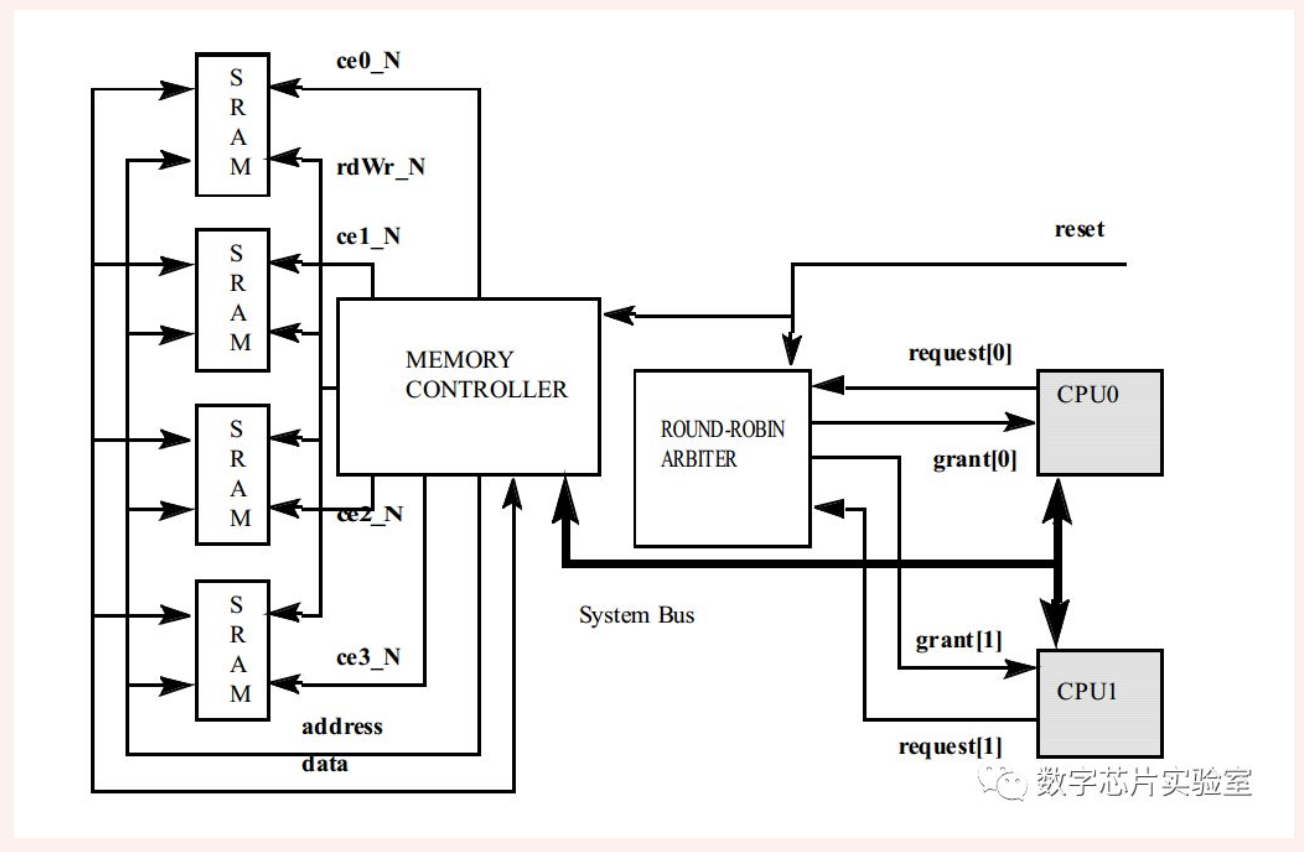

这个tutorial使用的设计是一个简单的存储系统,包含系统总线、round-robin仲裁器、控制四个SRAM的存储器控制器和两个CPU。

下图显示了该系统的原理图。

上图标有阴影的CPU0和CPU1不是被测系统的一部分,这些模块将在SystemVerilog测试平台中建模。 CPU和其余模块之间的信号是DUT外界的接口。

02 存储系统验证

大多数验证项目中,验证存储器系统的方法是类似的:

最初,所有子模块都在block level进行单独验证。然后,所有子模块都集成到最终设计中进行system level验证。

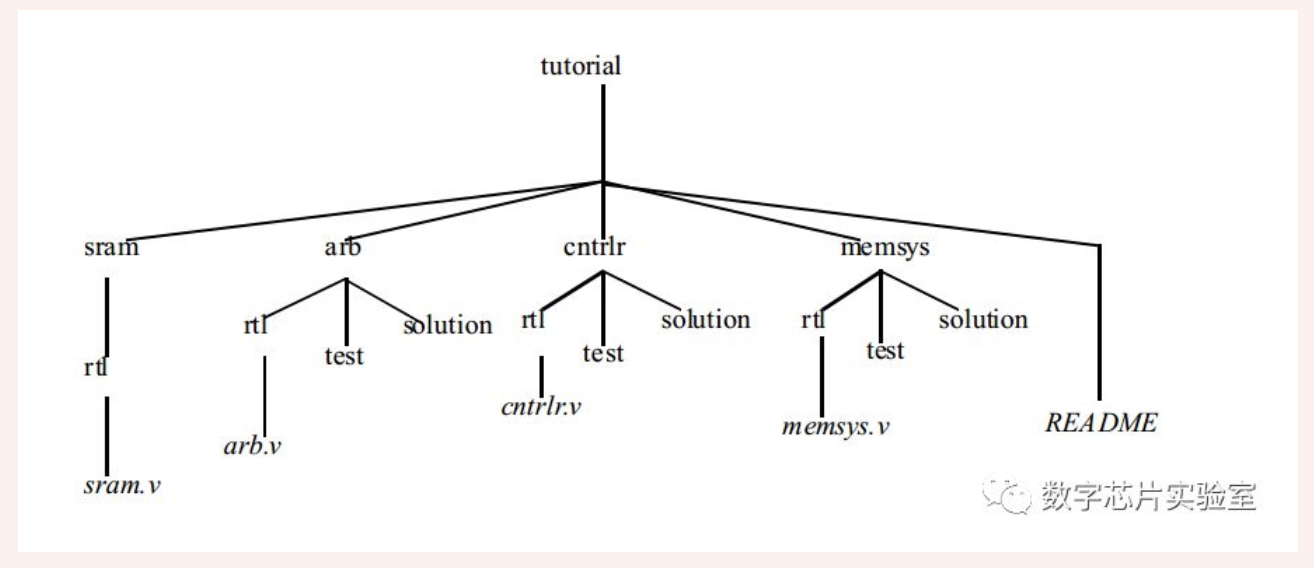

03 验证管理文件目录

•README - 简述

•sram - 子模块sram的RTL

•arb - 子模块arb 的RTL

•cntrlr - 子模块cntrlr的RTL

•memsys - 集成的top-level的RTL

•每个“rtl”目录包含Verilog HDL代码。

•每个“Solution”目录都包含测试文件和运行脚本

作者: iwonder

来源:数字芯片实验室

推荐阅读

更多数字IC设计技术干货等请关注数字芯片实验室专栏。添加极术小姐姐(微信:aijishu20)微信可申请加入IC设计交流群。