14.7 L0 State // L0 状态

L0 状态是链路的全功能正常工作状态, 虽然刚进入此状态时处于逻辑空闲状态,但之后链路两端的设备会交换 TLP 和 DLLP(译注:此处按照个人理解翻译了,原文为 This is the normal, fully‐operational Link state, during which Logical Idle, TLPs and DLLPs are exchanged between Link neighbors.)。在链路训练过程完成后,会立刻达成 L0 状态。物理层此时通过 LinkUp 变量通知更高层的逻辑: 链路已经准备就绪。此外变量 idle_to_rlock_transitioned 也复位为 00h。

退出至 Recovery 状态

如果本方设备提议改变链路速率或者宽度,或者对端设备已经进入了 Recovery 或者电气空闲状态,表示提议发起链路速率或者宽度改变,那么状态机的下一个状态是 Recovery 状态。让我们接下来用一些略详细的篇幅来介绍三种情况。

14.7.1 Speed Change // 速率切换

协议中提到两种触发自动速率改变的情况。

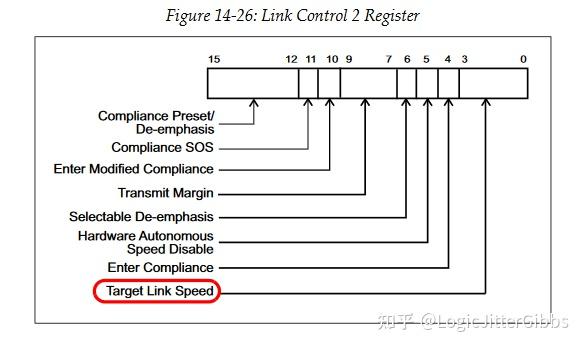

第一种情况是链路双方都支持 2.5GT/s 以上的速率,并且链路处于活跃状态时(数据链路层报告 DL_Active),或者链路一方通过 TS1/2 有序集请求速率转换时。举个例子,如果对方声明支持更高的速率,并且软件通过使能重训练(Retrain Link )比特,并将目标速率(Target Link Speed,见原文 569 页的图 14-26)设置为与当前不同的速率,那么 DSP 会发起一次速率转换。

第二种速率切换的情况是链路双方都支持 8GT/s 速率,并且一方打算进行 Tx 均衡。这两种情况下变量 directed_speed_change 都会被设置为 1b,并且 changed_speed_recovery 比特会被清除为 0b。

如果链路对端在 Configuration.Complete 或者 Recovery.RcvrCfg 状态中从未通告过比 2.5 GT/s 更高的速率,那么当前端口不会发起速率改变(也就是不会设置 directe_speed_change 变量)。

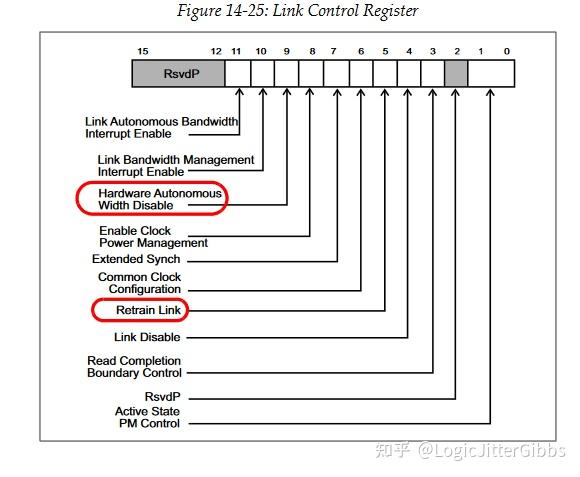

图 14-25 链路控制寄存器

图 14-26 链路控制寄存器 2

14.7.2 Link Width Change // 链路宽度切换

当变量 upconfigure\_capable 设置为 1b 时,上层的逻辑(Upper layer)一般只会减少链路宽度,用于恢复链路的原始宽度。如果禁止硬件自主决定位宽(Hardware Autonomous Width Disable)比特被置位为 1b,那么端口将只能通过减少链路宽度来解决可靠性问题。仅当链路对端伙伴通告其具有链路宽度恢复能力,并且链路宽度没有被配置为最大宽度时,上层逻辑才可以发起一次链路宽度增加操作。除了上述指导性建议以外,协议中没有其他关于何时进行链路宽度改变的规定,因此该行为的细节取决于具体实现。

14.7.3 Link Partner Initiated //链路伙伴发起链路改变的情形

协议中描述了三种链路伙伴发起链路改变的情形:

首先第一种情况,本方端口在链路上的所有通道上检测或者推断出电气空闲状态(详见原文 596 页的表 14-10),并且此前没有在任何通道上接收到 EIOS 有序集。此时,端口可以选择留在 L0 状态或者进入 Recovery 状态。如果由此产生错误,那么端口可能通过置位 Retrain link 比特的方式进入 Recovery 状态。

第二种情况,本方端口在任何已配置的通道上接收到 TS1 或者 TS2 序列(128b/130b 编码时接收到 EIEOS),这表示对端已经进入 Recovery 状态。由于这两种情况都是由对端发起的,因此本方端口发送端被允许完成正在进行中的 TLP 或者 DLLP。

第三种情况,如果任何通道上接收到了 EIOS 序列,表示对方已进行了电源状态转变,但是接收方不支持 L0s 并且没有进入到 L1 或者 L2,因此只能选择进入 Recovery 状态。

退出至 ”L0s“ 状态

在发送方发起进入 L0s 状态的请求后,或者接收方接收到 EIOS 序列后,进入 L0s 状态。有趣的是,此时发送方和接收方的 LTSSM 状态机状态可能是不同的,因为协议允许其中一方处于 L0s 状态,而另一方仍在 L0 状态。

- 发送方接收到上层逻辑进入 L0s 状态的指示后进入 L0s 状态,并在链路上发送 EIOS 发起改变请求。

- 接收方在任一通道上接收到 EIOS 后进入 L0s 状态。然而,如果接收方没有实现 L0s 状态,并且未被上层逻辑要求进入 L1 或者 L2 状态时,会被视作发生了一个问题,转而进入 Recovery 状态。

退出至 ”Rx\_L0s.Entry“ 状态

当链路伙伴被命令在链路上发起 L1 状态转移后,它会在所有通道上发送一个 EIOS 序列(如果速率为 5.0 GT/s,那就发两个 ),并在任意通道上接收到一个 EIOS 后,下一个跳转状态是 L1 状态。值得注意的是,链路进入 L1 状态之前需要链路双方都事先同意,因此需要一项数据链路层握手机制保证双方都已经准备好进入 L1。关于 L1 状态的详情,可以参考原文 733 页的 ”链路电源管理“ 一节 (原书第 16 章)。

退出至 ”L2“ 状态

当链路伙伴被命令在链路上发起 L2 状态转移后,它会在所有通道上发送一个 EIOS 序列(如果速率为 5.0 GT/s,那就发两个 ),并在任意通道上接收到一个 EIOS 后,下一个跳转状态是 L2 状态。值得注意的是,链路进入 L2 状态之前需要链路双方都事先同意,因此需要一项数据链路层握手机制保证双方都已经准备好进入 L2。关于 L2 状态的详情,可以参考原文 733 页的 ”链路电源管理“ 一节 (原书第 16 章)。

原文: Mindshare

译者: LJGibbs文章来源:https://zhuanlan.zhihu.com/p/590660608

《PCI Express Technology 3.0》翻译系列

- PCI Express Technology 3.0 链路初始化与训练 Configuration

- PCI Express Technology 3.0: 链路初始化与训练 3-4 节

- PCI Express Technology 3.0 : 链路初始化与训练 1-2 节

- 《PCI Express Technology 3.0》Chapter 5

- PCI Express Technology 3.0:Chapter 1 Background/背景

- PCI Express Technology 3.0:PCIe体系结构概述 2.1 节

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3 节(完)

- PCI Express Technology 3.0:PCIe配置概述 3.1-3.7 节

更多IC设计技术干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。