本文为由EETOP编译自semiwiki

早在 2002 年,Collett International Research 就有一项关于功能验证的研究,自 2010 年以来,Wilson Research Group 继续进行此类研究,每两年发布一份新报告。这份报告吸引人的地方在于,它不仅着眼于一家 EDA 供应商的安装基础,而且着眼于全世界,向设计和验证工程师提出问题,以便让半导体行业的更多的人能够了解功能验证的趋势。

根据IBS的数据,全球半导体市场在2021年的总价值为5470亿美元,到2023年降至5450亿美元,然后预计到2025年将增长到6350亿美元,其中IC和ASIC部门将在2025年达到3309亿美元。使用IC和ASIC系统设计人员希望功能验证是彻底和正确的,以确保他们的产品正常可靠地运行。

980 名工程师对 2022 年的调查做出了回应,涵盖 FPGA、IC、ASIC、全定制、结构化定制、结构化 ASIC,甚至包括嵌入式阵列和门阵列设计。本文的内容仅关注IC和ASIC细分市场部分。

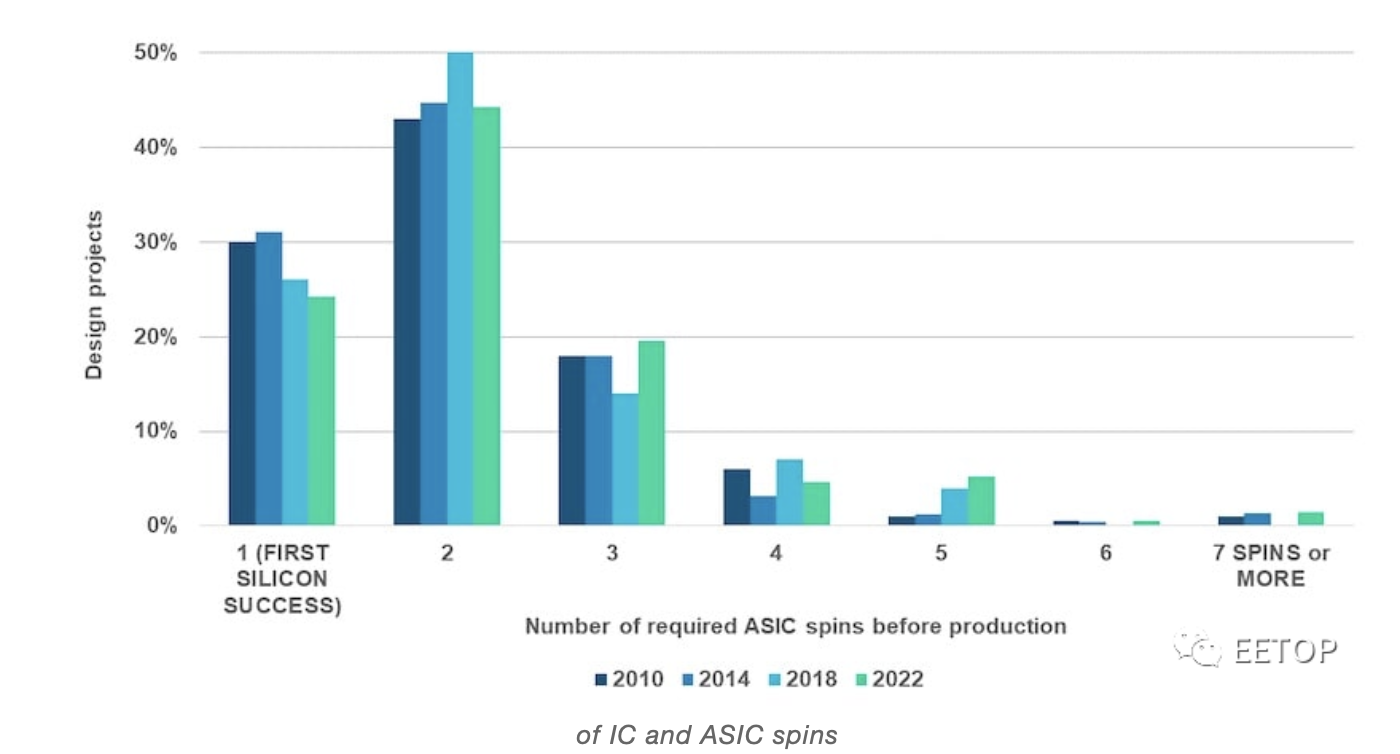

报告中的第一个指标显示了一个可悲的结果,即首次流片的成功率正在下降,只有24%,这意味着昂贵的重新设计加上损失的上市时间,从而损失了更多的收入。

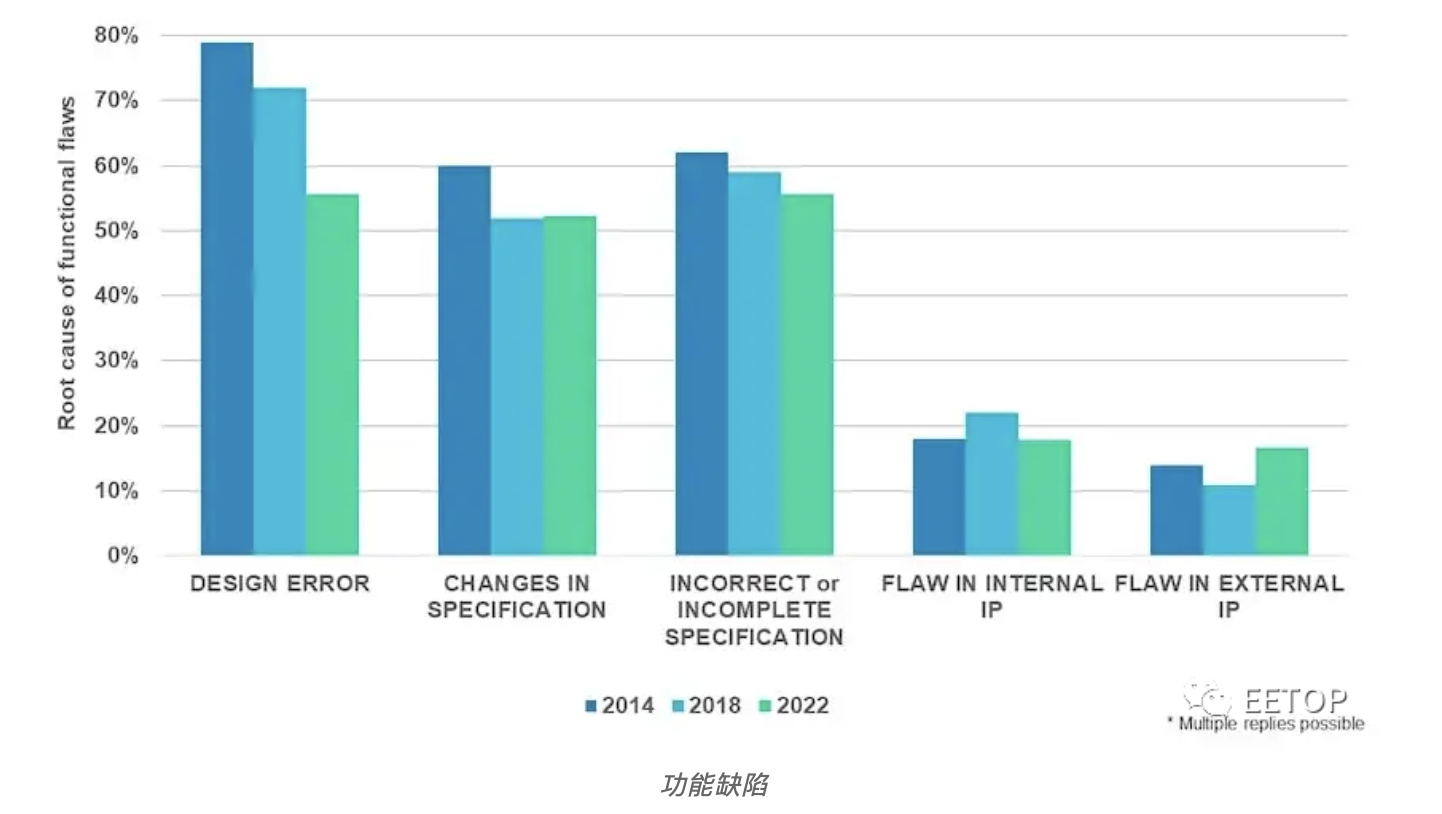

导致这些芯片重新设计的前五个因素依次是:

- 逻辑、功能缺陷

- 模拟

- 功耗

- 时钟

- 良率

可见,功能缺陷是导致故障的首要原因,这包括设计错误、规范的改变和不正确的规范等。IP 供应商应注意,内部和外部 IP 模块对功能缺陷的影响小于设计错误。

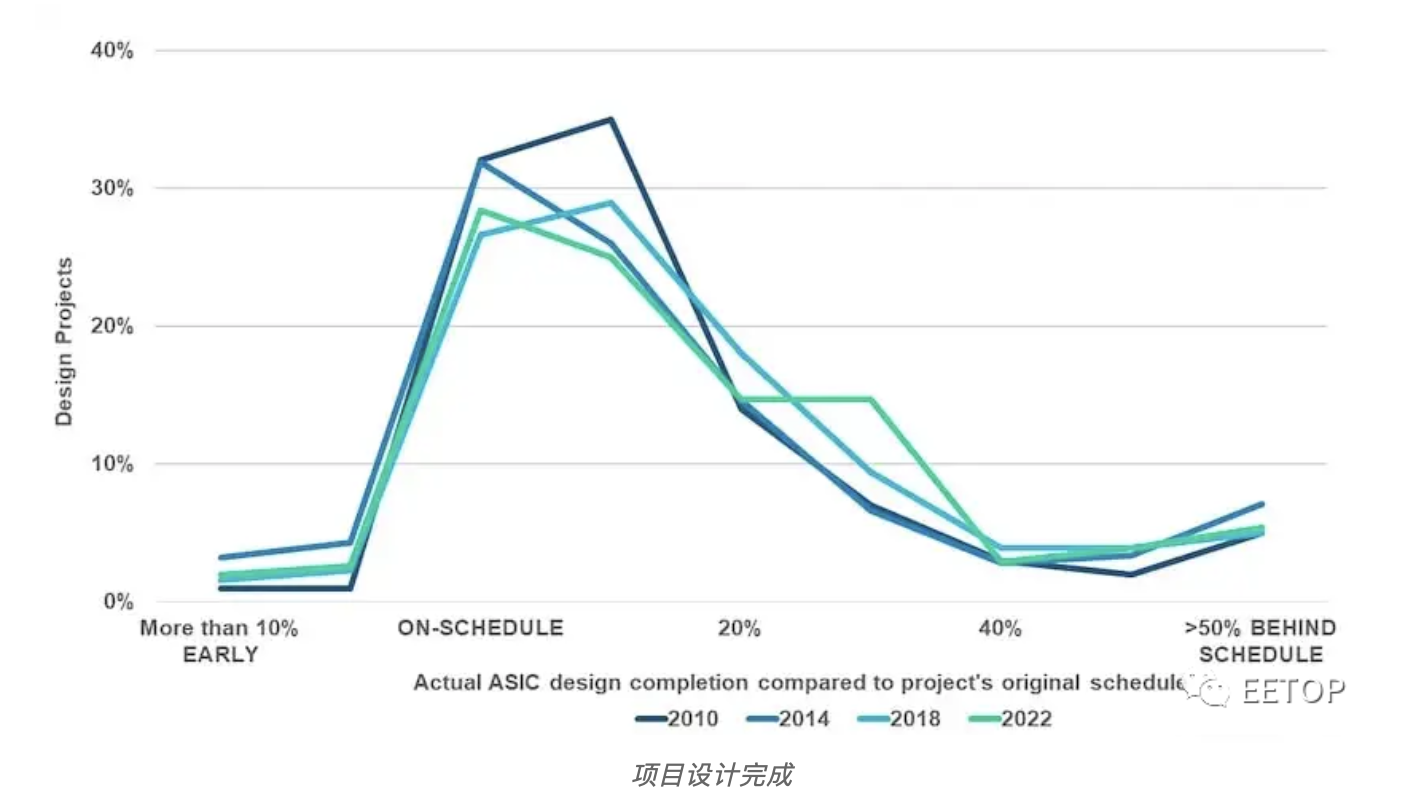

这是管理层的一个常见问题,“项目是否按计划进行?这不是一个现实的答案,因为66%的IC和ASIC项目落后于计划完成。

自2008年以来,花费在功能验证上的总时间比例一直保持在70%左右,而设计和验证工程师的平均峰值人数已增长到约 12 人。甚至设计工程师也花费 49% 的时间进行验证。验证工程师将他们的时间分散在五项活动上:

- 47% – 测试计划

- 21% – 创建测试和运行仿真

- 15% – 测试平台开发

- 13% – 调试

- 5% – 其他

IC 和 ASIC 趋势表明,嵌入式处理器内核的数量正在增加,74% 具有一个或多个内核,52% 包括两个或更多内核,15% 具有八个或更多内核。到 2022 年,RISC-V 处理器占设计的 30%,比两年前增加了 23%。AI 加速器出现在 32% 的设计中。为了管理 SoC 设计的电源,我们发现时钟域的数量有所增加,平均数量为 3-4。

IC和ASIC趋势表明,嵌入式处理器内核的数量正在增加,因为74%具有一个或多个内核,52%包含两个或多个内核,15%具有八个或更多内核。2022 年,到 2022 年,RISC-V 处理器占设计的 30%,比两年前增加了 23%。AI加速器的设计占32%。

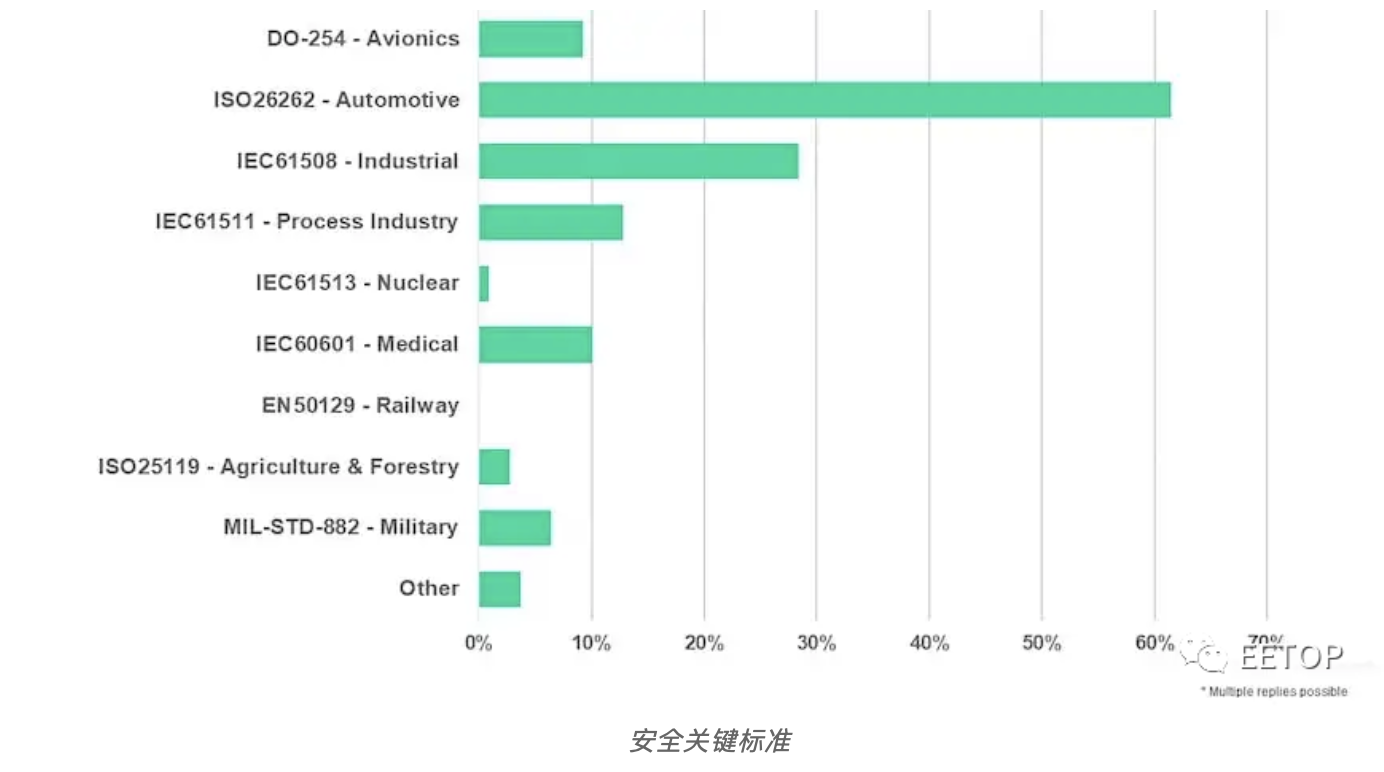

异步时钟域在93%的设计中占主导地位,因此需要更多的门级仿真和CDC验证工具。58%的IC/ASIC设计增加了安全功能,用于加密密钥、DRM密钥和处理敏感数据等。以下是安全关键标准的分布:

FuSa(功能安全)项目时间花在四项活动上:安全分析、安全架构和设计、安全需求、安全验证。这些加起来不到项目时间的 25%。

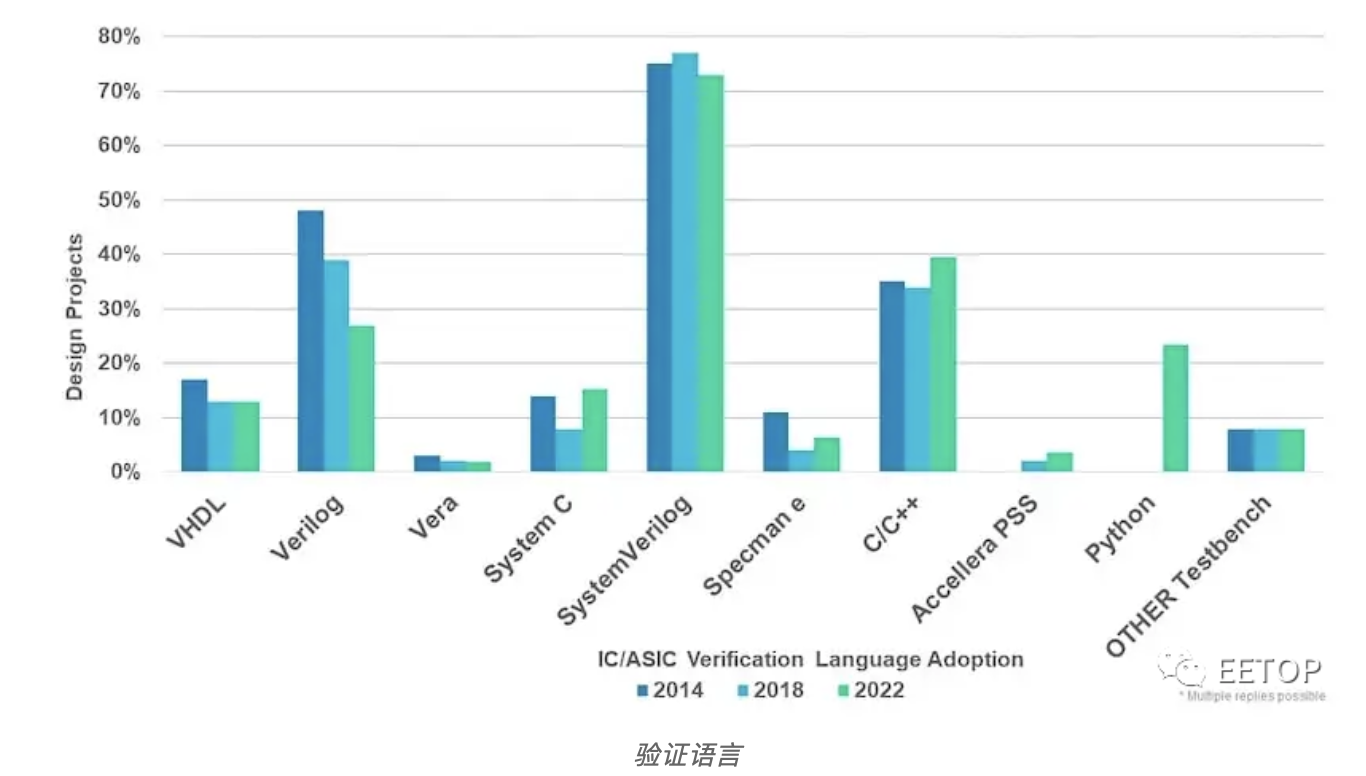

验证语言和方法分布包括了在 10 个类别的统计数据,其中SystemVerilog 的使用最多,而 Verilog 的使用减少,Python是一种新兴趋势:

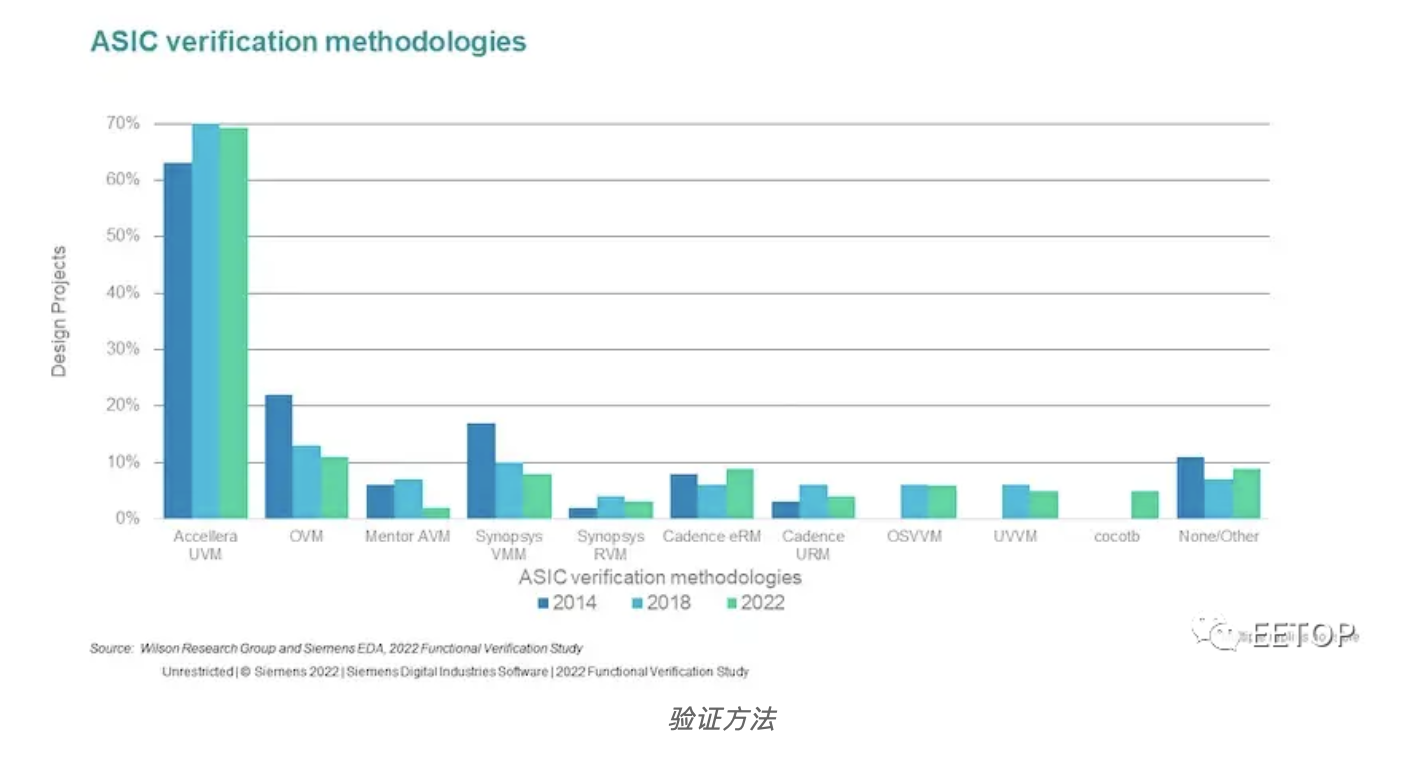

Accellera UVM仍然是最常用的验证方法,今年最近增加了基于Python的cocotb。

对于断言语言,SystemVerilog Assertions仍然占72%,OVL占15%,PSL占9%。35% 的设计使用了形式属性检查,自动形式检查增长到32%,这两个类别在过去8年中都增长迅速。

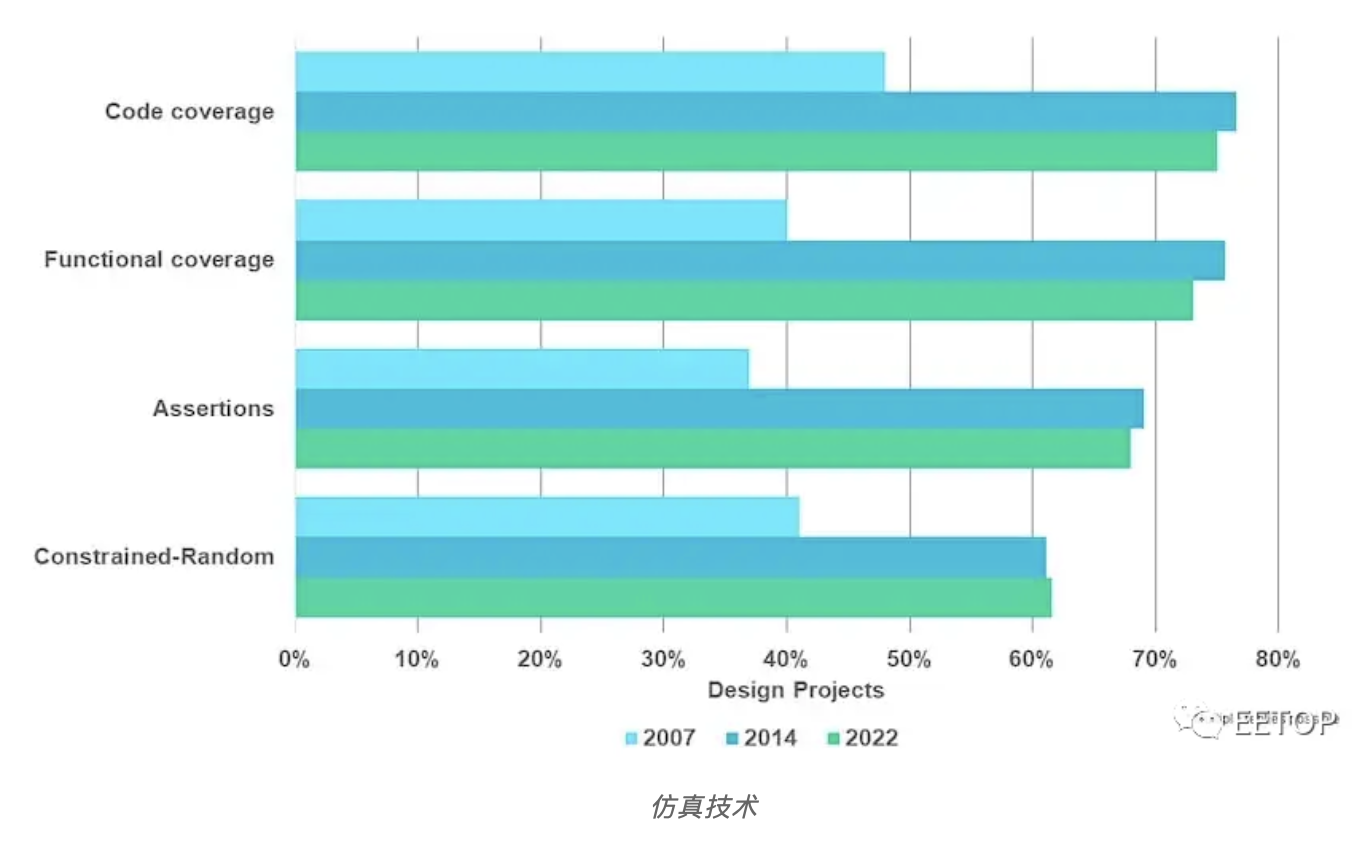

调查中跟踪了四种基于仿真的技术,因此在过去15年中没有增加新方法:

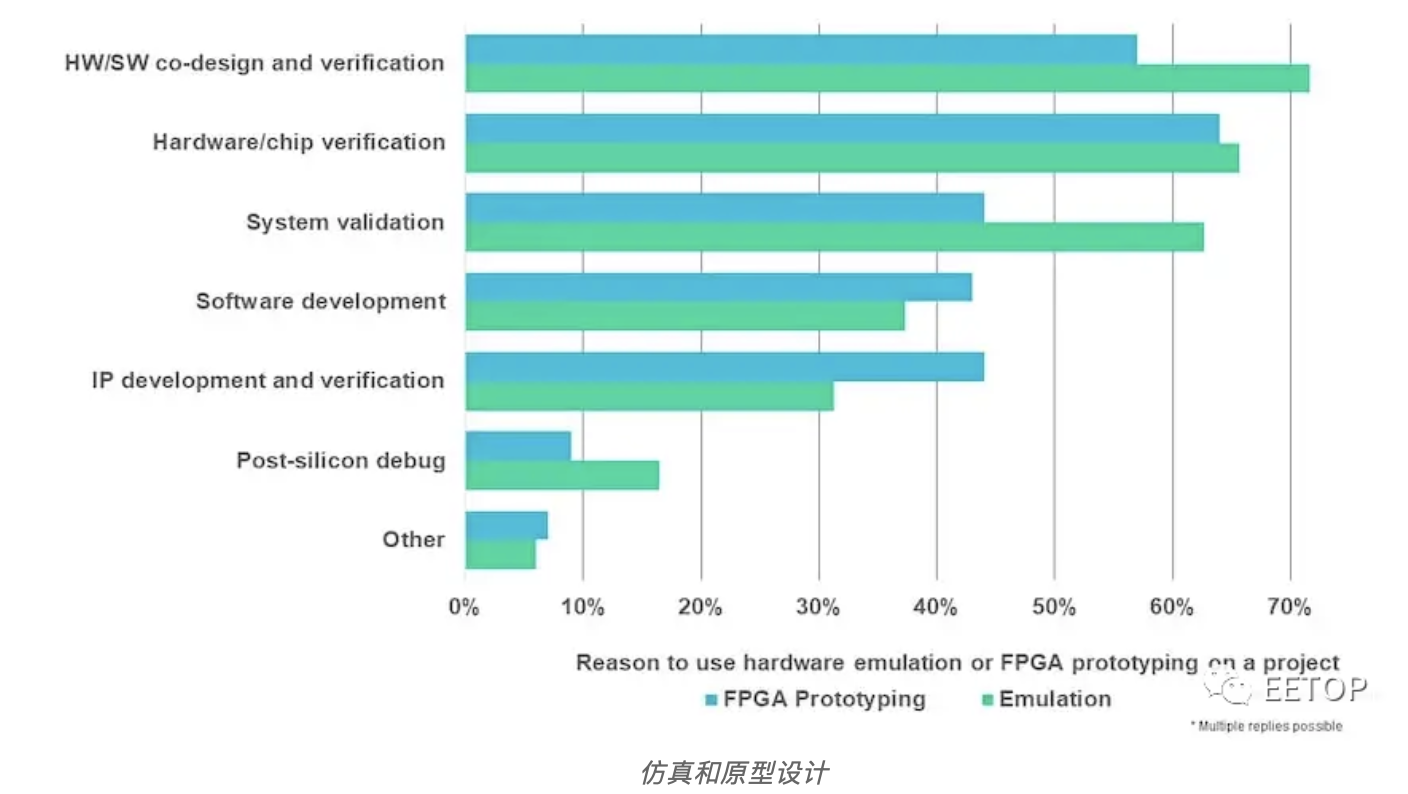

基于软件的验证受到速度和容量问题的限制,因此基于硬件的仿真和 FPGA 原型设计及时出现,通过运行实际软件和操作系统来帮助验证最大的 SoC 设备。使用仿真或FPGA原型设计的六大原因被列为最重要的因素,其中硬件/软件(HW/SW)协同设计和验证是最重要的因素。

仿真和原型设计最近的容量已提高到超过 10 亿个门,这还不包括存储器。

总结

功能验证对于了解新的电子设计是否符合规范、功能可靠并在第一片硅芯片上正常工作至关重要。设计和验证工程师都将时间花在使用多种语言、方法甚至硬件辅助平台进行功能验证上,以实现按时交付项目的目标。这份半年度报告包含丰富的信息,可帮助我们的行业了解IC和ASIC设计人员的功能趋势,然后以最佳实践做出回应,并让工程师了解如何更聪明地工作,而不是更努力地工作。

文章来源:EETOP

推荐阅读

- PCIe 6.0:在有损HVM通道中使用PAM4实现64GT/s的挑战

- Wi-R 一种全新的通信方式,让你的身体充当媒介!芯片已推出!

- 科普:DDR

- 用于探测中微子的超低温(液氩)ADC设计

- 在IC设计/验证中怎么应用ChatGPT?

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。