文章来源:阿里云开发者社区

作者:云言·云议

简介:因为X86及其CISC架构生态的封闭性,中国市场对未来处理器的选择,将是更开放、更模块化的RISC架构。 鲲鹏处理器就是符合这个潮流的创新产品和生态,将直面一系列挑战,和Apple一样赢得这场挑战,来扭转X86的封闭性的乾坤,创造出中国的处理器新生态。

一、前言:扭转x86乾坤的挑战

1、ARM:超越x86二选一思维

ARM基础设施事业部高级副总裁兼总经理Chris Bergey称,ARM想改变行业对部署基础设施的思维,每一个创新者都不应该被要求在性能与能耗之间进行抉择,ARM平台提供了两者兼得的最佳解决方案。

法国芯片公司SiPearl和韩国电子通信研究所( ETRI)的高性能计算(SoC)均可展现这些设计元素的优势,这被ARM看作是高性能计算的发展方向

ARM系列芯片之一Neoverse N2在安全性、能耗以及性能方面都有全面提升,并能为用户减少TCO的每瓦性能表现。相比于Neoverse N1,N2在保持相同水平的功率和面积效率的基础上,单线程性能提升了40%。

ARM芯片具备良好的可扩展性,可以横跨从高吞吐量计算到功率与尺寸受限的边缘和5G应用场景,并在这些应用中带来优于Neoverse N1的表现。例如,在云端上提升1.3倍的NGINX,在5G边缘应用上提升1.2倍的DPDK数据包处理。

2、Apple:推出惊人速度的ARM笔记本电脑

今年还有一个里程碑式的事件,就是Apple以惊人的速度推出了基于ARM的笔记本电脑。Apple从来不是一个拘泥于现状的公司,在其历史上,就曾经在短时间内抛弃了摩托罗拉转向Intel。但当时的情况是Powerpc日渐式微,而Intel明显的处于快速上升期。如果告诉一个人说现在的iMac装不了Win10了,有很大一批人可能都会犹豫。因此Apple当下的选择好像是冒了很大的风险的。

Apple与之不同之处在哪里呢,是有自己独有的优势,就是软硬件一体的高度控制能力,这也是它敢于叫板Intel的底气。由于IOS在庞大的电脑市场占比较小,目前还不能对X86构成什么威胁。但这次改变却透露了X86未来可能的隐患,这就是基于Apple强有力的执行力和软硬件整合力的推动下,在Apple体系中成功建立起移动、桌面和云的一体化,从而证明了ARM架构在泛云支持上的可能性。

这个杀伤力就很大。

这表明现在桌面和移动的几乎所有应用都可以迁移到ARM上,同时对应的云端应用也可以用ARM支持,这样相当于直接切入了X86全部的生态圈。

3、鲲鹏:扭转x86乾坤的挑战

因为X86及其CISC架构生态的封闭性,中国市场对未来处理器的选择,将是更开放、更模块化的RISC架构。

鲲鹏处理器就是符合这个潮流的创新产品和生态,将直面一系列挑战,和Apple一样赢得这场挑战,来扭转X86的封闭性的乾坤,创造出中国的处理器新生态。

因为鲲鹏采用ARM64架构,其RISC架构和x86的CISC架构有很大的不同,原来在x86处理器上运行健壮的程序,在ARM64上不稳定,开发人员随口说,ARM64处理器有什么问题吗?这个帽子扣的有些大,后来发现是自己代码搞错了,有个代码分支没有加锁,这部分代码还是新写的,并没有在x86上运行多久,只是问题没有暴露而已。这是一个乌龙,让ARM64处理器背了锅。

其实,应用程序很少看到ARM64处理器的架构细节,也很少能碰到处理器的问题。中间隔着操作系统和编译器,处理器架构相关的工作都已经适配了,跨体系结构移植代码的难度也没有预想的那么大。不能因为对ARM64不了解,就谈虎色变,问题还是问题,还是需要从问题本身出发,从现象到本质。

鲲鹏处理器基于ARM64架构,追求极致能效比,与x86处理器相比的优势更在于多核和乱序执行,在处理程序并行上也会遇到一些挑战。

全新构建一个生态本身,不是一帆风顺的,鲲鹏产业必须举着”补洞”的大旗,再困难也要往前冲,有些困难的挑战却不仅仅是锦上添花的事情,在ARM64上干成了,就不怕和x86比了。

本文主要讲一讲扭转X86封闭性的乾坤重大挑战之一:ARM64的指令乱序。

二、指令乱序执行:独特架构的先进特性

ARM以及芯片架构师都有共识,ARM64就是这样的,是允许指令乱序执行的,这是出于性能的考虑,这是架构特性,不是漏洞。网传苹果最新的M1处理器的乱序窗口达到600条。

但是,指令乱序的影响却给系统可靠性带来了风险,驱动模块,基础软件和应用软件都要做排查、设计优化。所以,这是鲲鹏生态各产品线切换到ARM64平台上的软件也要谨慎面对。

1、体系结构决定内存模型:X86强内存序,ARM64是弱内存序

为什么会有指令乱序,这确实是体系结构的内存模型决定的,并不是有人在忽悠我们。

2、X86强内存序: 写后读乱,读后读/写后写/读后写不乱

X86是强内存序模型,复杂指令集允许其运算指令本身支持内存访问,并允许非依赖的写后读指令乱序,其它非依赖的读后读,写后写,和读后写的指令都不会发生乱序。

3、ARM64弱内存序: 精简指令集把访存指令和运算指令分开了

ARM64是弱内存序模型,因为精简指令集把访存指令和运算指令分开了,为了性能,必须允许几乎所有的指令乱序,但前提是必须遵守依赖约束和排序约束,不影响程序的逻辑和正确性。

所以,ARM64上没有依赖关系的读后读,写后写,读后写,和写后读都是可以乱序执行的。

这听起来很匪夷所思,那程序代码还能保证正确吗? 搞不定的问题都可以扣上CPU乱序的帽子吗?

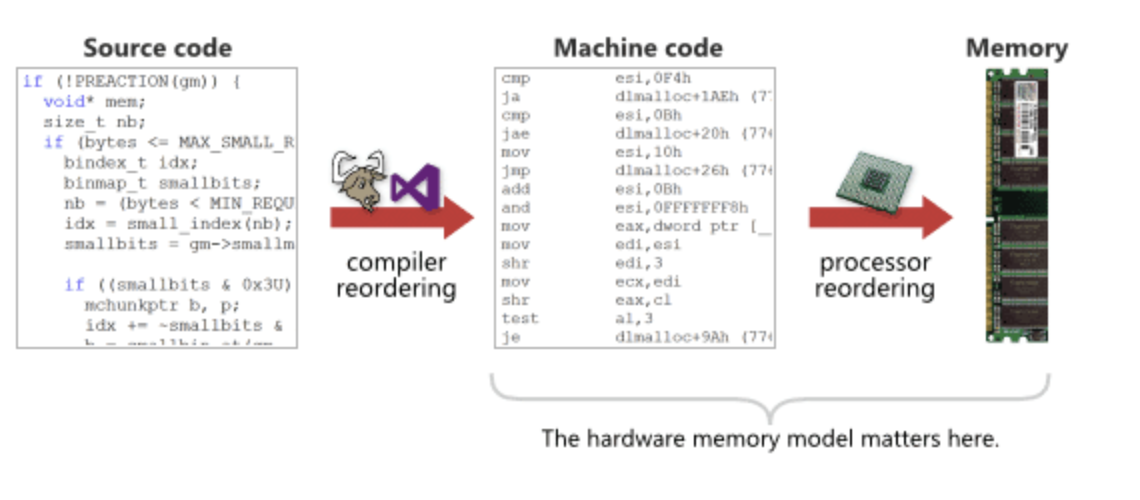

这其实呢,在指令乱序前还得知道编译乱序,ARM64处理器并不是直接面对程序代码的,而是面对机器代码,或者说汇编指令。

由高级语言编写的程序,如C语言,首先通过编译器的编译转换为汇编指令,编译器会根据ARM64处理器的流水线特点,合理安排汇编指令的顺序,目的是最大限度的发挥CPU流水的并行能力。这也没有什么可怕的,编译器一定会在保证程序正确性的情况下,合理调整汇编指令的顺序。

特别的,在源代码中内联汇编指令时,这个外部额外插入的汇编指令,要告诉编译器不要优化指令顺序,需要使用“__asm__ __volatile__("": : :"memory") ”的编译提示。编译阶段的乱序不是我们关注的重点,而且这部分极少出错。我们仍然回到CPU的指令乱序特性上来。

三、并行流水:10000米高空的观察

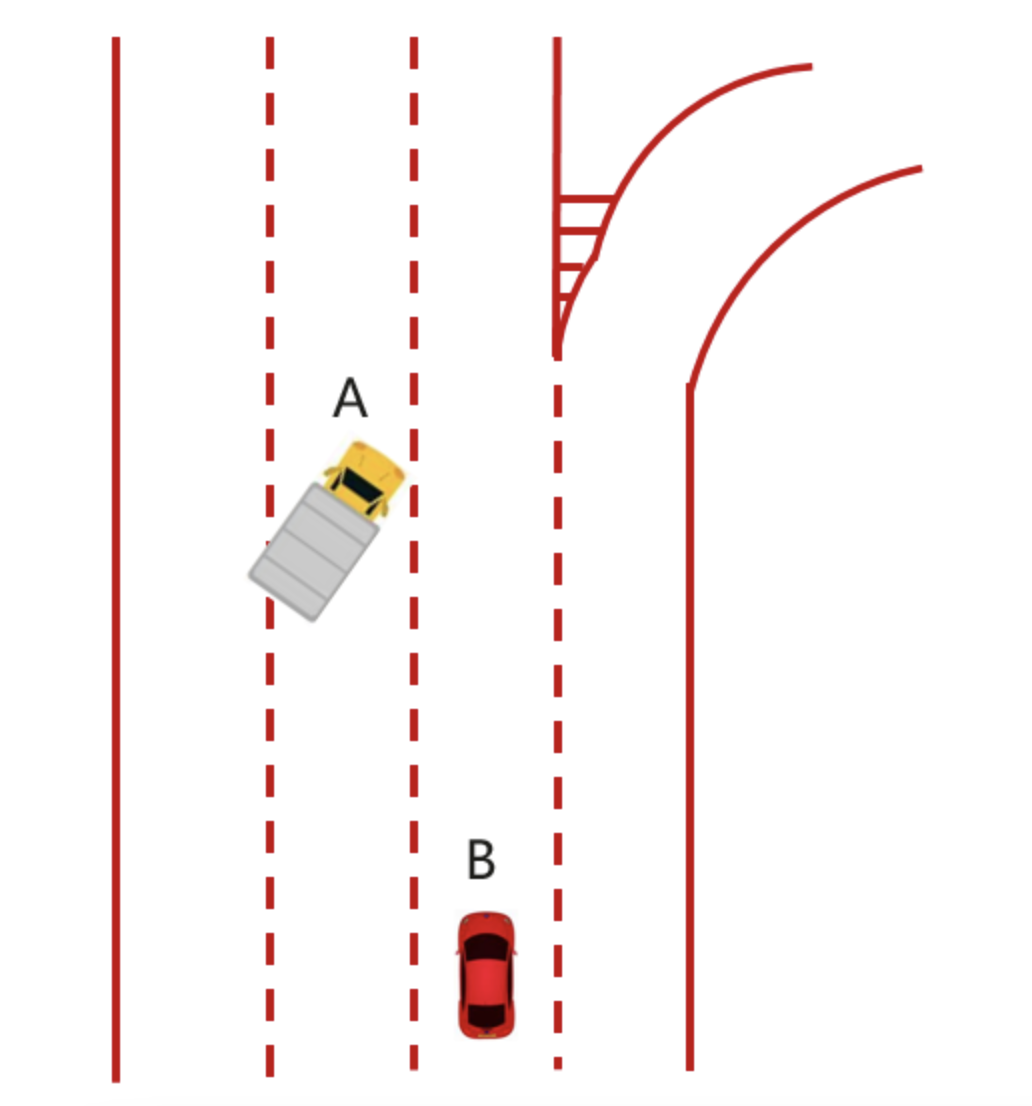

生活中,特别是高速路的道路设计和CPU的流水设计有一点相似之处。高速路设计了并行的行车道和超车道,是允许超车的,这样可以保证高速路的高效通行和最大车流量。

经常开车的同学,肯定会为高速路上在行车道或者超车道上龟速行车的小汽车大为光火,也许你超车时还不忘瞟一眼,确认一下是不是女司机,其实多数是新手男司机才这么霸道。

1、ARM64:多个并行流水部件,支持超标量

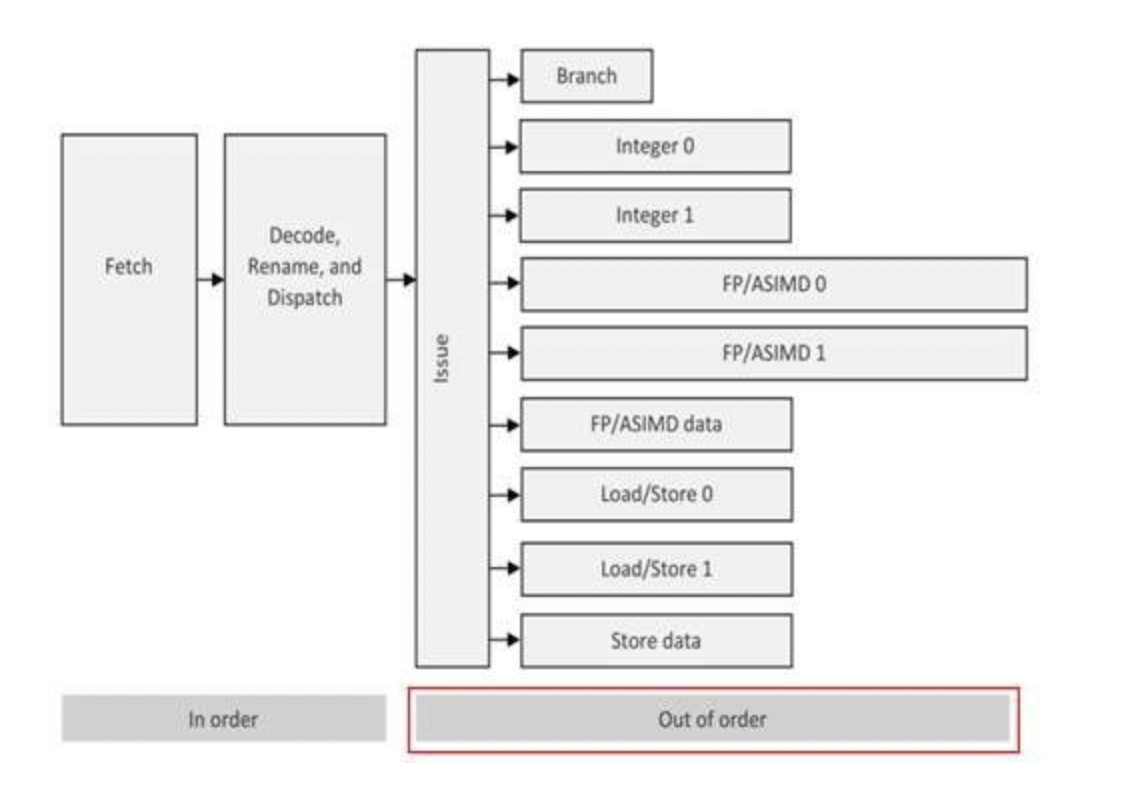

ARM64设计了多个并行的流水部件,支持超标量,可以一个指令周期分发多条指令,实现最大程度的指令并行。

2、流水第一二阶段:串并转化、保乱皆有序

流水的第一阶段包括指令提取,译码和分发,这部分是保序的;

一旦到流水的第二阶段,执行指令流“串并转化”后,指令一旦分发到不同的并行流水部件中,它们的执行顺序就是乱序的了。有依赖的指令会放到同一个流水部件,先进先出方式排队,防止乱序执行。

关于流水线的设计是如何保证指令并行的正确性,详细的微架构分析,cache一致性原理等以后解释,此处直接跳过。

高速匝道口事故:A变道是否影响B正常行驶

高速路上经常发生事故的地方是匝道口。当左侧超车道上的车辆A往右侧匝道横向慢速变道,往往导致后方行车道上正常行驶的车辆B刹车不及,导致追尾碰撞。当然,如果此段高速路上只有车辆A,或者后面的车B根本看不到踪影,或者车辆A占用的车道和车辆B行驶的道路不相关,那么车辆A怎么慢吞吞的变道都没有关系。所以,发生事故的条件之一就是车辆A的变道是否影响到车辆B正常行驶。

文章来源:阿里云开发者社区

作者:云言·云议

推荐阅读

更多Arm服务器相关技术及移植干货请关注Arm服务器专栏。如要加入Arm Server微信群,请添加极术小姐姐(微信id:aijishu20)备注Arm服务器邀请加入。