1. Equality operators

Equality operators有三种:

- Logical equality:==, !=,该运算符中如果运算数包含有x/z态,那么结果就是x态。只有在两边的bit都不包含x/z态,最终结果才会为0(False)或1(True)

- Case equality:===, !==,该运算符中会把两边运算数的x/z态都考虑进去,最终结果肯定是0或1

- Wildcard equality:==?, !=?,该运算符的右边是wildcard匹配,右边操作数的x或z bit对应于左边的bit可以为任何数字,但左边的x或z不能被认为是wildcard。因此该运算符的结果可能有x/0/1三种结果,如果左边的x/z态不能被右边的wildcard匹配,那么结果就是x态,如果左边的x/z态会被右边的wildcard匹配,那么结果就为0/1

2. short circuit evaluation

只有&&, ||, ->, ?: 可以用short circuit evaluation方法,该方法如下:

第一个operand表达式肯定会被evaluated,对于&&,如果第一个operand结果为false,那么后续的operands就不会evaluated,对于||,如果第一个operand结果是true,那么后续的operands不会被operands。

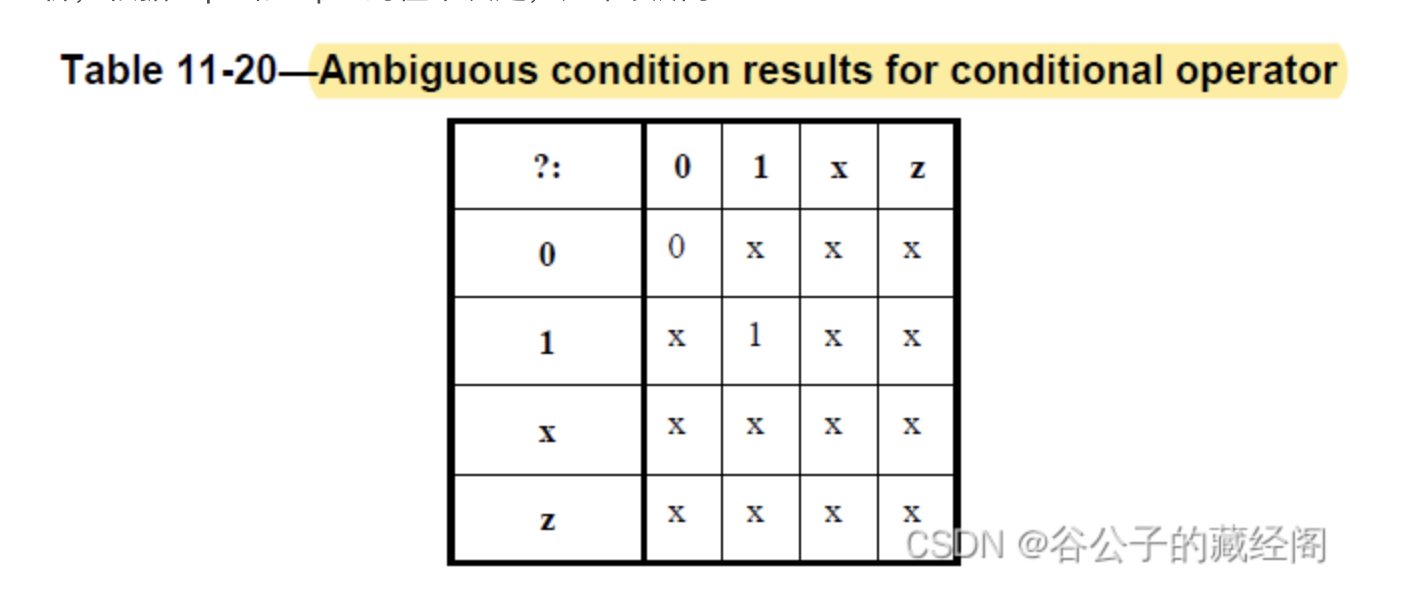

对于条件运算符(cond_predicate ? expr1 : expr2),如果cond_predicate为True,那么第一个expr1会被evaluated如果cond_predicate为False,那么第二个expr2会被evaludated。如果cond_predicate为x或z态,那么将具体情况具体分析,根据expr1和expr2的值来决定,如下表所示:

3. shift operators

Shift operators有两种类型:logical shift operators(<<, >>)和arithmetic shift operators(<<<, >>>>)。对于左移操作符<<和<<<,空出的bits位补0。对于右移操作符>>和>>>,logical right shift移出的空位bit补0;arithmetic right shift操作如果是对unsigned变量移位,那么也是补0,如果是对signed变量移位,那么需要根据signed变量的最高位来移位,如果operand中含有x/z态bit,那么结果是unknown的。

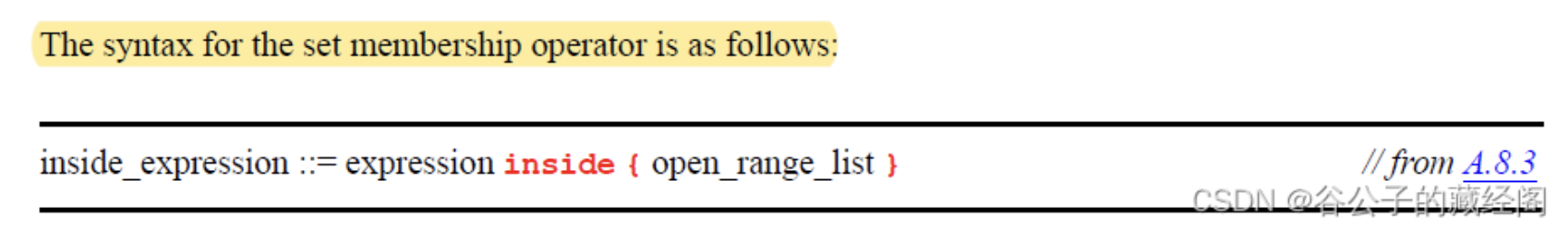

4. set membership operator

inside左边的expression是singular expression。inside的右边是用逗号分隔的expression或range列表,如果expression是unpacked array,那么它将自动会被展开直到为singular value。open_range_list的value可以重复,所以values和value ranges可以有overlap。

对于非整形expression,inside是采用logical equality(==)运算符来比较的。对于整形expression,inside是使用wildcard equality(==?)来比较的,所以range_list中expression含有的x/z bit不参与比较,但左边的x/z仍然是需要比较的。

inside没有匹配到相等的expression时,如果一些comparison里结果时x,那么将整体返回1'bx。

inside中range的指定时采用[low_bound : high_bound]的方式,$可以可以用于代表左边expression中最小或最大值。如果[:]中左边的值大于右边的值,那么该range会被认为时无效的,没有包含任何value。

5. vector bit-select and part-select addressing

bit-select是从vector、packed arrary、packed structure、parameter或concatenation中选出特定的bits。bit-select或part-select对scalar或real variable或real parameter进行操作是非法的。

有两种类型的part-select:

- non-indexed part-select:使用vect[msb_expr:lsb_expr]格式,msb_expr和lsb_expr必须是整型恒量表达式,第一个expr应该比第二个expr寻址到更significant bit。

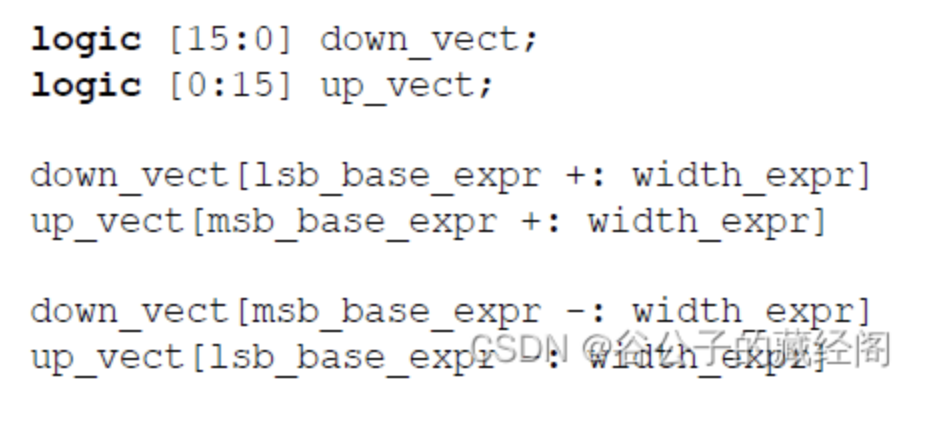

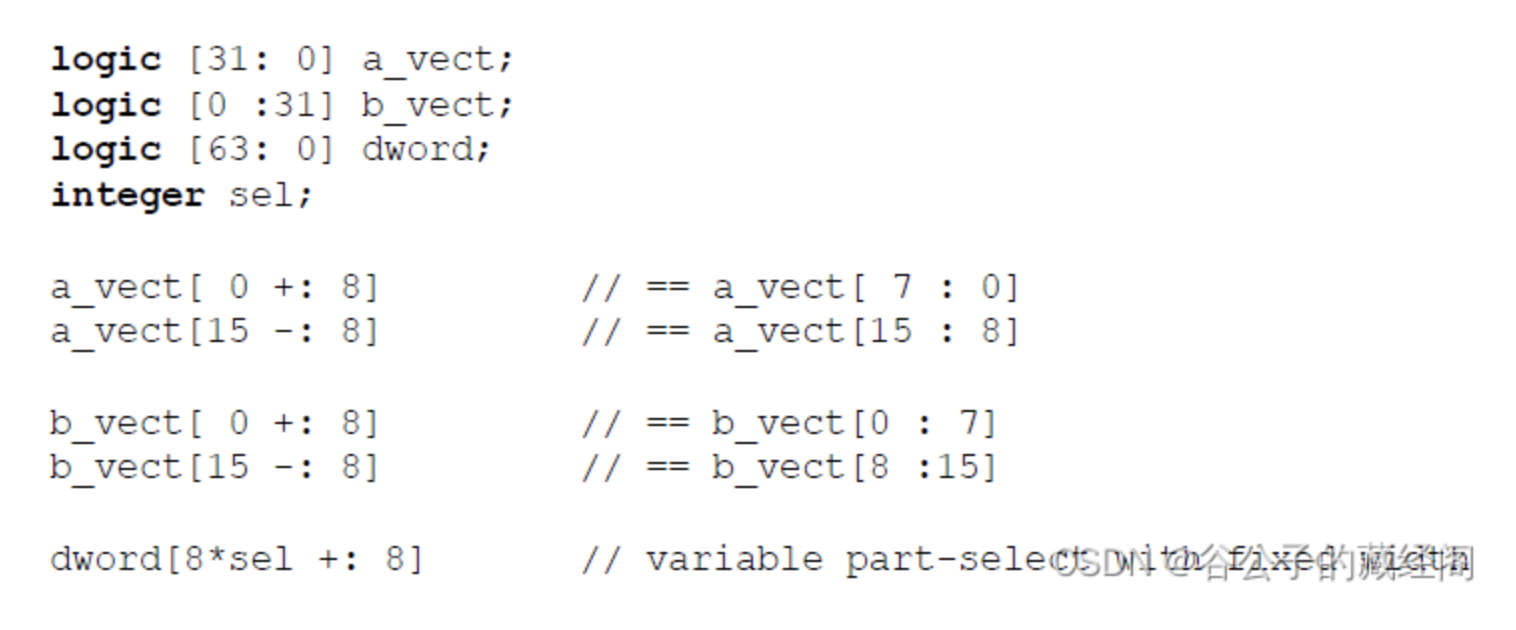

- indexed part-select语法如下:前两个选择bit从base开始,并逐渐按bit range上升,后两个选择bit从base开始,并逐渐按bit range下降。

example如下:

6. Steps for evaluating an expression

expression的评估步骤:

- 基于sv的规则确定expression的size;

- 基于sv的规则确定expression的sign;

- 将expression的size和type传递给context-determined oprands

- 将type和size一直传递到simple operand级别。Simple operand也就是最简单的操作数了,不可以分隔为更下一层的operands。

7. Steps for evaluating an assignment

assignment的评估步骤:

- 决定右手边的size

- 如果需要,将右手边的size扩展

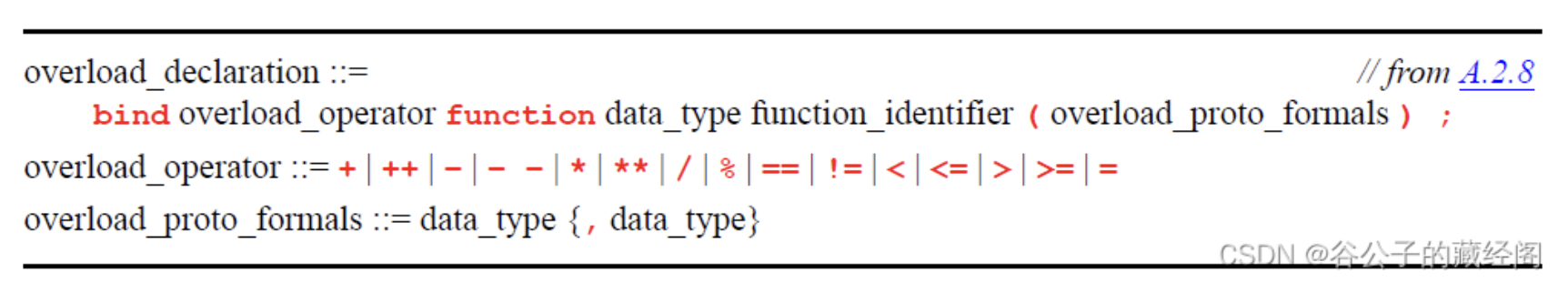

8. operator overloading

operator可以使用overloading的方式增加额外的功能,例如实现unpacked structure的加减法。

被bind的operator可以使用argument data types来匹配正确的bind function。可以被overload的operators有arithmetic operators、relational operators和assignment。

overload的scope的visibility与data declaration一样的。

例子如下,这个功能还挺有意思的。

作者:谷公子

文章来源:CSDN

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。

迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。