众所周知,在prePlace阶段打完Power后,需要使用APR工具把网表中存在的例化完的instance来全 局放置在core内,这个布局阶段(place)会暴露出设计Case在不加任何约束下按工具默认的global density等设置摆放cell所存在的风险。

实际上在后端范围,工程师通常提到的高风险模块指的就是congestion较高的模块以及时序风险较 高的模块,这两者实际上都和place有着千丝万缕的联系,前者可能是因为place阶段不合理/面积切分不 合理导致局部绕线资源紧张,后者则有可能因为place的原因使得局部density过高导致timing eco阶段 hold插爆引起不能修的short drc。

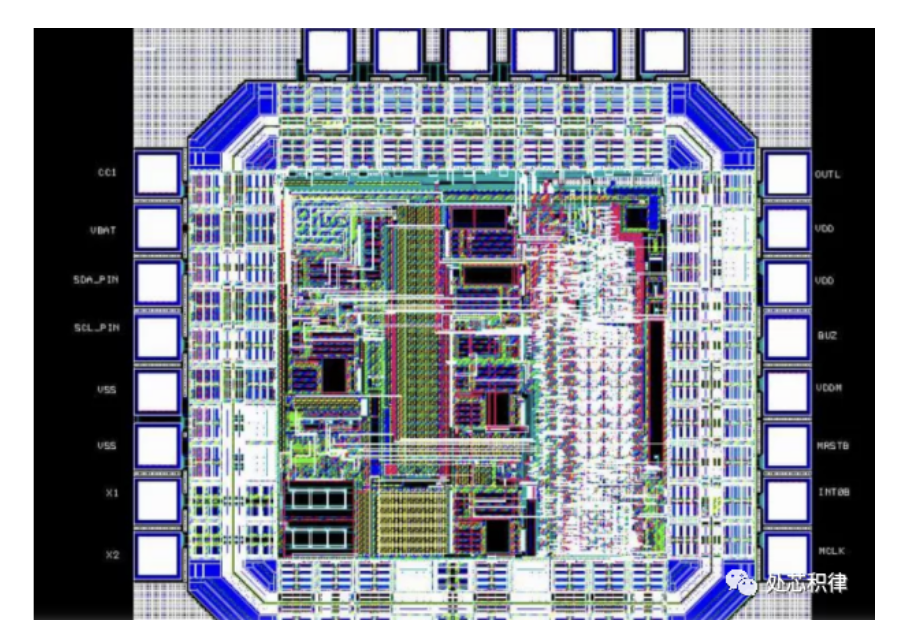

这篇文章小编就来以APR placement flow为例,分析工具在place阶段到底做了哪些事情,并且结合 项目心得,讲述几种常见的解congestion的方法和思路。

实际上placement不止和route最后的drc结果息息相关,更是和下个阶段的cts时钟树密切相关,一个 优秀的placement,摆的寄存器的位置比较合理/紧凑的话可以让cts解drv的时候线长减短,进而减少很 多为了解transition而插的INV,进而一定程度上优化时钟树长和skew。

在数字电路中,单元的放置是很规范的,std cell的面积都是site的整数倍,而row是由site大小决定 生成的,std cell也通常为一倍/二倍row高度,对应的std cell也会snap到row上放置,其实从综合工具 DCG看初始状态这些cell全部都是堆叠摆放的。而placement最重要的任务,就是把这些cell摆好,不能 有Overlap,不能有legalization的问题,不能有FE DRC。这就很类似于一堆散乱的乐高积木,我们要把 它一个个的在地上(core row)铺好,但是又要摆放的符合前端代码(RTL)关系。

上述内容就是指导innovus进行block placement的基础flow了,由注释可以发现主要包括设置place mode;设置opt mode,设置OCV derate参数加严时序,add_tie_cell来钳位住logic 0/1的Pin,一端接 pg net,一端接constant pin;进行Place以及Place_opt操作;存完db后,报timing以分析时序,也许 有些ICer会疑惑PlaceOpt怎么就一个place_opt_design就一笔带过了?事实上,APR布局布线的 PlaceOpt阶段工具是其中的一个重要步骤,主要负责对芯片的物理布局进行优化,以满足电气约束和布 局规则。

PlaceOpt阶段工具的主要作用如下:

- 优化芯片的物理布局:PlaceOpt阶段工具可以通过对芯片的物理布局进行优化,使得芯片的面积更 小、功耗更低、性能更好。PlaceOpt阶段工具会针对芯片的电气约束和布局规则进行优化,以达到 最佳的布局效果。

- 解决布局冲突:在布局布线的过程中,可能会出现布局冲突的情况,比如两个器件之间的距离过 近,或者某些器件之间的间距不符合规定等。PlaceOpt阶段工具可以检测这些冲突,并进行解决, 以保证芯片的物理布局符合规范。

- 优化时序和功耗:PlaceOpt阶段工具可以通过优化芯片的物理布局,来改善芯片的时序和功耗。例 如,可以通过减小器件之间的距离,来缩短信号传输的时间,从而提高芯片的时序性能。又如,可 以通过合理的布局,来降低芯片的功耗。

- 生成布局报告:PlaceOpt阶段工具会生成布局报告,其中包括芯片的面积、功耗、时序等信息,以 便设计人员对布局结果进行评估和调整。

需要注意的是,PlaceOpt阶段工具只是APR布局布线过程中的一个步骤,它需要与其他工具配合使用, 才能完成整个布局布线的过程。例如,在PlaceOpt阶段工具之后,还需要进行时钟树合成、布局布线、 后仿真等步骤,以完成芯片设计的整个流程。那么问题来了,如果在place完毕后,工程师在查阅log/报 告时候发现局部区域overflow(congestion)确实很大,存在很大的绕线风险时候一般怎么解决呢?

- 可以通过调整flooplan来解决,通常MEM的沟道/出PIN位置附近会有纵向/横向的overflow,这种 congestion通常可以通过调整沟道宽度/MeM的相对位置(使得走线规整)解决

- 打PlaceBlk,对于cell density过高的区域可以加partitial place blk来降低density,可以密度逐层 递增,打多层

- 增加keepout margin,通过设置Pin keep out来给PIN足够空间出

- 打routing blk,对于Macro周边底层signal如M2 M3等出PIN导致的signal overflow尤其是拐角 处,在周边区域走线资源充足的情况下,可以对堵塞区域设置对应层的no_signal rblk,route完毕 后删掉,以免报drc错误

- 设置padding,对于高Pin Density的区域,经常有AIO,MUX,MBIT等多Pin std cell,虽然cell的 密度不高,但是走线出Pin太多,这种情况可以通过设置一类lib cell的padding来解,通常可以加 1~2site的距离,不够再加,注意,这样操作很有可能会影响timing,需要谨慎使用。

- merge bit,对于寄存器导致发生overflow的区域,工程师可以设置Merge bit以减少时钟PIN

- 修改RTL代码,有可能是逻辑设计不合理,MUX等多PIN逻辑太多了,后端确实解不了

- 修改Power Plan,对于H overflow,则加密纵向走线,放松横向Power走线,反之加密横向Power 走线,放松纵向Power走线

- 规划std cell,整理signal 线,在Power net高层空间允许的情况下,走高层NDR来释放风险

- 少部分的signal线,可以自己手动拉线走高层/或者换层

- 最终杀招,和项目经理商量要不要增加点面积,或者砍点macro放到其他模块去,H overflow就增 加高度,V overflow就增加宽度

我是处芯积律,感谢大家阅读!

作者: 处芯积律

文章来源:处芯积律

推荐阅读

Questasim设置仿真随机种子(random seed)

一颗芯片的自述:从立项、流片、验证到发布管理的心路历程!

原型验证过程中的ASIC到FPGA的代码转换

更多IC设计请关注IC设计技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。