作为一名芯片工程师,从毕业出到步入公司的第一天开始,需要完成一次明显的转变,随着工作的日益开展和项目推进,个人能力的也得到了潜移默化的提升,当我们回看个人的知识/技能成长的曲线时,可能会发现很多的发生和变化,和自己当初的规划不太一样,再向前看,也会发现未来的要求和我们手上的技能貌似还有很大的差异,那么到底怎样的学习曲线时合理和科学的呢?笔者的一些浅显见解这里想和大家一起分享/探讨一下,不当之处也请各位指正。话不多说,ICer GO!

成长欲望

每个人都渴望长大,成长,不仅仅是身高/相貌,同时也是技能和知识,自我实现的不断突破 ,当然,这也是你的快乐源泉(内啡肽的来源之一)(摘自: 怎么获得更多的内啡肽?)

如同校园时期的你,解决了一个难题,完成了考试的附加题,获得了成绩以及同学们的点赞和好的排名;工作中你一样需要做类似的事情,来表现你的价值,作为芯片工程师可能是:用自己的算法实现了一段卷积的verilog的编写;或者使用UVM完成了CPU claster的互联互通的验证;抑或是一个TCL脚本完成了DFT链的手动微调等等,所有总总,拨开表象,各位同学还是在“做题”。

学习基本知识,掌握基本理论,然后通过学习现有的流程,脚本,文档,在一个有基础的平台上,用自己的code完成一个又一个的小任务,直到把项目胜利TO出去。当回片后,你的工作结果被芯片测试认可,一个悬着的心也就落了下来,Yes, I Can!。恭喜你,在螺旋楼梯上你又上了一层。

对应的,升值加薪等等物质的变化,让你产生了除过内啡肽快乐外,也有了可以向家里/女友报喜的硬邦邦的实物。

这就是简单的通过项目的成长曲线,拥有以下几个要素:

- 基于项目

- 协同合作

- 个人专注自身业务/工作

- 整体成功方能体现个人成功

后面的事情更是相像,不断地盘旋上升,直到永远。

个人价值也在逐步放大,对自己的自我认同感也在逐步加强。把技术搞明白,把活干好,别掉链子,慢慢就融入到了你的血液里边,这时候又诞生一个标准地技术人员!

平台和个人

芯片设计是一个庞杂的工程类项目,业务线条比较长,基本上每个人都在赶工期,非常忙。但是很少地项目是从零做起,就算是新项目,很多IP资源,EDA流程之类的也是会提供的,当然,最终还是离不开人,因为人才才是公司的核心竞争力。这里需要把成就项目的因素剥离出来看:偏向硬件的平台,和偏向软性的人力。

平台价值

简单的事情靠创意,复杂的工作靠流程。芯片设计显然属于后者。无论是前端/中端/后端/DFT等等,每个阶段都是有一套独立的流程。什么是流程:流程就是一个规避个人错误和加速产品的规范。如果说公司搭台工程师唱戏,那么这个流程就可以简单看作是这个戏台。铁打的营盘流水的兵,这个芯片设计这个营盘里边有一部分也就是这个流程。

越是大公司,越是重视流程,基本流程也都是silicon proven的黄金宝典了。这点看看国外大厂或者海思,中兴就能感觉得到。如果考虑后端,那么流程里边也可以根据不同的fab/node进行区分。

由于芯片设计过于复杂,流程也不是从零搭起,目前流行的做法就是基于EDA工具进行搭建。

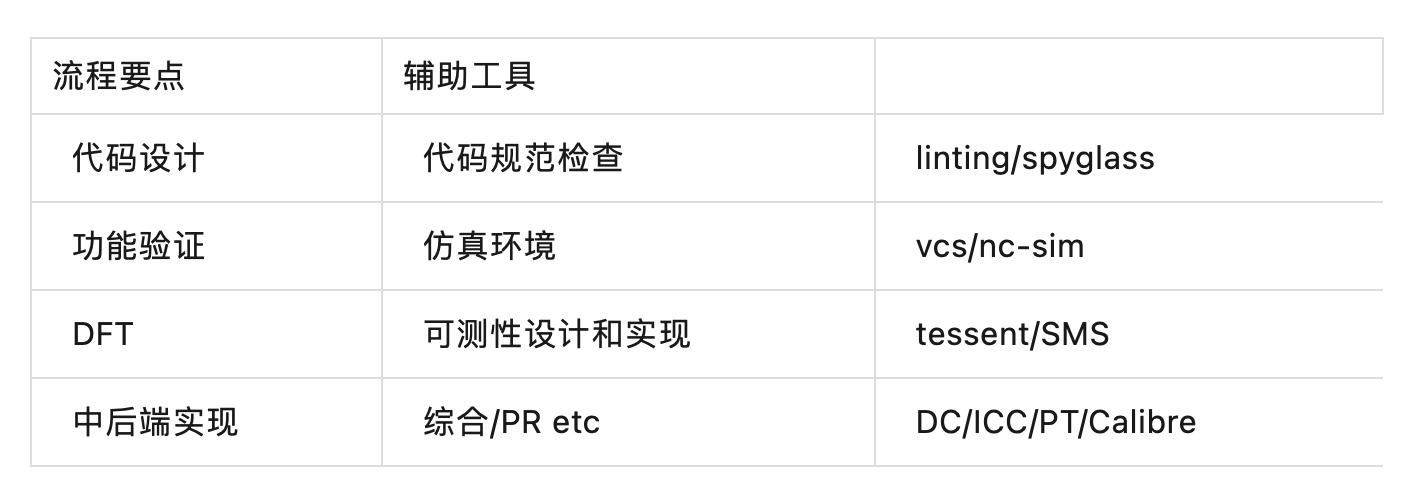

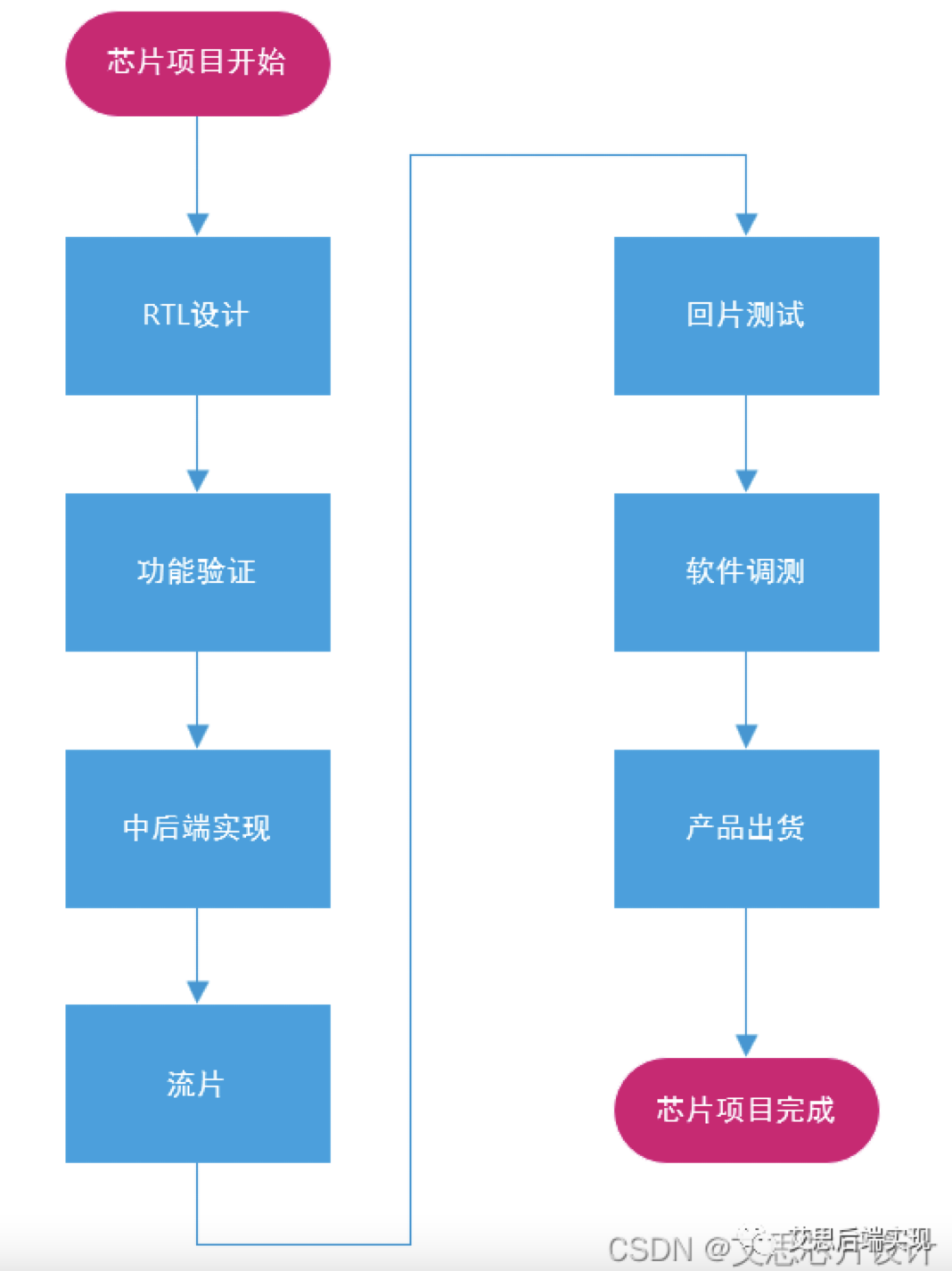

设计步骤

以上种种都是EDA公司提供的标准工具,用户如果想把这些工具用起来,是需要在每一个工具进行流程搭建的,大概示例如下:

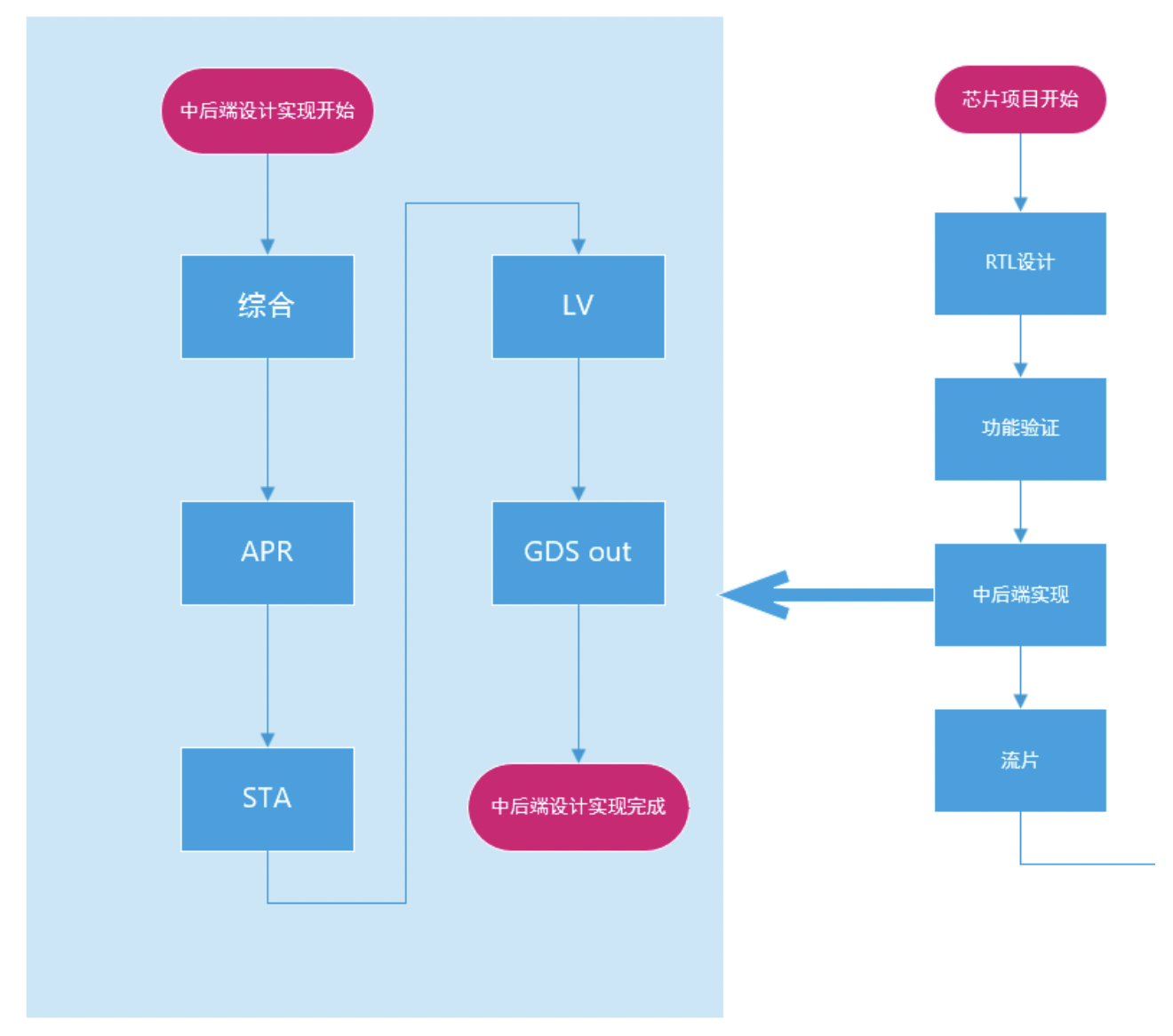

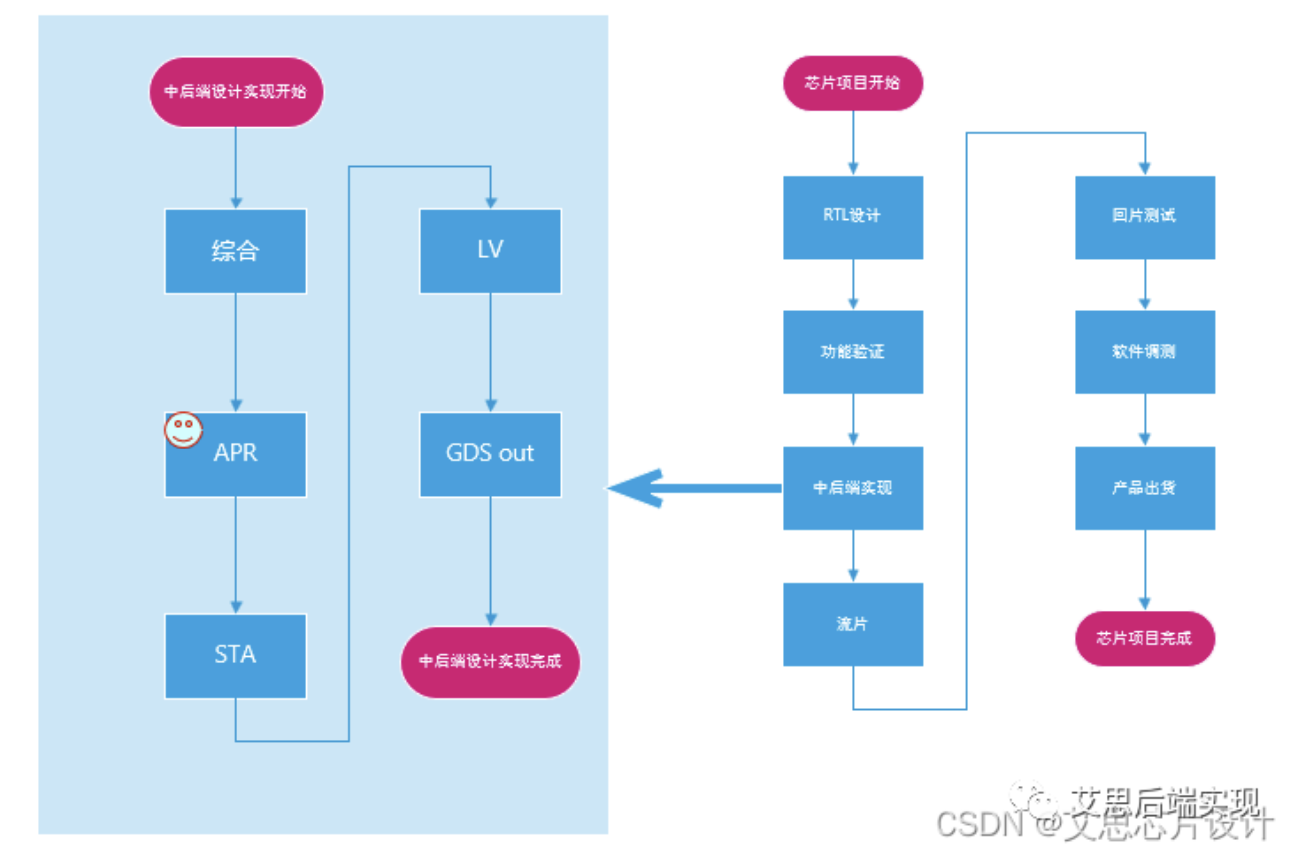

如果将其中的一个步骤展开,大概是这样的一个图解

但是,问题来了,where area you?

OK,找到了,恭喜你,你在做APR!如果看全貌,工程师哪里实在给公司打工,完全是在给流程打工

所以,严格一点来看,项目的技术构成应该是:工程师使用流程上完成项目任务。

但是注意,由于每一个项目都在流程上要走一遭,所以,流程的力量会变得越发庞杂和强大,自动化也会越高,收敛性也会更强。如果有下面一个简单公式表达:

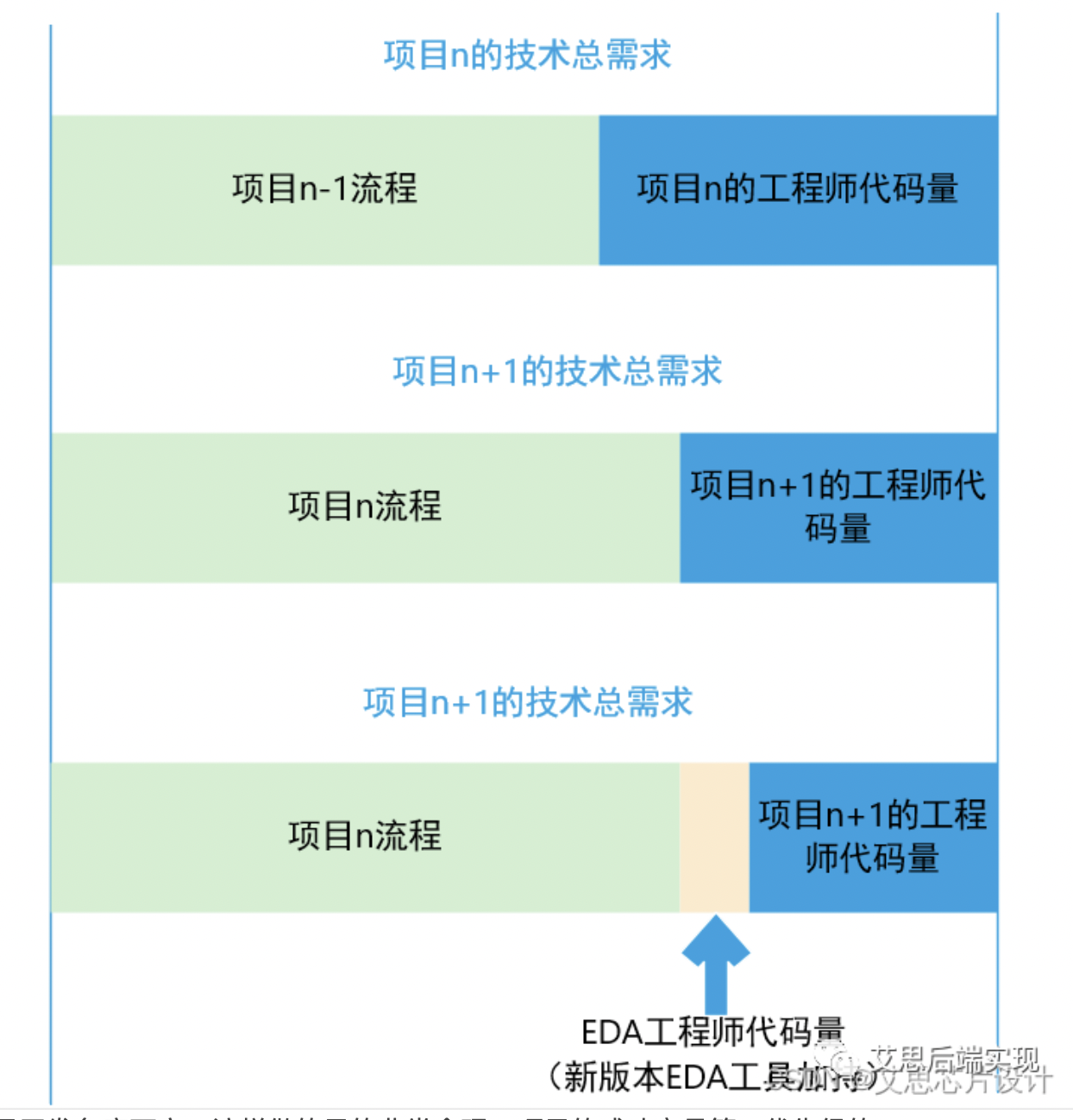

项目技术总需求 \= 流程 + 本项目的工程师的代码量

那么,每当项目完成后,工程师的代码量就会打包(archive)到流程脚本,为了未来可以做更大更稳定的项目,所以可以看到,一个第n次的项目的工程师的开发量就是:

项目n技术总需求 \= 项目n-1的流程 + 项目n的工程师的代码量

随着设计越来越复杂,流程的重要性不言而喻,这也是目前各大EDA公司的重拳出击的地方,更何况最近还带上了AI一起玩,所以可见,当下和未来的趋势必然是,工程师的代码量会被流程吞噬(在和EDA公司的工程师做拔河?),

从项目开发角度而言,这样做的目的非常合理:项目的成功率是第一优先级的。

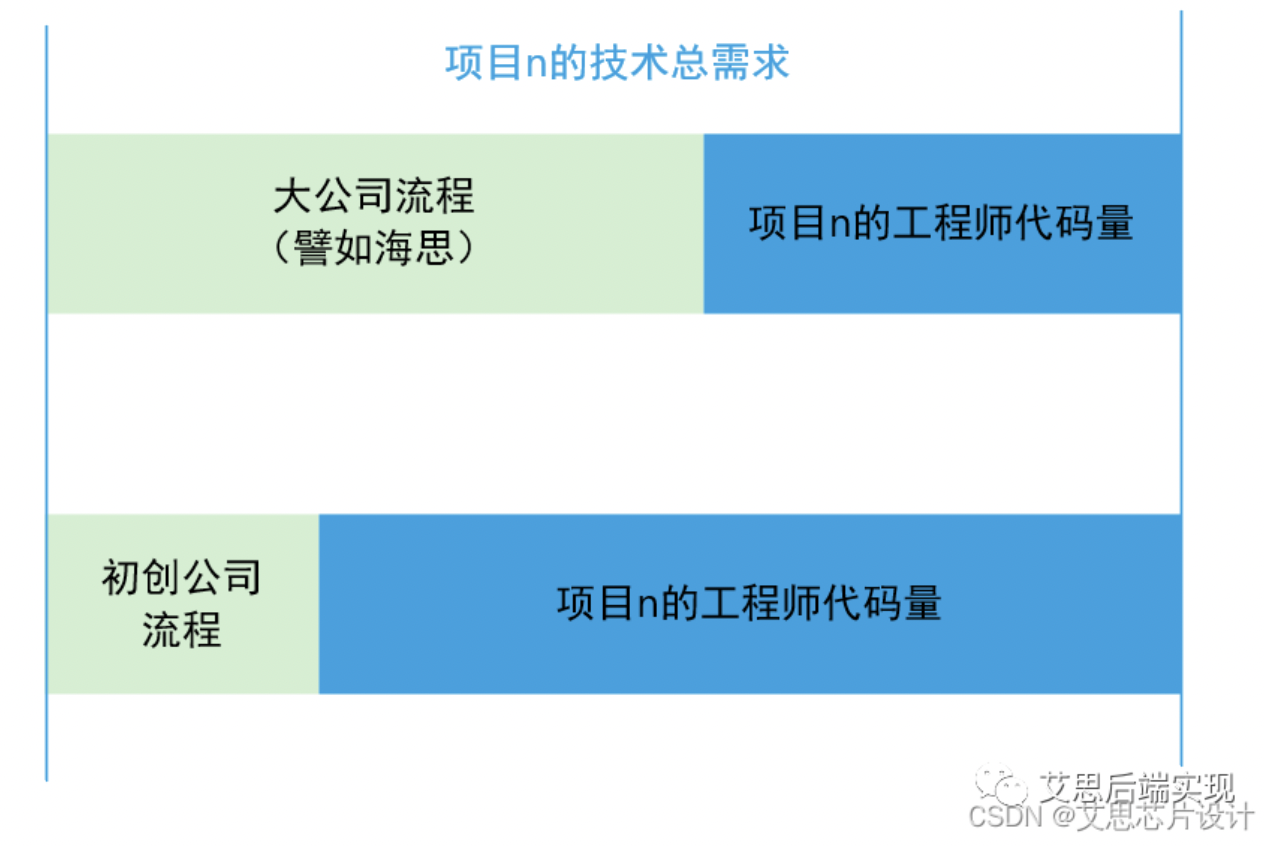

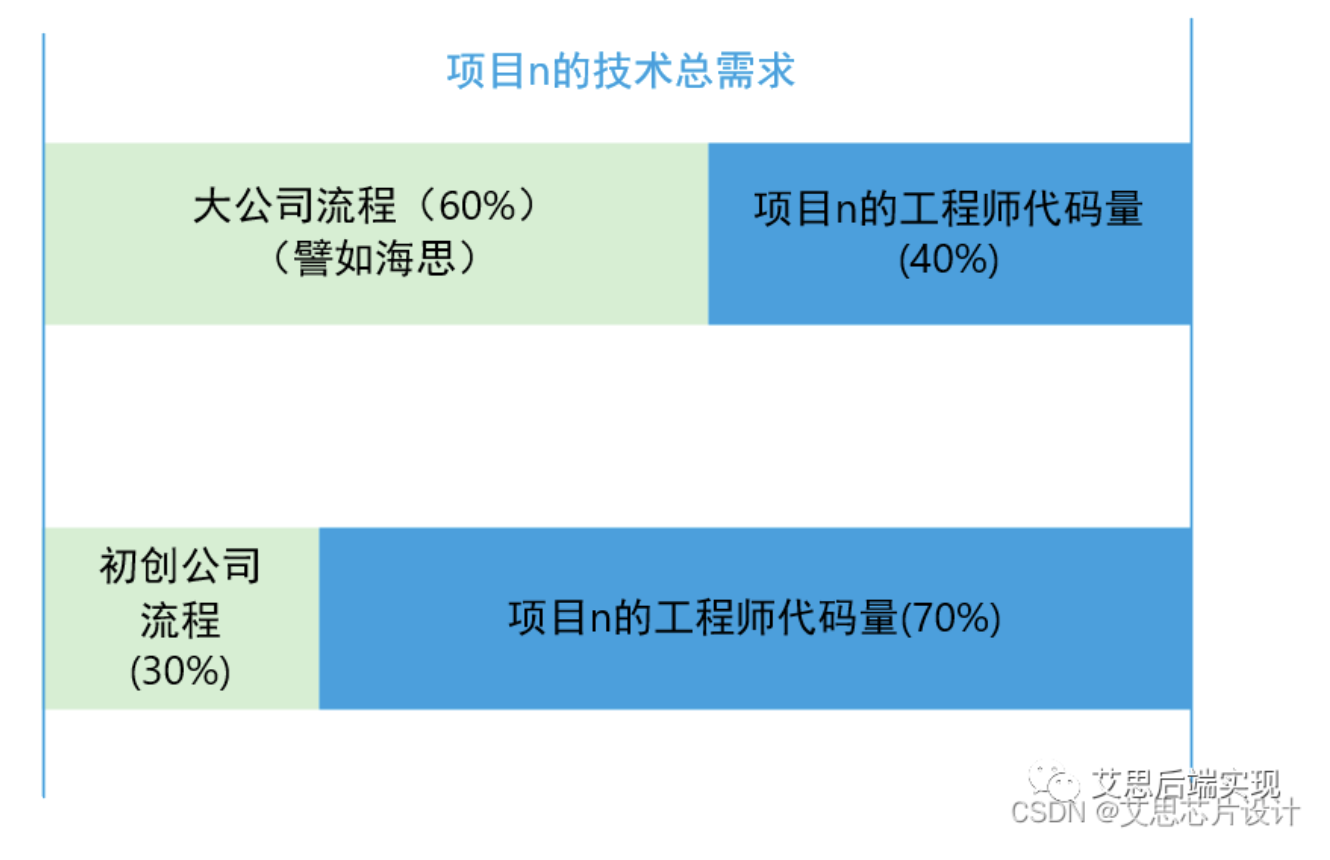

如果把这个模型按照公司诚实度来比对,那么同样的项目规模大概是这样的:

看起来总代码量类似,那么初创型公司何以硬刚老牌公司,答案是不能,这个模型可以细化如下:

项目n技术总需求 \= 项目n-1的流程*准确率 + 项目n的工程师的代码量*准确率

由于流程的质量/完备性远远高于人工,所以最后折算下来,同样的工程师,在新公司的流程里很难做出同样质量的项目,这个不是人的问题,这个是平台建设的问题。

在复杂工作环境中的项目,流程的价值远远大于人的价值,这仅仅是从EDA自动化的角度看,如果从IP,PHY,coding等角度看,这个现象会放大更多。

所以,平台可以不依赖于大部分工程师,但是没有平台,但是大部分工程师都离不开平台

个人价值

项目的代码还是需要工程师去码,没有工程师,平台什么也产生不了,如果说平台是河道,那么工程师就是河道里的船,没有了船什么也运送不出去。但是注意,船是动态的,工程师的选择也是自由的。

由于大厂的平台高,空间大,资本强悍,通常入职即巅峰,可以有一览众山小的感觉。

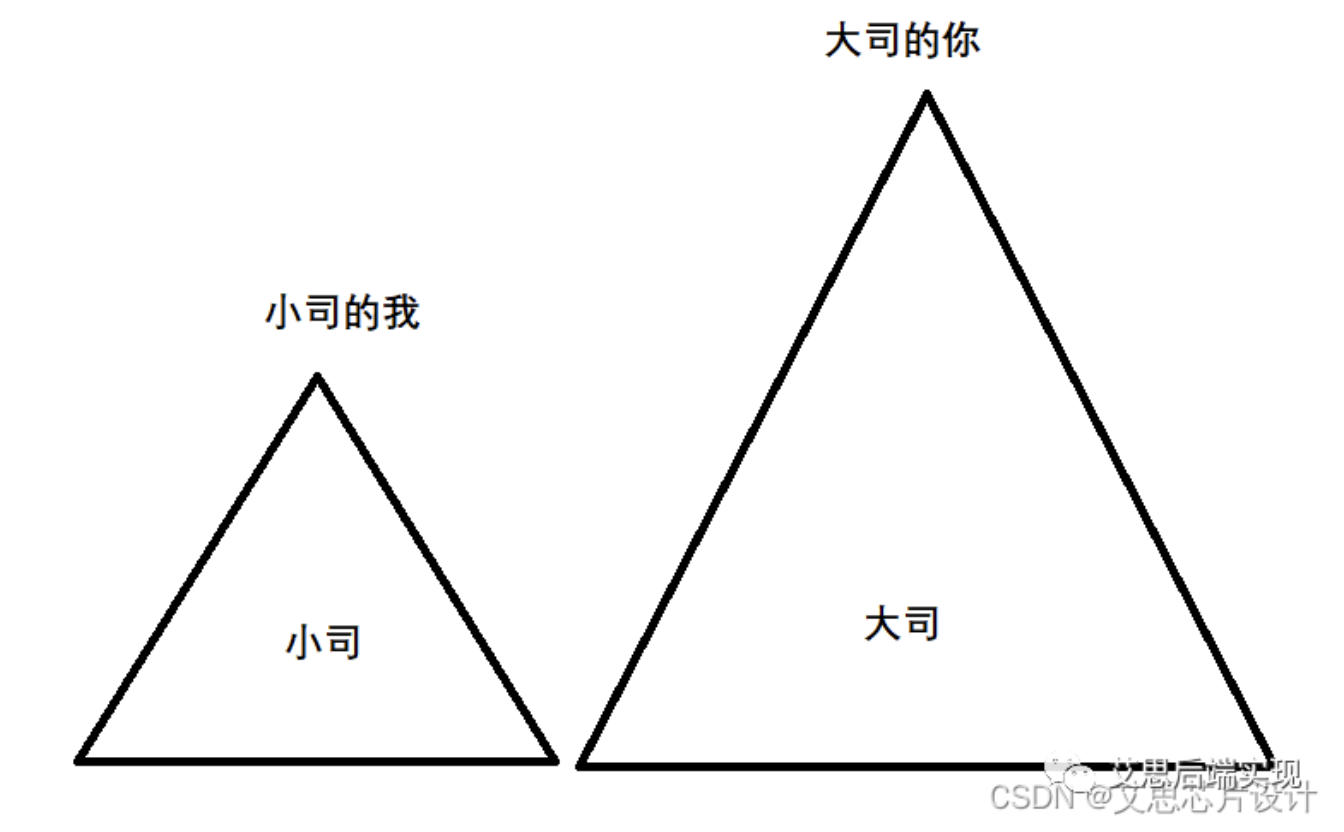

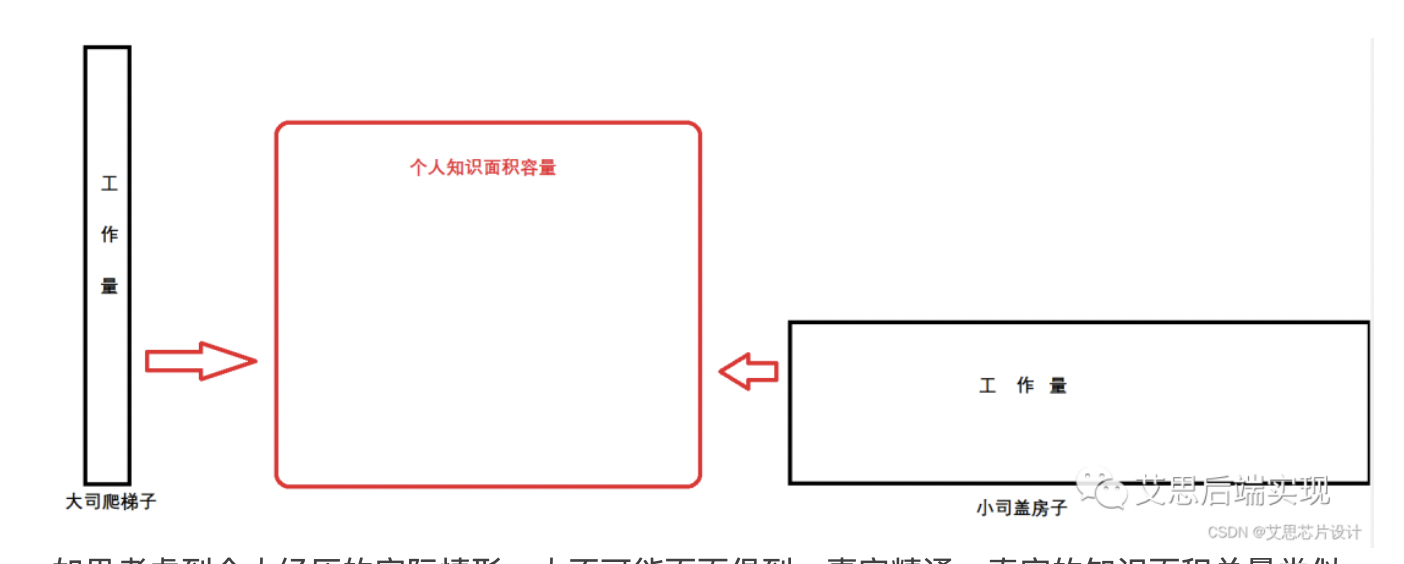

还是老话讲得好:大司就是香!由于平台构建的不同,大司和小司对人的要求完全不一样

大司爬梯子

大司的平台太好了,工程师可能过去需要做的就是在一个细分领域一直挖啊挖,不停的迭代在迭代,注意,你不是从零做起,你是基于之前很多版的基础的,前任栽树后人乘凉。当然,大平台也会很忙,譬如海思风格的公司,平台好,但是项目也是巨大的,就算在前人的基础上做,工作量也是巨大无比,加班还是很多的,但是这样的工作,专注度很高。类似爬梯子:

对于大项目,这个梯子可能会很长,很长,不过由于很好的平台,你是不用担心,它是一定能够爬上去的,这就是大厂的平台力量。对于工程师,这里有几个特点:

- 需要具备岗位的基本知识,边干边学

- 参考/继承前人工作,大概率没有完成不了的风险

- 出了问题可以问EDA或者周围同事,满眼的资源可以咨询

- 梯子比较长,要能耐得住寂寞和连续加班

小司盖房子

在小司,团队通常都不会很大,项目也会相应的比较小,但是由于流程的不完善(通常完全没有EDA公司支持),所以做项目,就是在盖房子,但是注意,领导不会让你盖摩天大楼的,因为可能小司连摩天大楼的水泥费用都没法支撑。

第一个项目,那就先盖个平房吧,看看团队的磨合吧:

对于工程师,这里有几个特点:

- 团队一定要有懂得人(就是干过完整项目的人)

- 盖房子杂事很多,什么活都得干,什么活都得会干,不会干最起码也得能学会

- 流程现场搭建边干边改

- 需要强烈的主动精神,不能等靠让

- 基本没人可以问,大家都很忙或者就是需要你搞定

- 项目迭代少,房子盖出来会不会有问题大家都没底,出问题大家也都别埋怨,要有耐心和人文关怀

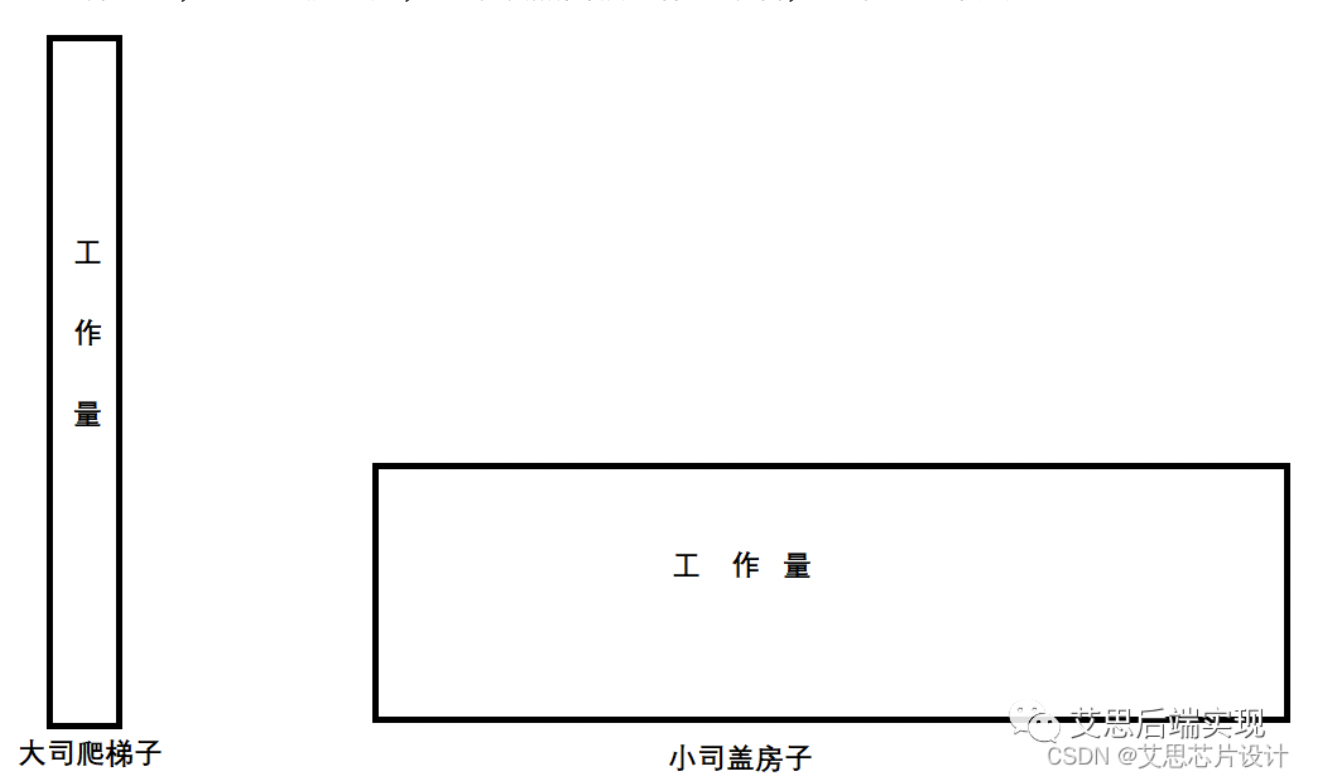

大司的梯子长,小司的房子宽,如果按照面积工作量来看,基本也差不太多:

由于平台的差异,这两者的风险是不一样。

这样的差异对人的要求就有明显的区别。对于新人或者初级工程师而言,在什么看过别人盖房子前,应该选择呆在大司,梯子不会倒好好爬。对于有经验的工程师而言,两者皆可,如果房子能盖好,起个小高层的话也未尝不可(初创公司的的逻辑),但是但是,小司想要成功,一定需要大咖卡位,否则失败是高概率的。

学习曲线

无论工程师是在小司还是大司,整个项目的大方向/流程基本还是类似的,可能小司的产品相对简单,会简化一些。回归个人的学习曲线,题主有如下的一些循序渐进的学习建议:

- 技能概览

工程师需要对本岗位有一个技术概览,这点很重要。

芯片业务流程比较长,任何一个节点都需要一个比较长的流程,工程师刚入行,通过看一些系统性的数据、公司流程、工具UG等等,一定要理解这个流程的存在的价值和特点。这样对于日后工作的流水控制非常重要,同时也可以更有效率的为项目提供服务。

这里举一个简单的例子来做说明,譬如说后仿真,这个通常是发生在APR完成后交付的数据库,目的是弥补静态时序分析和gatesim之间的缝隙,常规而言需要APR实际收敛后才可以启动gate-sim,如果工程师可以准确却分gatesim和APR ECO的关注点的不同,是完全可以通过更快速的方式提供gate-sim仿真环境的,这样可以加速gates-sim至少一个月的时间。

如果你在本岗位的工作中,连你的岗位技术概览都接触不到,那么基本可以视为公司流程不健全或者主干人力短缺的情形。这样做出来的东西大概率是没法有保证的。 - **技术专长

**这个大概率就是个人的专注领域了,譬如:RTL设计工程师,专注开发调用PCIE,这里需要花大把的力气把PCIE那本大部头书得肯几遍吧,边干边啃,有利于消化吸收。如果你是验证人员,除过搞明白PCIE的规范,也需要看看验证环境/流程里边对你有应影响的地方,除过RTL代码的bug,流程的坑也需要小心。这个技术点长期耕耘,以后也会让你成为此方面的专家。毕竟PCIE6.0都要来了,把有比把它搞清楚更香的事情吗? - **内卷 (Involution)的理解

**在英文里边以volution为词根的词有一些,大概如下的意思是漩涡,如果以它为词根,常见的有下面的一些单词:

可以看到,目前常说的内卷在应为里边其实是由一种退化的含义的,所以,innovution 并不是competition(竞争)也不是challenge (挑战),他更向是一种内部退化或者团队内部的消耗。

内卷的理解:如果一个事物(volution)不能向外发展进化(e-volution),并且只在现有的资源,被相同的人用类似的方式反复迭代,最后的事物(volution)就会落入到内卷(in-volution)化。

内卷的核心问题就是过于聚焦当下问题,并极大寄希望于采用既有流程和方式解决现在问题。这种力量越强大,内卷就会越严重。跳出内卷的一个方法就是提高维度。也就是学习当下方法后,跳出现有方法流程,从更高维度去优化。这个需要强烈的进化(evolution)意识,甚至是革命(revolution)意识。这个是对自身的挑战也是对团队的挑战。

千万不要陷入内卷(in-volution)的漩涡(volution),更不能以内卷(involution)为荣,所有因为内卷而消耗掉的资源,并不会因为消耗(cost)而变成收益(revenue),因为整个系统都处于退化(involution)形态。

4. 扁平化学习

无论你是爬梯子还是盖房子,这点都很重要,前边说过平台流程,在日常的工作中就是空气就是水,大家完全没有感受到他的价值,所以很多从公司出来的同学,尤其是大厂出来的,业务非常窄,这样在一个新环境或者小公司会比较难搞,尤其是经验比较长的工程师,如果一生只会一个梯子,那么就很难腾挪出来。所以这里需要尽早建立扁平化的学习路径,尤其是大厂员工,否则离开了大厂,压力会非常大。

代码解决具体问题,流程解决项目问题,要想可以提高维度,需要从流程平台的角度看问题

所以,专注自身业务的同时,需要关注实现这个业务的流程,间接的也可以多多参考学习其他业务部门的流程。

理解流程是优化流程的第一步,优化流程是创建流程的第一步,创建流程是打破常规流程的第一步。

通过扁平化学习,提高思考维度,才能让自己跳出当下的漩涡(volution),避免内卷( involution)。

通过扁平化学习,无论是在大司爬梯子,还是在小司盖房子,最后的知识拓扑必然要实现为一个有大矩形

如果考虑到个人经历的实际情形:人不可能面面俱到,事实精通,真实的知识面积总量类似一个正太分布

通过扁平化学习,扩展知识,使用进化甚至革命的精神,从外界吸取资源和力量,这样可以有效避免在有效的空间内相互内卷(involution),从而实现个人提升和团队价值。

作者: 艾思后端设计

文章来源: 艾思后端实现

推荐阅读

- 芯片工程师求职题目之CPU篇(1)

- 门控时钟检查(clock gating check)的理解和设计应用(上)

- ICC/ICC2 or INN 一点不成熟的浅见

- StarRC的妙用

- 芯片设计里的Multi-Bit FF探究

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。