这个选项没有错,只是它不符合题意。

Hi!是不是早已经“饥渴难耐”,终于到了安全的章节。

在开始之前我想“辩解”几句为什么啰嗦两章才开始正文:

- 暂时我接触的安全相关不是一门基础的内容,它是基于各种系统机制之上或者穿插其中的。所以这就是为什么更新的内容有时候与软件:系统、驱动、代码规范等相关,有时候与硬件:IC设计、后端、量产、Soc设计等相关。这是有区别与隐私计算中的多方安全计算(密码学技术)、联邦学习(融合延伸)等其他可信技术。

所以很多的大佬都对基础的东西很懂,当然我不是大佬,还需要学习。

- 从当年看了一本自顶向下学习计算机网络开始,就开始喜欢上这种学习方法。因为自顶向下学习搭起一个框架后,站在宏观的角度会让我们在浩瀚的知识地图里不迷路。

Returning THE THEME!本文内容如下:

篇一:硬件木马

- 一、SoC 硬件木马(Hardware Trojan)

- 二、硬件木马的特性

- 三、FPGA 中的硬件木马

- 四、硬件木马的分类

- 五、信任基准

- 六、硬件木马设计

- 七、硬件木马的防御 1、木马检测 芯片流片前的硬件木马检测 ①增强功能测试 ②侧信道指纹识别 ③硬件木马防范 芯片流片后的硬件木马检测 2、信任设计3、小结

篇二:电子供应链

- 一、安全隐患

- 二、信任问题

- 三、对策

下面开始我们的硬件安全学习之旅吧。

硬件木马

硬件木马,硬件木马会攻击硬件本身,引起自身的安全问题

这里主要讲述了 SoC 的设计制造流程中的硬件木马(Hardware Trojan)插入威胁、HT 特性、FPGA 中的 HT、HT 的分类、信任基准、硬件木马的防御。

由于硬件木马的硬件级别的植入,软件级别的对应措施,可能不足以应对由硬件造成的威胁。

一、SoC 的设计制造流程中的硬件木马(Hardware Trojan)插入威胁

随着尖端工艺的代工成本和现代片上系统(system-on-a-chip,SoC)平台设计复杂性的不断提高,曾经局限于一个国家甚至一家公司的IC供应链已经遍布全球。

在这种形式下,硬件电路设计中的第三方资源(主要指用于外包芯片制造和SoC开发的第三方知识产权,即intellectual property,简称IP核,包括软核和硬核)在现代电路设计和制造中得到了广泛的应用。

这类资源的利用虽然在很大程度上减少了设计工作量、降低了制造成本、缩短了产品上市时间(time to marketing,TTM),但是对第三方资源及服务的高度依赖也引发了安全问题,打破了“攻击者无法轻松访问封闭的IC供应链”的幻想。

例如,恶意代工厂可能会将硬件木马程序插入所制造的芯片中,交付的IP核可能包含恶意逻辑和设计缺陷,这些缺陷在IP核集成到SoC平台后会被攻击者利用。

硬件安全的概念在硬件木马出现后被正式引入。学术界和工业界开始采取措施缓解或防止相关威胁。硬件安全最初指的是硬件木马的设计、分类、检测和隔离。

硬件木马威胁与不受信任的代工厂密切相关。因此,研究者开发的硬件木马检测方法往往侧重于IC制造过程的流片后阶段,强调增强现有检测方法的安全性。

鉴于第三方IP核可能是恶意逻辑插入的另一个攻击向量,对综合前设计的保护也变得同样重要。据此,研究者还开发了流片前电路保护方法。

除了硬件木马检测,硬件安全的概念还从测试解决方案延伸到形式化验证方法。形式化验证方法不仅在保证软件程序安全时得到广泛应用,还被证明在硬件代码的安全验证中颇为有效,因为硬件代码通常是使用硬件描述语言(hardware description language,HDL)编写的。

形式化验证方法的发展不仅有助于为硬件设计提供高水平的安全保证,即便在攻击者可能有权访问原始设计的情况下也是如此,也有助于克服黄金模型在许多硬件木马检测方法中的局限性。然而,在实现形式化验证方法时,安全属性的构建却成为硬件安全研究者尝试解决的一个开放性问题。

二、硬件木马的特性

硬件木马(Hardware Trojan)指对电路设计的恶意的、故意的修改,在部署电路时会导致恶意行为(例如通过I/O输出密钥、通过侧信道功率输出重要信息、增加系统延迟、减半加密轮数)。

- 1、结构:基本结构有两个:触发器和攻击载荷。当触发器监测到预期的事件,攻击载荷就会执行恶意行为。触发条件可以是某内部节点上的n位值、重复发生某事件 2^10^次、到达某个温度等,以增加反检测能力。

- 2、硬件木马示例:

- ①加密引擎中的木马:攻击载荷可以是由攻击者自定义的虚拟密钥而不是用于敏感加密的实际加密密钥,通过侧信道泄露硬件密钥。例如恶意片外泄露技术(MOLES),通过功率侧信道泄露硬件密钥。

- ②通用处理器中的木马:攻击者在系统中植入后门,根据攻击者的命令输入禁用安全启动机制。并在硬件木马的帮助下实现深层次攻击,如利用缓冲区溢出攻击绕过内存保护机制或通过认证绕过漏洞来访问特定资产。

硬件安全研究的演进已经从硬件木马的检测转移至可信硬件的开发,即构建信任根。虽然硬件设备的一些固有特性对电路性能有负面影响,但是可以将这些特性用于安全保护。

一个典型的例子是物理不可克隆函数(physical unclonable function,PUF)的开发,借助电路制作过程中的工艺偏差,以“激励—响应”对的格式生成特定芯片的指纹。除金属—氧化物半导体场效应晶体管(MOSFET)外,研究者正在研究新型的晶体管,如自旋转移矩(spin transfer torque, STT)器件、忆阻器和自旋畴壁器件等,利用器件性能的特殊性来实现新型的硬件安全应用。

现有的硬件木马设计可分为基于触发机制和基于有害功能机制两类。

硬件木马的识别主要依赖于识别触发机制和有害功能机制。

因此,硬件安全的研究者重点关注这两种机制,以这两种机制为突破口,探索和评估新的硬件木马。

三、FPGA 中的硬件木马

FPGA用途广泛,从电信系统到导弹制导都有应用。但FPGA的木马可以通过IP核的形式载入通用FPGA结构中,并且有大量可被控制的可重构逻辑单元,攻击者从而利用FPGA通用系统进行攻击。

存在IP依赖木马和非IP依赖木马。

IP依赖木马是一种攻击手段,其中攻击者将恶意代码嵌入到FPGA的IP(知识产权)模块中。 这些IP模块是FPGA设计中使用的现成模块,它们被集成到设计中,并在运行时执行特定的任务。攻击者可以利用这些IP模块中的漏洞,将恶意代码注入到FPGA中,从而控制整个系统。

非IP依赖木马则是一种更高级的攻击手段,它不需要依赖FPGA中的IP模块。 这种类型的木马利用了FPGA的物理层特性,例如电压波动、时钟偏差等,来制造错误,从而篡改系统行为。这种类型的木马很难检测和防御,因为它不依赖于特定的IP模块或设计,而是利用了FPGA的通用特性。

四、硬件木马的分类

分类的主要依据是硬件木马的物理、激活、功能特性。

硬件木马是指故意对电路设计进行恶意修改,导致电路在运行时产生意外行为。

受硬件木马影响的IC可能会发生功能或规范被更改、泄露敏感信息、性能下降及系统不可靠等情况。目前有些文献已对硬件木马提出了详细的分类,涵盖广泛的具有潜在风险的硬件木马。

比如:根据插入阶段、抽象级别、激活机制、效果和位置这五个不同的属性将硬件木马进行分类。

- 硬件木马与制造缺陷完全不同。制造缺陷具有无意、随机的特点,数十年来已被广泛研究,其行为可以通过Stuck-at故障、延迟故障等模型来反映。

- 但对于硬件木马,研究者却难以创建适合所有类型的模型。

- 此外,缺陷只在制造过程中产生,而硬件木马可以在IC开发的任何阶段插入。

因此,硬件木马问题比制造缺陷的表现更为复杂。

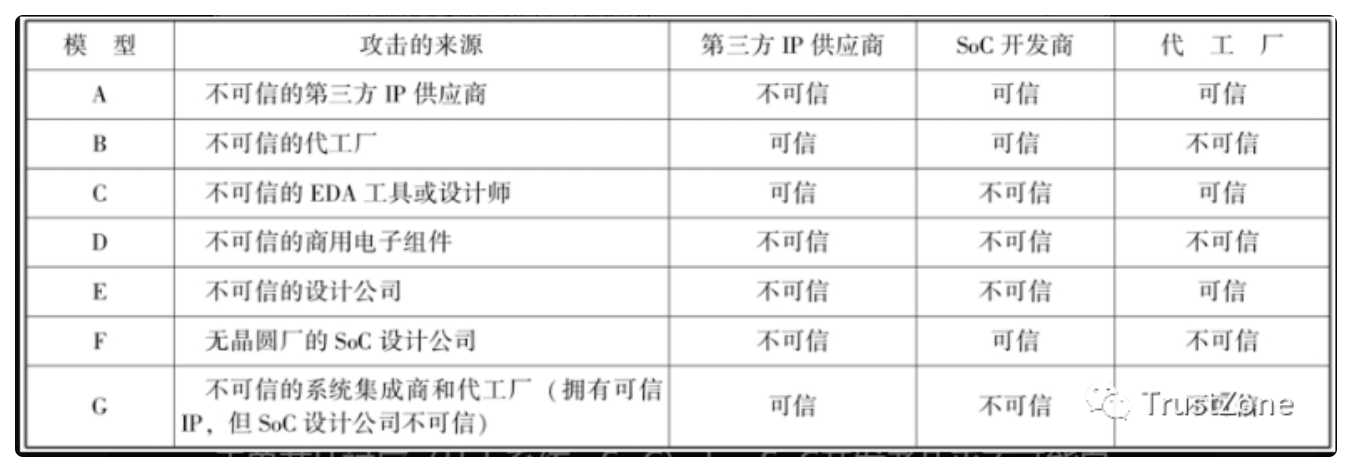

五、信任基准

信任基准是一种用于检测和评估电子系统安全性的方法。它涉及到在系统中故意引入一些错误或“木马”,以观察它们对系统性能和稳定性的影响。

这种方法可以帮助评估不同检测技术的有效性,并确定最有效的防御策略。

- 1、基准命名约定:DesignName - Tn#$,e.g.,MC8051-T1010:木马10号被插入MC8051的1号位置,版本为0

- 2、信任基准样例:

- ①开发制造阶段的基准样例:EthernetMAC10GE-T710,由组合器触发的木马程序,查找特定的16位向量

- 基准命名约定:DesignName - Tn#$,e.g., MC8051-T1010:木马10号被插入MC8051的1号位置,版本为0。这是一种标准的命名约定,用于标识在特定设计中的信任基准测试。

例如,MC8051-T1010表示在MC8051设计的第1号位置插入了木马10号,版本为0。

- 信任基准样例:信任基准测试可以用在不同的阶段,例如开发制造阶段。以下是一个样例:EthernetMAC10GE-T710,这是一个由组合器触发的木马程序,它查找特定的16位向量。

这个样例表明,在EthernetMAC10GE的设计中,已经插入了一个由组合器触发的木马程序,该程序会查找特定的16位向量。这种类型的木马可能会对系统性能产生重大影响,尤其是如果它能够成功地干扰系统的关键部分。

在硬件设计中,信任基准测试是一种重要的安全评估方法。它通过对系统进行故意攻击来测试其防御能力,从而提供了一种度量防御策略有效性的方法。

同时,通过比较不同木马的影响和各种木马检测技术的效果,设计师可以了解到哪种方法最有效,从而改进他们的设计。

为了防止信任基准测试带来的潜在风险,设计师通常会在测试后对系统进行详尽的检查和验证,以确保没有留下任何可能影响系统性能或稳定性的隐患。同时,也会努力改进设计,以增强系统对未来攻击的防御能力。

六、硬件木马设计

对于设计良好的硬件木马,传统的功能测试方法很难检测[7]。通常,硬件木马包含两个基本部分:木马触发器(实施木马激活)和有害电路(实施有害功能)。

- 木马触发器是一个可选部件,用于监控电路中的各种信号或一系列事件。

- 有害电路通常从原始(无木马)电路和木马触发器的输出中获取信号。

一旦木马触发器检测到预先确定的事件或条件,就会激活有害电路执行恶意行为。通常情况下,木马触发器会在极为罕见的情况下被激活,因此有害电路大部分时间均保持非活动状态。

当有害电路处于非活动状态时,IC就像一个无木马的电路,很难将木马检测出来。

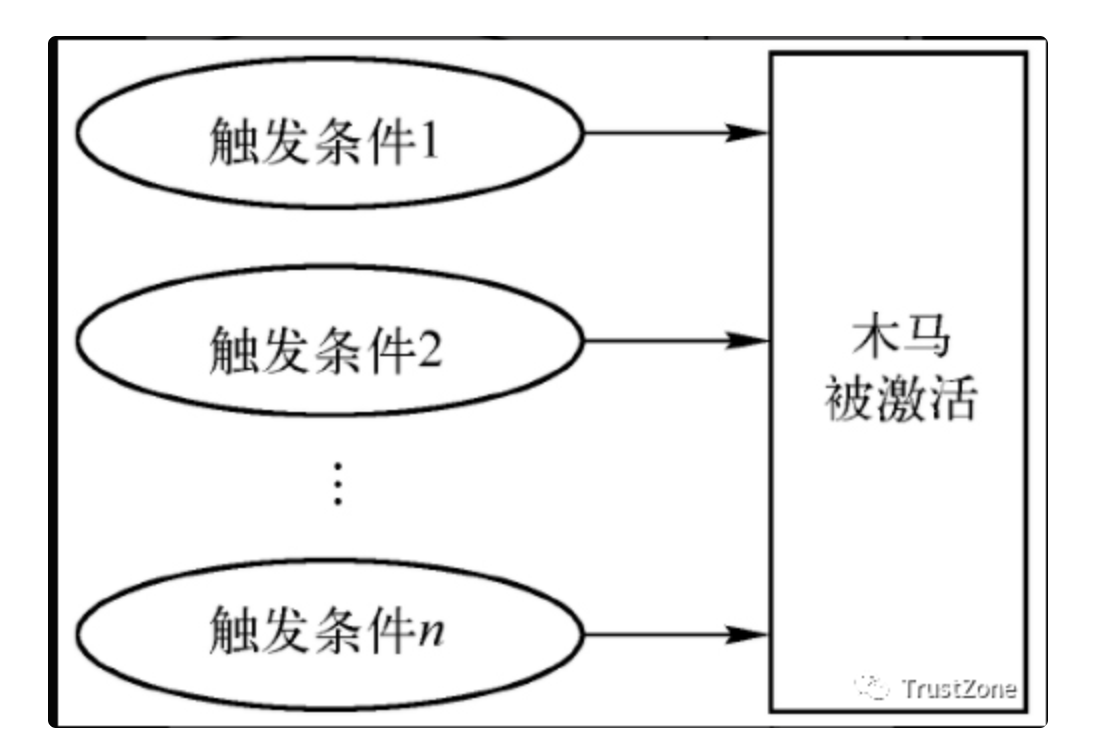

根据木马触发机制的不同,硬件木马可分为:组合木马和时序木马。一些木马触发机制采用组合和顺序混合机制设计。图展示了组合硬件木马的抽象模型。恶意电路行为由同时发生的一组触发条件激活。组合硬件木马不使用触发器或锁存器来存储状态信息。

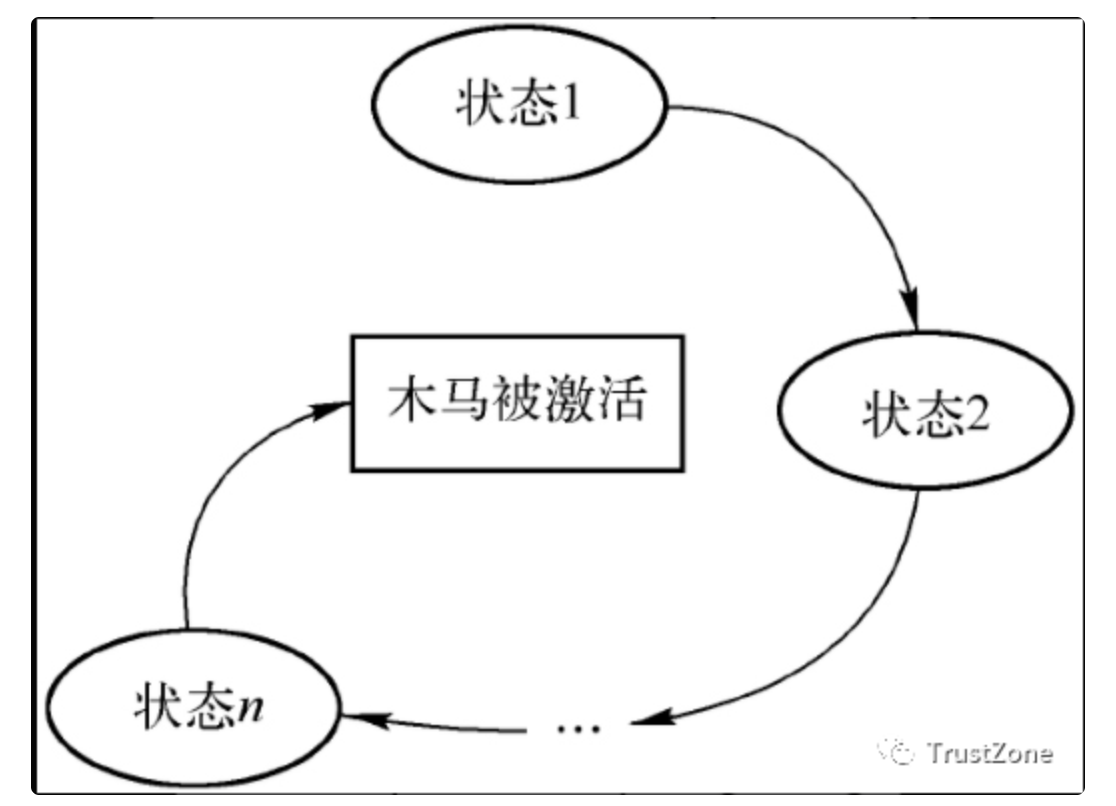

下图展示了时序硬件木马的抽象模型。木马被一系列状态转换激活。

下图给出了硬件木马的触发机制和有害功能机制。

现有的硬件木马设计可分为基于触发机制和基于有害功能机制两类。

硬件木马的识别主要依赖于识别触发机制和有害功能机制。

因此,硬件安全的研究者重点关注这两种机制,以这两种机制为突破口,探索和评估新的硬件木马。

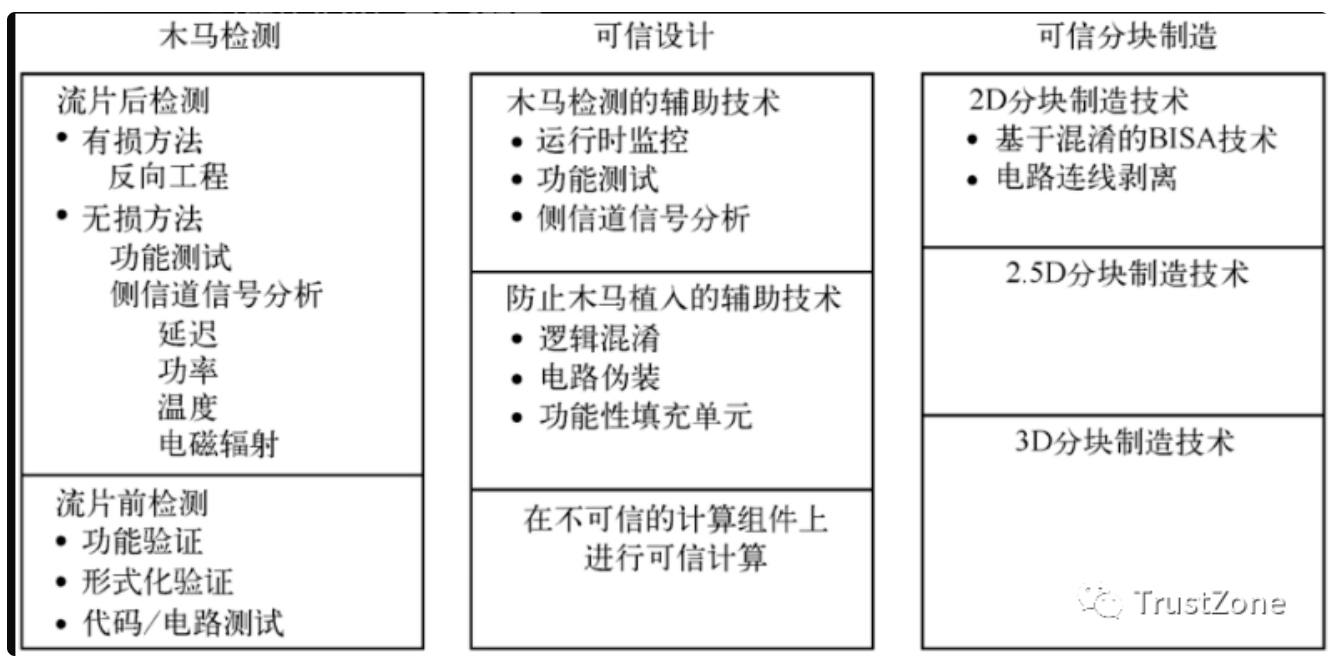

七、硬件木马的防御

1、木马检测

木马检测时最简单、常用的方法,分为硅前、硅后两阶段。

- ①硅后检测:

- 1、破坏性逆向工程:检测能力强,可以检测到任意恶意修改

- 2、功能测试:检测能力弱,难以触发木马

- 3、侧信道信号分析:测量硬件参数来检测硬件木马(如延迟、功率、温度、辐射),将其与正常的(破坏性逆向工程得到的结果)进行对比

- ②硅前检测:

- 1、代码覆盖率分析:即在设计阶段的功能验证期间执行代码行的百分比。木马可能逃脱

- 2、形式验证:如符号执行、模型检查、信息流,在验证3PIP方面有效。

- 3、结构分析:用定向指标将低激活概率的信号或门电路标记为可疑。

主要是从两个角度详细展开:

芯片流片前的硬件木马检测

与软件病毒、软件木马不同,硬件木马无法通过固件更新轻易消除。因此,硬件木马对计算机系统的危害更大。硬件木马由攻击者设计。攻击者往往采取在IC设计中添加不需要的功能的方法植入硬件木马。

硬件木马的设计没有标准流程,所采取的方法取决于攻击者的目标及可用资源。尽管如此,硬件安全研究者还是对不同的硬件木马进行了分类。

基于硬件木马的隐蔽性及其可能造成的影响,研究者还提出了多种硬件木马设计方案。虽然硬件木马大多是在寄存器传输级(register transfer level,RTL)层面插入的,但有些是通过半导体掺杂操作插入的。

这种在一开始就种下了不安全的种子

由于传统的电路测试方法在检测恶意逻辑方面存在不足,因此近年来研究者专门开发了硬件木马检测方法和可信集成电路设计。研究者已经提出了大量的硬件木马检测和防范方法。这些方法主要可以分为四大类:

- ①增强功能测试;

- ②侧信道指纹识别;

- ③硬件木马防范;

- ④电路强化。

①增强功能测试

由于增强功能测试方法是基于“硬件木马通常由小概率事件触发”这一思想的,因此,研究者提出以下两种建议:

- ①将这些小概率事件包含在测试模式中,以便在测试阶段触发木马程序[5];

- ②在门级网表中分析所有小概率事件,以识别可能充当触发器的可疑节点[19]。

增强功能测试方法的局限性在于不存在对于小概率事件的标准定义,使得在标准测试模式和小概率事件模式之间留有巨大的缺口。同时也会给测试带来工作量的提升。

②侧信道指纹识别

侧信道指纹识别是另一种流行的硬件木马检测方法。尽管在测试阶段硬件木马不易被触发,可能会逃避功能测试,但插入的硬件木马必然会改变被攻击电路的参数[21,39,49]。

该方法的有效性取决于区分硬件木马入侵电路和无硬件木马电路的侧信道信号的能力。

因此,利用先进的数据分析方法,通过消除不断增加的工艺误差和测量噪声,可以帮助生成侧信道指纹[14,48]。在指纹生成和硬件木马检测中,有些研究成果选择使用多种侧信道参数及其组合,包括全局功耗跟踪[48]、局部功耗跟踪[3,4]、路径延迟[7,50]等。

基于侧信道指纹识别的硬件木马检测方法因具有非侵入性而得到了广泛的应用,由于是依据黄金模型可供比较的假设发展而来的,在很多情况下,黄金模型不容易获取,所以不容易实现。

③硬件木马防范

硬件木马防范和电路强化技术方法试图利用附加逻辑修改电路结构,以消除小概率或可疑事件,或者使目标电路对恶意修改更加敏感。这类方法往往与其他硬件木马检测方法结合使用,可提高检测精度或降低检测成本。

即使在目标设计中使用了电路协同设计技术来降低附加逻辑的影响,附加保护逻辑仍然会影响电路的性能。此外,强化结构本身也可能成为硬件木马攻击的目标。

这不就是成了一个无限套娃的场景,比如说安全的架构TEE,让更多地安全目的与服务进入到了安全侧,安全侧的代码量于是极大的增加了,这样安全侧代码被攻击的面也就越来越广了。

芯片流片后的硬件木马检测

尽管现有的检测方法已能成功检测到某些硬件木马,但检测范围仍十分有限,其原因在于依赖于过度简化甚至有时是错误的假设。这些假设往往包括以下方面:

- (1)硬件木马设计者使用传统、简单的电路结构,会使硬件木马的功能受到限制;

- (2)硬件木马设计者试图占用尽可能小的片上区域,在芯片侧信道信息中难以发现硬件木马产生的侧信道信息;

- (3)被测电路存在黄金模型来检测侧信道信息的变化;

- (4)攻击者只会攻击数字电路,因为模拟和射频电路对恶意篡改更为敏感。

这些假设很长时间内都被硬件安全研究者所接受,成为开发先进硬件木马检测和预防方法以及相关研究工作的主要指导原则。很可惜,这些假设并不完整,甚至带有误导性。笔者现在已经明显意识到,硬件安全和硬件木马检测的问题比之前设想的更加复杂、更加普遍,特别是:

- (1)类似于现代电路设计中的进步,硬件木马可以利用先进的设计技术,在不牺牲功能的情况下增强隐蔽性;

- (2)增强的硬件木马程序设计可以使用大量的芯片空间,相对于整个侧信道信息仍保持隐藏状态;

- (3)包含第三方资源的集成系统不一定都存在黄金模型;

- (4)模拟和射频电路同样容易受到硬件木马攻击。

上述情况推翻了许多先前提出的硬件木马检测和预防方法,导致无论在数字领域还是在模拟和射频领域,集成系统都容易受到硬件木马的攻击。

因此,研究者开始研究芯片流片后的检测方法,主要利用流片后侧信道指纹识别和片上等效性检查等技术。

这里的关键思想是在测试阶段,隐藏的硬件木马可能很容易避开检测,如果被触发,将会对侧信道指纹识别或电路功能造成重大影响。

2、信任设计

- 检测静默的、低功率消耗的硬件木马更有效的一种方式。

- ①促进测试:字面意思,如增加运行时监控模块

- ②木马植入防范:逻辑混淆、伪装、功能性填充单元(将布局填满)。通过重新排序逻辑门、加入额外的逻辑功能或者使用不同的设计方法来实现。

- ③可信计算:软件级别的检测,是基于不可信元件的可信计算,是最后一道防线。主要有TPM (受信任的平台模块)、安全启动 (Secure Boot)、远程验证 (Remote Attestation)、封装 (Sealing)组成。

- ④分割制造:字面意思,降低代工厂的不可信水平

3、小结

一般来说,硬件木马防护对策分为三大类。每个大类还可进一步分为几个子类。硬件木马防护对策的分类如图:

这一部分是最常用于芯片的设计中的,比如在最近的项目中,就做了很多防止侧信道攻击的设计,这里留着后面值得展开学习一下。

如果我没更新,那肯定是我又被换岗位了。

聊聊第二个大点:电子供应链

电子供应链

本章主要讲述电子供应链上的安全隐患及应对措施。简要罗列一下会在哪些点出现安全问题。

随着集成电路的制造工艺发展至深亚微米级和纳米级,集成电路设计和制造的复杂性急剧增加。

专用集成电路(application-specific integrated circuit, ASIC)或片上系统(SoC)组件通常需经过复杂的工艺过程。

该过程首先将规范转换为行为描述,通常使用硬件设计语言(hardware design language,HDL),如Verilog或VHDL。

接下来,执行合成,根据网表(逻辑门)将行为描述转换成设计实现。在完成设计实现后,数字GDSII文件被交给代工厂进行IC制造。

一旦代工厂生产出实际的IC,将通过测试过程确保其正确。

那些通过测试的IC通过组装、重新测试后发送至市场,最终被部署到电子系统中。

先进的半导体制造技术在IC开发过程的每一个阶段都需要投入大量的资金。

例如,2015年拥有一家代工厂的成本约为50亿美元[2]。因此,大多数半导体公司无力维持从设计到包装的全部IC供应链。

为了降低研发成本、缩短开发周期,半导体公司通常将部分工作外包给第三方代工厂,购买第三方IP核,使用第三方供应商的EDA(electronic design automation,电子设计自动化)工具。

显然,第三方可能不可信或具有潜在恶意,第三方的加入增加了系统的安全风险。

有研究表明,IC供应链容易受各种攻击,如硬件木马、逆向工程、IP盗版、IC篡改、IC克隆、IC生产过剩等。其中,硬件木马可以说是最大的威胁,引起了广泛关注。

一、安全隐患

- 1、硬件木马

- 2、CAD工具:CAD 工具只注意可能无意间引入漏洞,CAD 设计主要考虑传统指标(如面积、产量、可测试性),而忽略了安全性。

- 3、测试/调试工具:无法避免其在电子元件上的使用,但其允许攻击者观察或控制其内部状态

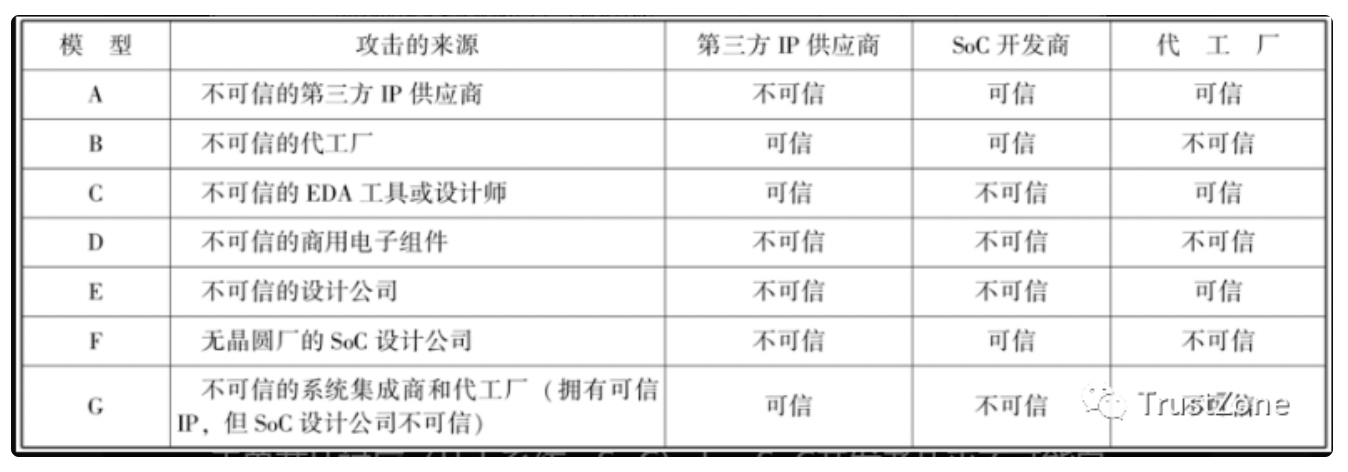

二、信任问题

- 1、IP滥用:即生产超过约定数量的元件

- 2、IP盗版:非法复制和修改

- 3、零件不合格:

- 4、集成电路 ** 逆向工程:RE

- 5、文档伪造:即数据造假

- 6、集成电路再标记、回收:放图

三、对策

- 1、木马检测、安全检查:

- 2、IP加密

- ①硬件锁:硬件锁通常是一个外部USB设备,其内部包含了一个芯片,这个芯片具有独特的识别码、加密功能和存储能力。软件开发者可以将授权信息、加密算法和关键数据存储到硬件锁中,然后将这些功能与其开发的软件绑定在一起。软件启动时,会与连接的硬件锁进行通信,验证硬件锁的身份。这通常包括向硬件锁发送请求,硬件锁返回唯一的识别码供软件进行验证。只有在硬件锁通过验证后,软件才会继续运行。

- ②时间锁:类似硬件锁,通常与硬件锁结合使用。

- ③追踪/水印技术:将特定的标识信息嵌入到IP中,以便在未经授权使用的情况下进行追踪。提取水印后进行水印比对,例如物理不可克隆函数(Physical Unclonable Function, PUF)利用微小的物理变异来生成唯一的标识信息。 这些微小的变异是由制造过程中的随机性和不均匀性引起的,使得每个硬件实例都具有独特的特性。PUF可以用于实现设备的唯一标识、认证和密钥生成。

提起硬件锁的时候你是否想起了可信根?

- 3、电气测试、物理检查

参考资料

感谢网络中浩瀚的资料以及前辈们的分享,我不过是这些知识的学习者与资料整理者,偶尔换了我喜欢的方式表达出来。

以上就是本次的全部的内容,下次聊!

- ZHANG X, TEHRANIPOOR M. Case study: Detecting hardware trojans in third-party digital ip cores[C]// Proceedings of the IEEE International Symposium on Hardware-Oriented Security and Trust(HOST). IEEE,2011:67-70.[31] HICKS M, FINNICUM M, KING S T, et al. Overcoming an untrusted computing base: Detecting and removing malicious hardware automatically[C]//Proceedings of IEEE Symposium on Security and Privacy.IEEE, 2010:159-172.

- SALMANI H, TEHRANIPOOR M. Analyzing circuit vulnerability to hardware trojan insertion at the behavioral level[C]//Proceedings of the IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems(DFT). IEEE, 2013:190-195.[33] WAKSMAN A, SUOZZO M, SETHUMADHAVAN S. FANCI: Identification of stealthy malicious logic using boolean functional analysis[C]//CCS’13:Proceedings of the ACM SIGSAC Conference on Computer &Communications Security. ACM, 2013:697-708.

- 《集成电路安全》

- HICKS M, FINNICUM M, KING S T, et al. Overcoming an untrusted computing base: Detecting and removing malicious hardware automatically[C]//Proceedings of IEEE Symposium on Security and Privacy.IEEE, 2010:159-172.

- RAJENDRAN J, VEDULA V, KARRI R. Detecting malicious modifications of data in third-party intellectual property cores[C]//Proceedings of the 52nd Annual Design Automation Conference. ACM, 2015:1-6.

- 硬件木马检测

- 《HARDWARE SECRURITY - A HANDS-ON LEARNING APPROACH》

- CAO Y, CHANG C H, CHEN S. Cluster-based distributed active current timer for hardware trojan detection[C]//Proceedings of the IEEE International Symposium on Circuits and Systems(ISCAS). IEEE,2013:1010-1013.

作者:Hcoco

文章来源:TrustZone

推荐阅读

更多物联网安全,PSA等技术干货请关注平台安全架构(PSA)专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入PSA技术交流群,请备注研究方向。