为什么需要复位树

复位信号在数字电路里面的重要性仅次于时钟信号。对一个芯片来说,复位的主要目的是使芯片电路进入一个已知的,确定的状态。主要是触发器进入确定的状态。在一般情况下,芯片中的每个触发器都应该是可复位的。在某些情况下,当在高速应用程序中使用流水线触发器(移位寄存器触发器)时,为了实现更高的性能设计,可能会从某些触发器中消除复位。这种类型设计需要在复位激活期间,运行预先确定数量的时钟周期,以使芯片处于已知的状态。

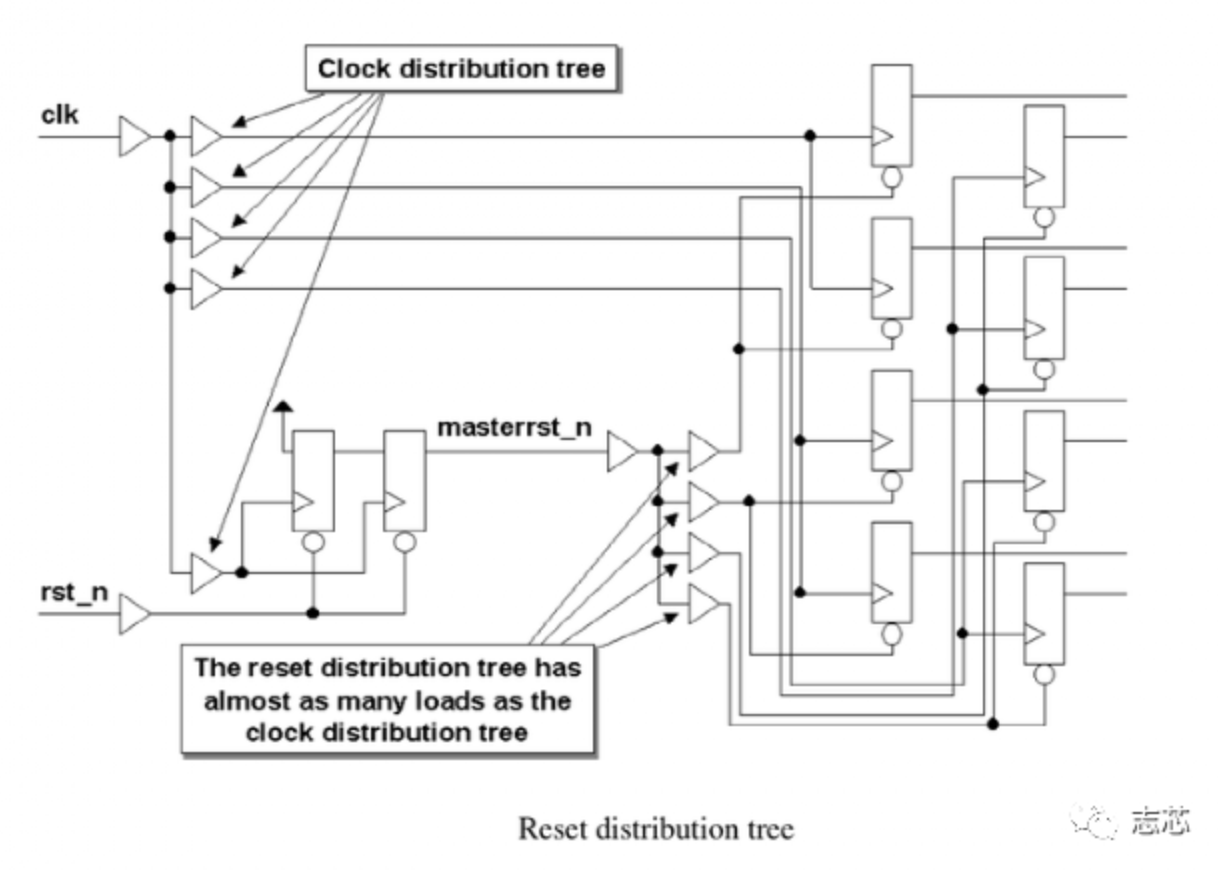

复位树是复位电路形成的类似于时钟树的树状结构,因为复位信号也要送到各个寄存器上。复位树和时钟树一样应该引起重视,因为典型的数字电路中,reset的负载和clock的负载数量一般是相当的。不管是同步复位还是异步复位,对复位树都是有时序要求的。

复位信号用什么电路产生

POR是上电复位电路(Power-On Reset),广泛应用于各种数字电路和系统中。上电复位电路就是在电源电压上升过程中一直保持低电平(有效复位电平),直到电源电压稳定达到系统规定的正常工作电压后才迅速产生一个高电平(无效复位电平)。在复位信号电平发生翻转时,电源所上升到的电压值被称作复位电路的“起拉电压”。

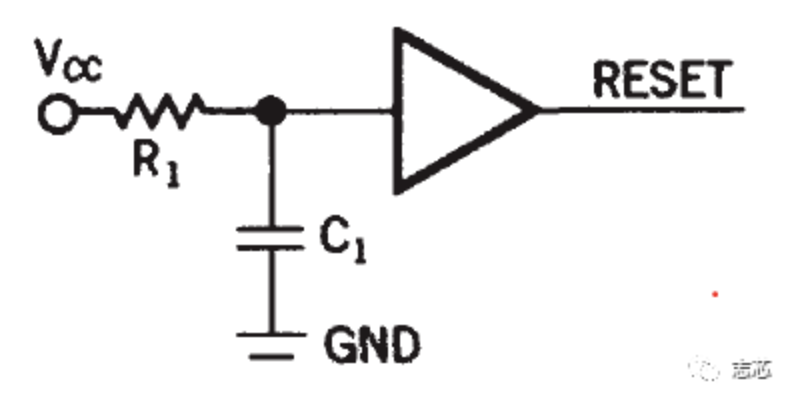

上图是一种基于RC网络实现的简单复位电路,复位信号在上电开始的一段时间内保持低电平接近零伏),随着电源电压Vcc通过电阻R1对电容器C1充电,当电容上极板的电压达到一定高位后触发后级门电路,复位信号随即输出高电平。

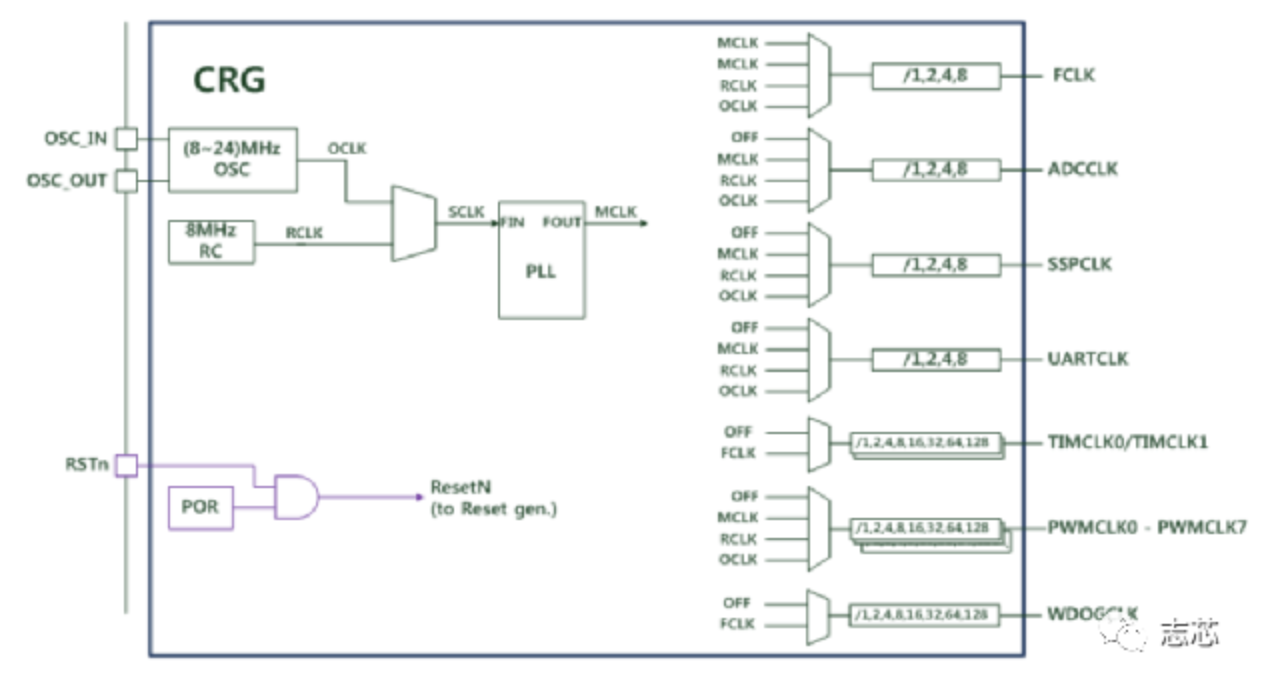

如下图所示,复位信号源也是CRG(时钟复位信号产生模块)的重要组成部分。

复位实现主要有同步复位和异步复位两种方式,两种方式使用的寄存器结构和复位树结构都不相同。

同步复位

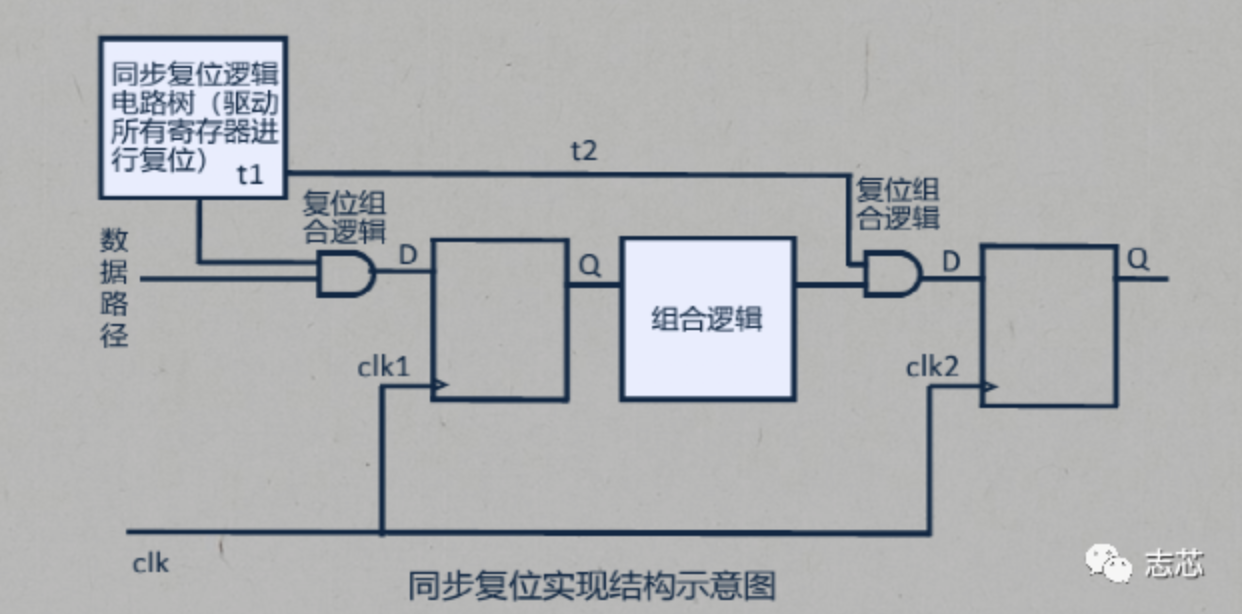

同步复位采用下图所示的寄存器电路,复位信号和数据信号通过组合逻辑接入到寄存器的数据输入端,二者共用时钟信号,复位也必须在时钟有效沿下才能生效。

同步复位的优点:1、同步复位可以确保整个电路为同步电路;2、同步复位对复位信号毛刺不敏感,可以过滤掉复位信号的毛刺;3、同步复位相比于异步复位而言会综合成更小的触发器。

同步复位的缺点:1、同步复位要求复位脉冲信号要尽可能的宽,必要的时候需要对复位信号进行脉冲展宽,从而保证复位信号能够出现在时钟有效沿到来时;2、同步复位需要保证时钟存在才能对电路进行复位,在某些使用时钟门控节约功耗的场景下,由于没有时钟,可能会造成复位失效,此时必须使用异步复位。

异步复位

下图是一种异步复位采用的寄存器结构,将边沿触发器的非门替换为或非门。SD=RD=0时为工作态;SD=1&RD=0为置1态;SD=0&RD=1为置0态。该寄存器的复位生效不需要依赖于时钟有效沿。

异步复位的优点:1、异步复位具有最高优先级,不管有没有时钟都能正确复位,综合工具能够自动推断出异步复位而不需要添加额外综合参数。2、生产商所提供的单元库中带有异步复位触发器,可以保证数据路径干净,可以减小路径延时,缓解时序紧张。

异步复位的缺点:1、异步复位使整个系统不再是同步系统,异步复位在时钟有效沿附近释放需要满足移除时间和恢复时间的时序要求,如果不满足即会出现亚稳态。2、异步复位对复位信号的毛刺比较敏感,需要设计专门的毛刺过滤器来对复位毛刺进行消除。

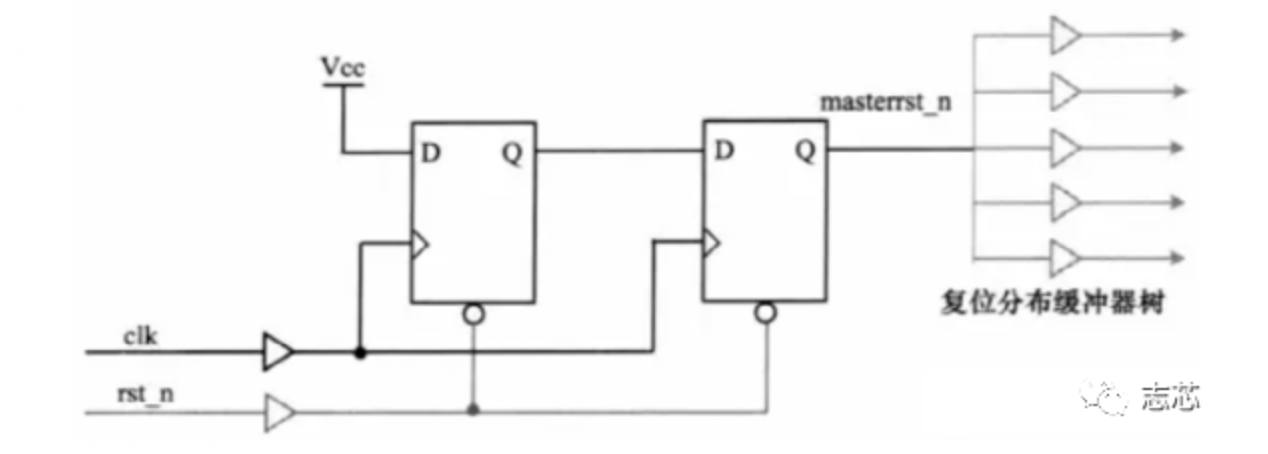

异步复位,同步恢复:所有的复位信号是用两集同步器的第二级 reg送到后来的reg系列,这个reg和后面的所有reg系列都有recover和removal timing check。

一般复位信号送到芯片内部之前需要经过同步处理,一般使用两级同步器。两级同步器是1防止reset中的glitch导致reg错误反转;2防止复位移除时刚好处于时钟跳变边沿导致亚稳态,所以把reset信号通过同步电路变成clk clock这个group中的一级信号,同步化。所以对于异步复位同步恢复,复位时钟树不用单独处理,同步器的reg和功能reg自己做平。复位时时钟频率也可以拉低,比较容易满足时序要求。

END

作者:Jack Xu

文章来源:志芯

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。