1 使用范围

此文档为DDR4 SDRAM的使用说明书,包含了DDR4 SDRAM的特性、功能、AC与DC特性、封装与出球分布。此标准的目的为定义从2Gbit到16Gbit的x4\x8\x16 DDR4 SDRAM的JEDEC最小标准。此标准是基于DDR3的标准(JESD97-3)以及DDR和DDR2的部分标准(JESD79\JESD79-2)。

DDR4 SDRAM标准中的每一处改动,都是通过委员会考虑并投票通过的。JESD79-4说明中新增的修改都是先累计投票,然后再替换整个部分,并将新增部分增加到功能描述与操作中。

2 DDR4 SDRAM 的引脚封装与寻址

2.1 DDR4 SDRAM x4\x8\x16的行

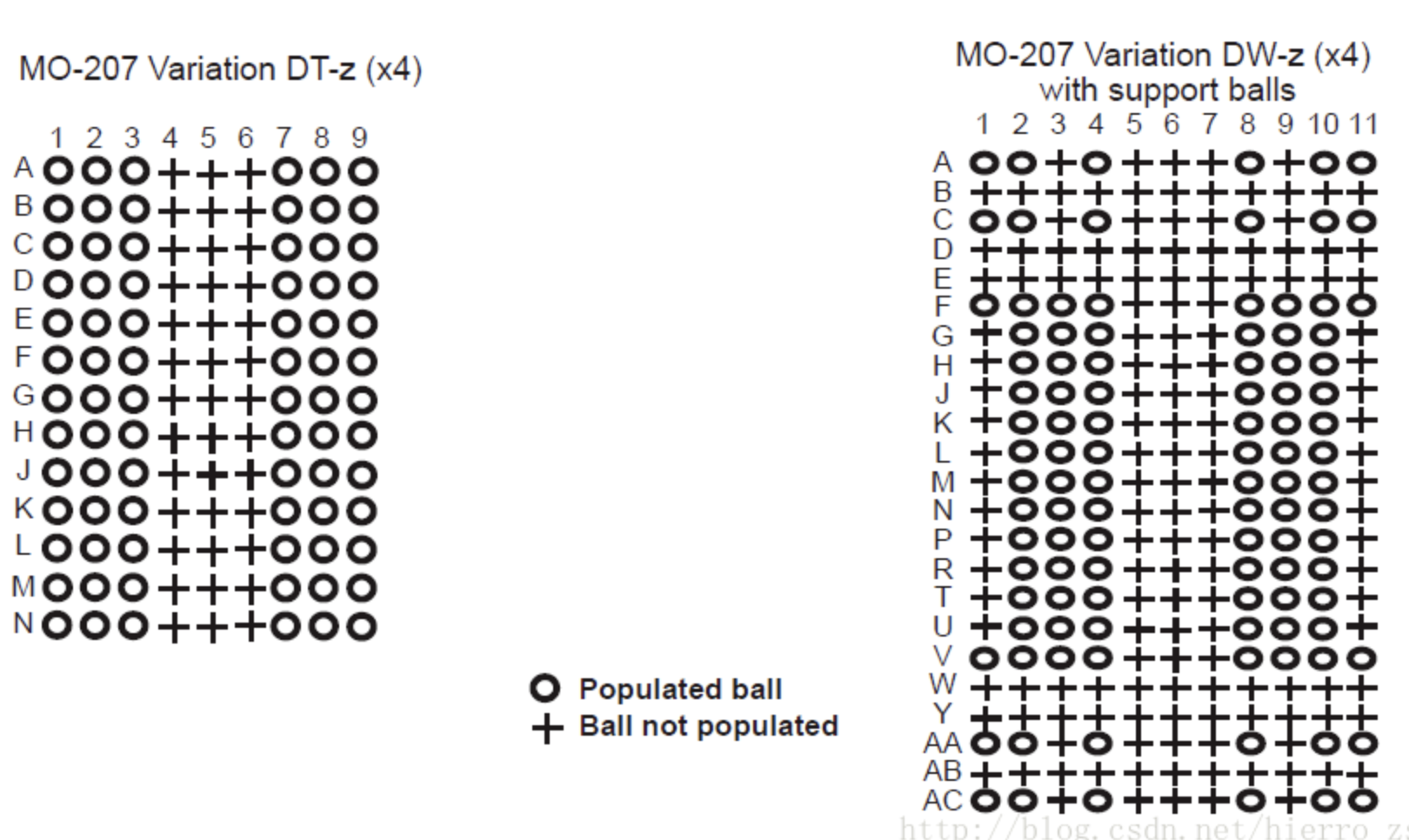

x4/x8的DDR4 SDRAM器件都有13个电气行的出球,电器行共包含信号出球与电源地出球。x16的器件有16个电气行的出球,但是因为机械补偿仍然会有一些没有激活的出球作为附加行。

2.2 DDR SDRAM 出球间隔

DDR4 SDRAM的出球间隔为0.8mm x 0.8mm,隔离岛为三列。

2.3 DDR4 SDRAM x4/x8/x16的列

DDR4 SDRAM的x4/x8/x16器件都是6个电气列,组成两组,每一列三个电气列。每组电气列之间可能会有不出球的空列。这些不出球的电气列共有3列。电器列共包含信号出球与电源地出球,但是因为机械补偿仍然会有一些没有激活的出球作为附加列。

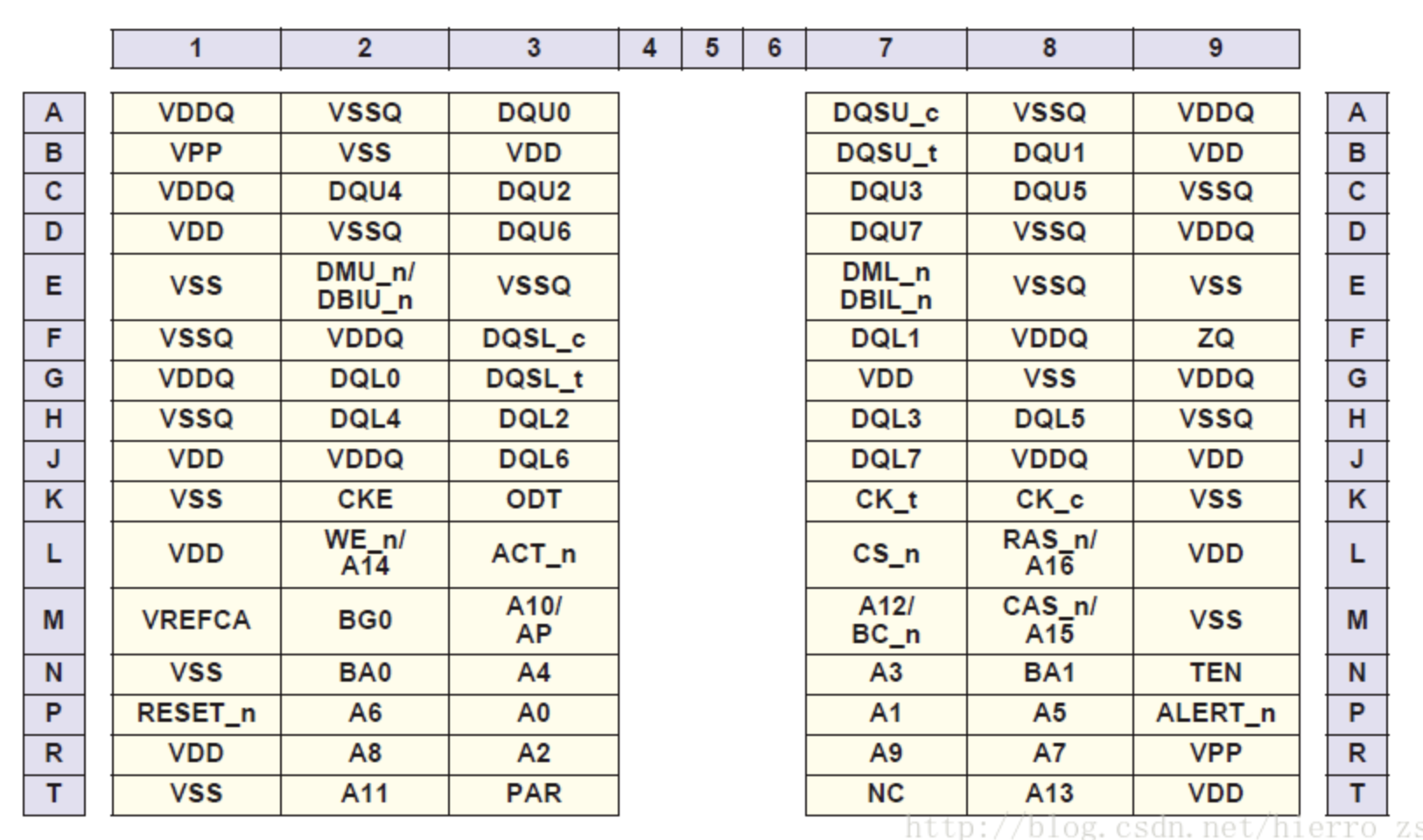

2.4 使用MO-207出球策略的DDR4 SDRAM x4/x8器件

- NOTE 1 这些引脚在x4配置中是不会连接的

- NOTE 2 TDQS_t 在 x4 配置中是不可用的

- NOTE 3 TDQS_c 在 x4 配置中是不可用的

- NOTE 4 A17 仅在x4配置中使用

- NOTE 5 这些引脚是用于堆叠组件的,例如3DS. 在mono封装中,这些引脚没有连接

- NOTE 6 ODT1 / CKE1 /CS1_n are 仅在DDP中同时使用

- NOTE 7 TEN 仅在8Gb或以下选择使用. 若TEN功能未开启,则此引脚不可用

2.5 使用MO-207出球策略的DDR4 SDRAM x16器件

2.6 引脚描述

NOTE 输入引脚(BG0-BG1,BA0-BA1, A0-A17, ACT_n, RAS_n/A16, CAS_n/A15, WE_n/A14, CS_n, CKE, ODT, and RESET_n)不支持终结电阻。

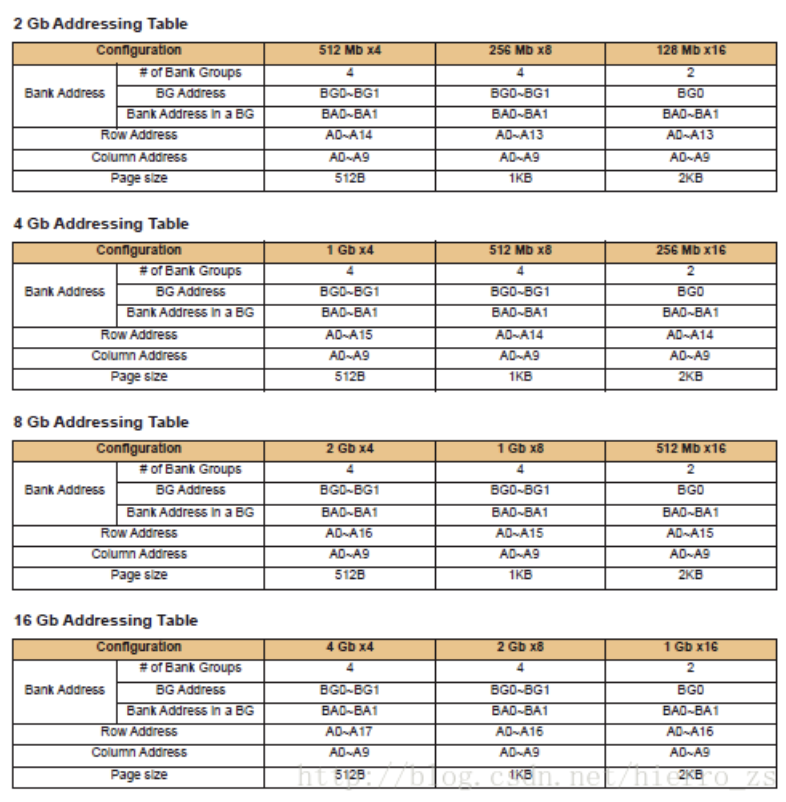

2.7 DDR SDRAM的寻址空间

原文:CSDN

作者:hierro_sic

相关文章推荐

- DDR 学习时间:学习 Micron DDR4 TN-40-07: DDR4 功耗估算 (2)

- DDR 学习时间 (Part C - 1):DFI 协议简介、演进和协议下载

- DDR 学习时间:学习 Micron DDR4 TN-40-07: DDR4 功耗估算 (1)

- 一些PCIE知识整理——PCIe体系的拓扑结构

- 一些PCIE知识整理——带宽计算

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。