英伟达发布了一个以自家内部数据为基础训练而成的定制大语言模型——ChipNeMo,可以帮助工程师完成与芯片设计相关的任务。

这厢,黄仁勋穿着花背心、拿着手绢出席年会。那厢,Sam Altman 正在筹措数十亿资金,以建立新 AI 芯片公司。

春风得意与雄心勃勃的对比之下,正是当前 AI 芯片领域的真实写照,算力至上的时代,英伟达几乎是卡所有人脖子。所以,越来越多 AI 芯片初创企业如雨后春笋般拔地而起,更有甚者高喊对标、替代英伟达,同时微软、谷歌等大厂也开始更加勤奋地自研芯片。

诚然,自进入智能时代以来,芯片已经成为了一众科技巨头的「阿喀琉斯之踵」,而半导体行业的高门槛也使得这一技术围城很难被轻易攻克。除了华为已经「现身说法」的生产环节外,半导体设计同样极具挑战性。尤其是在电子芯片逼近摩尔定律极限,算力需求却持续走高之际,如何在先进制程上发挥更高性能就成为了 AI 芯片设计的重要挑战。

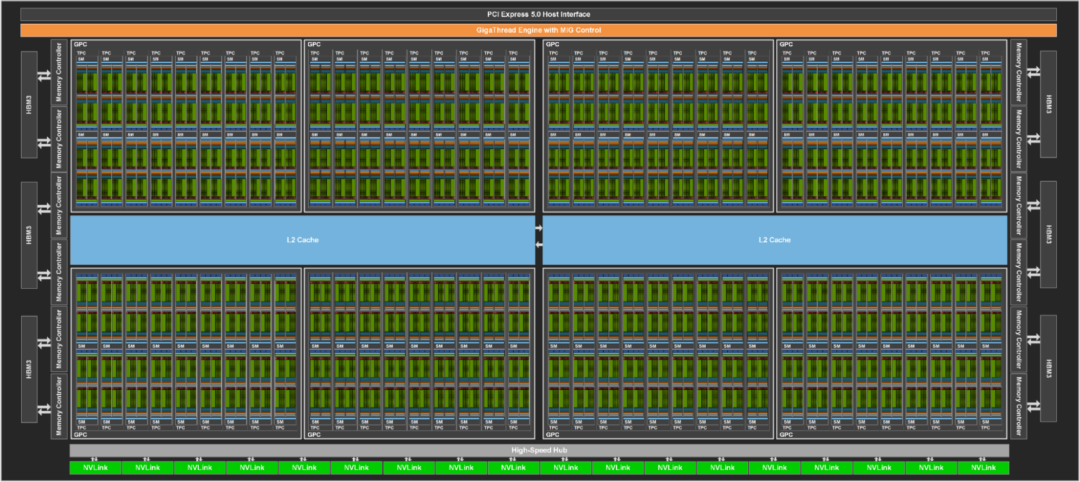

具有 144 个 SM 的 GH100 完整 GPU

如上图所示,在显微镜下,NVIDIA H100 Tensor Core GPU 这样的先进芯片看起来就像一个精心规划的城市,由数百亿个晶体管组成,比人的头发丝还细 1 万倍的「街道」将这些晶体管连接起来。而整个城市的搭建,需要多个工程团队协作两年才能完成。

其中,各个部门分工协作,一些定义芯片的整体架构,一些负责各种超小型电路的设计与布局,还有一些负责测试工作。每项工作都需要采取专门的方法、软件程序和计算机语言,复杂程度可见一斑,而这也恰恰是芯片厂商的技术护城河。

有意思的是,凭借最强 AI 芯片疯狂掏空大厂钱包的英伟达,也开始琢磨起利用 AI 更「轻松」地赚钱。不久前,英伟达发布了一个以自家内部数据为基础训练而成的定制大语言模型——ChipNeMo,可以帮助工程师完成与芯片设计相关的任务,目前仅供内部使用。

该成果已收录于 arXiv,论文地址:

https://arxiv.org/abs/2311.00176

关注公众号,后台回复「ChipNeMo」即可下载论文

基于领域自适应技术为芯片设计定制 LLM

英伟达的研究人员并没有选择直接部署已有的 LLMs,而是基于领域自适应技术 ,利用 NVIDIA NeMo 对基础模型 (70 亿参数、130 亿参数、700 亿参数的 LLaMA2) 进行了定制。

注:NVIDIA NeMo 是一款端到端云原生框架,可以灵活地构建、定制和部署生成式 AI 模型,包含训练和推理框架、护栏工具包、数据管护工具和预训练模型

ChipNeMo 采用多种领域自适应技术 (domain adaptation techniques) 以使 LLMs 适应芯片设计领域,其中包括:

- 用于芯片设计数据的定制分词器 (custom tokenizers)

- 使用大量领域数据进行的领域自适应预训练 (domain-adaptive continued pretraining)

- 带有领域特定任务的监督微调 (supervised fine-tuning with domain-specific instructions)

- 使用经过微调的检索模型 (domain-adapted retrieval models)

- 检索增强生成 (RAG)

研究人员通过工程助手聊天机器人、EDA 脚本生成以及故障总结和分析三个具体应用,对 ChipNeMo 进行实测评估。

ChipNeMo 训练流程

其中,领域特定的分词器通过定制规则,能够提高对特定术语的标记化效率 (tokenization efficiency)。研究人员将 ChipNeMo 预训练的分词器调整为适应该研究的芯片设计数据集,仅为领域特定术语添加新的标记。

在领域自适应预训练 (DAPT) 期间,研究人员将英伟达内部的芯片设计数据与公开数据集结合,经过收集、清洗、过滤,内部数据训练语料库共拥有 231 亿个 token,涵盖设计、验证、基础设施,以及相关的内部文档。

在进行有领域特定指令的监督微调 (SFT) 时,研究人员使用公开的通用聊天指令数据集进行多轮聊天,并结合少量领域特定指令数据集对 ChipNeMo 基础模型进行 SFT,生成 ChipNeMo Chat 模型。

此外,研究人员通过使用 Tevatron 框架生成了 3000 个特定领域的自动生成样本,对 e5 小型无监督模型进行微调,从而创建了该研究的领域适应检索模型。

为了解决 ChatBot 普遍存在的「幻觉」问题,研究人员采用了检索增强生成 (RAG),从而提高特定领域问题的答案质量。

具体而言,RAG 从数据库中检索相关段落,将其与问题一起包含在提示中,从而使 LLM 能够更加基于事实地生成更准确的答案。同时,研究人员发现,通过使用适量的领域特定训练数据对无监督预训练稠密检索模型进行微调,可以显著提高检索的准确性。

RAG 实现过程

此外,领域自适应技术除了能够令大语言模型更加适配芯片设计领域外,还能够减少模型参数高达 5 倍,从而减少推理成本。

值得一提的是,所有模型均使用 128 个 A100 GPU 进行训练,研究人员估测了 ChipNeMo 领域自适应预训练的成本,如下表所示。其中,DAPT 的占比不足从零开始预训练基础模型总成本的 1.5%。

130亿参数的定制模型超越LLaMA2

研究人员在三种芯片设计应用中对 ChipNeMo 的实际性能进行监测评估,分别是工程助手聊天机器人 (Engineering Assistant Chatbot)、EDA 脚本生成 (EDA Script Generation)、Bug 总结与分析 (Bug Summarization and Analysis)。

首先,工程助手聊天机器人可以帮助芯片设计工程师回答有关架构、设计、验证等方面的问题,避免其基于错误的假设而编写代码或调试其不熟悉的代码,从而提高生产力。此外,Chatbot 还能从内部设计文档、代码、有关设计的其他记录数据、以及技术沟通留痕(电子邮件、公司即时通信等)中提取相关知识,帮助工程师提高工作效率。

工程助手聊天机器人示例

其次,EDA 脚本编写是工业芯片设计流程中的重要环节。过去,工程师需要学习内部脚本库、查阅工具文档,并调试脚本,占用大量时间。所以,研究人员从自然语言任务描述中,基于 Tool1 (Python)、Tool2 (TCL) 生成了两种不同类型的脚本。工程师可以在同一界面查询模型并运行生成的代码,同时还能看到还需要多少次更正才能获得一个可运行的脚本。

LLM 脚本生成器与 EDA 工具的集成

EDA 脚本生成器示例

第三,针对 Bug 总结与分析,研究人员利用英伟达内部的 Bug 数据库 NVBugs,还构建了一个领域特定的 SFT 数据集。

Bug 总结与分析示例

研究人员针对芯片设计知识、EDA 脚本、Bug 分析、电路设计和 MMLU(Mean Multi-Language Understanding,多语言理解均值)对 ChipNeMo 的性能进行了对比评估。

结果显示,ChipNeMo 的性能随基础模型的参数规模大小而提高,ChipNeMo 领域自适应预训练在基础模型上提供了显著的性能改善。同时,最优 ChipNeMo 模型在所有基准测试上的性能均优于 GPT-3.5,在设计知识和 Bug 基准测试上优于 GPT-4。

此外,在芯片设计任务中,只有 130 亿个参数的定制 ChipNeMo 模型的性能达到或超过了更大的通用大语言模型(例如包含 700 亿个参数的 LLaMA2)。

大模型设计芯片还真不是新鲜事

目前,ChipNeMo 仅供内部使用,并且由于使用了英伟达内部数据进行训练,未来对外开源的可能性或许也不大。尽管如此,英伟达作为显卡巨头,借助大语言模型优化工作流程的这一举动,对行业而言还是颇具启发意义的。

一方面,芯片设计的高门槛不仅体现在技术壁垒上,同时也体现在经验与成本方面。从设计到落地、再到投产的每一个步骤,都可能成为行业竞争中的「超车点」。而大模型的加入,对一些起步较晚、自身经验积累不足的初创企业企业而言,可以在更短的时间内「博采众长」,甚至可以看作是直接聘请了一位经验丰富的工程师。不过,这需要更多的开源数据与模型支撑。

另一方面,在大模型以 Chatbot 的形式持续惊艳世人的同时,很多企业都想基于开源模型,研发更加契合自身行业特点与业务属性的大语言模型,但大多都因为难以解决高昂的训练成本而打了退堂鼓,同时还要考虑训练数据安全问题。这一点也在英伟达身上再次得到印证,训练 ChipNeMo 所用的 128 个 A100 GPU 就不是所有企业能够轻易获得的。

值得注意的是,ChipNeMo 其实并不是大模型在芯片领域的首次落脚。

早在 2023 年 5 月,纽约大学坦登工程学院的研究人员就已经通过与 AI「对话」,首次实现了由人工智能来设计一种微处理器芯片。

论文链接:

https://arxiv.org/abs/2305.13243

关注公众号,后台回复「Chip-Chat」即可下载论文

纽约大学教授 Hammond Pearce 在接受采访时介绍道:“我根本就不是一个芯片设计专家。这是我设计的第一个芯片。我认为这是这件事令人印象深刻的原因之一。”

具体而言,研究人员通过 124 次对话成功让 GPT-4 设计出一个 8 位累加器微处理器,经由 Skywater 130nm shuttle 进行制造。

就在这一研究成果发布的第二天,中国科学院计算技术研究所在 arXiv 上发布了 ChipGPT,再度掀起讨论热潮。研究人员表示,ChipGPT 是一种尝试,旨在探索使用自然语言芯片规范自动生成逻辑设计的可行性,并利用当前的 LLM 降低传统上需要高度专业知识和人工劳动的硬件前端设计成本。

论文地址:

https://arxiv.org/abs/2305.14019

研究结论表明,ChipChat 与传统敏捷方法相比,代码量可以减少 5.32-9.25 倍。在优化面积模式下,ChipGPT 的面积减少最大可达 47%, 比原始 ChatGPT 模型减少更多。

此外,基于 AI 优化芯片设计也并非新概念。除了英伟达之外,谷歌等大厂均有布局。谷歌团队曾在 2021年 发布论文《A graph placement methodology for fast chip design》,介绍了一种用于芯片版面规划的深度强化学习方案。英伟达也曾在 2022 年发布基于深度增强学习的电路设计方法 PrefixRL。

不过,ChipNeMo 历经沉淀,且为定制模型,在应用的契合度与效率层面势必都将更具优势。在这个 AI 芯片内卷的时代,英伟达作为遥遥领先的「卷王」,竟然还想着用 AI 提升效率,或许也是感受到了追赶者带来的压力?

参考资料:

https://blogs.nvidia.cn/2023/...

https://mp.weixin.qq.com/s/cR...

https://mp.weixin.qq.com/s/54...