4 DDR4 SDRAM命令描述与操作

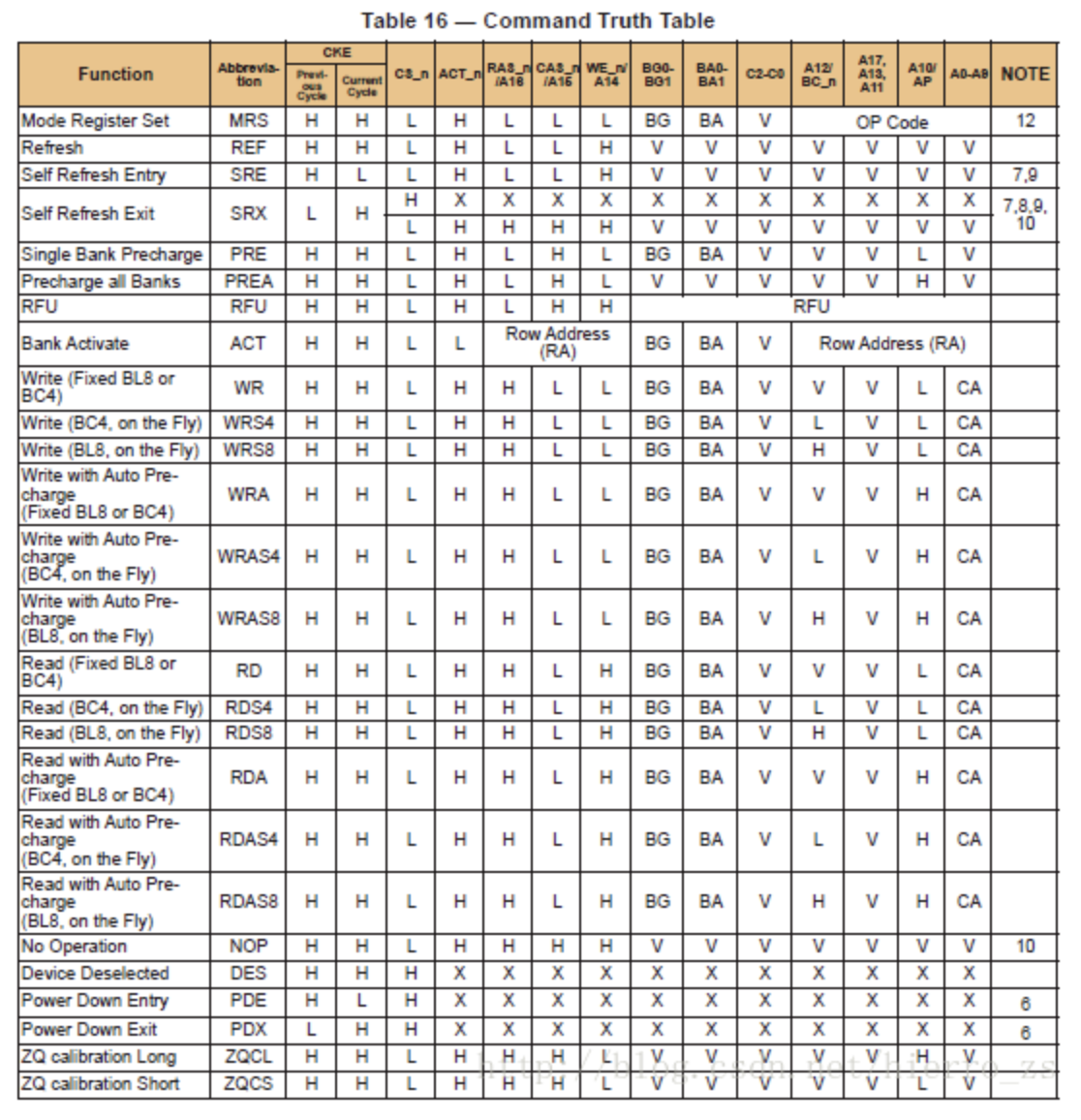

4.1 命令真值表

Note 1,2,3 and 4 适用于真值表中所有命令

Note 5 适用于读写命令

[BG=Bank组地址, BA=Bank地址, RA=Row地址, CA=Column地址, BC_n=Burst长度, X=不关心, V=需有效].

- NOTE 1 所有DDR4 SDRAM命令都是由在ck时钟上升沿的时刻CS_n,ACT_n,RAS_n/A16,CAS_n/A15,WE_n/A14以及CKE的状态确定的。BG, BA,RA与CA的有效位是由设备密度以及配置确定的。当ACT_n为高电平时,RAS_n/A16, CAS_n/A15与WE_n/A14是分别用作命令控制信号RAS_n, CAS_n与WE_n的;当ACT_n为低电平时,RAS_n/A16, CAS_n/A15与WE_n/A14是分别用作地址信号A16, A15与A14的。

- NOTE 2 RESET_n是低电平有效的,异步复位信号,在任何其他命令中此信号都必须为高电平

- NOTE 3 BANK组地址(BG)与BANK地址(BA)可确定是哪一个bank被操作。在MRS命令中,BG与BA用来定位模式寄存器。

- NOTE 4 “V”表示此信号此时需要一个“0”或者“1”,“X”表示此信号此时不需要任何逻辑值,可以为悬空信号。

- NOTE 5 读请求或者写请求的burst类型,仅在模式寄存器中被定义,且不可在访问过程中被打断。

- NOTE 6 Power Down模式中,不发送任何Refresh命令。

- NOTE 7 ODT的状态并不影响此真值表中的任何状态,且在Self-refresh模式中ODT功能不可用。

- NOTE 8 由控制器来保证退出Self-refresh命令的同步。

- NOTE 9 在Self-refresh模式中必须保持VREF(VrefCA)的状态,且在Self-refresh结束后的TBD个ck时钟周期内都不能出现write leveling的触发命令

- NOTE 10 无操作命令可用在DDR4 SDRAM的Gear Down模式与退出最大低功耗模式时。

- NOTE 11 CKE的传输可参考CKE真值表

- NOTE 12 MRS命令中的A17是保留位,且由设备密度与配置确定。

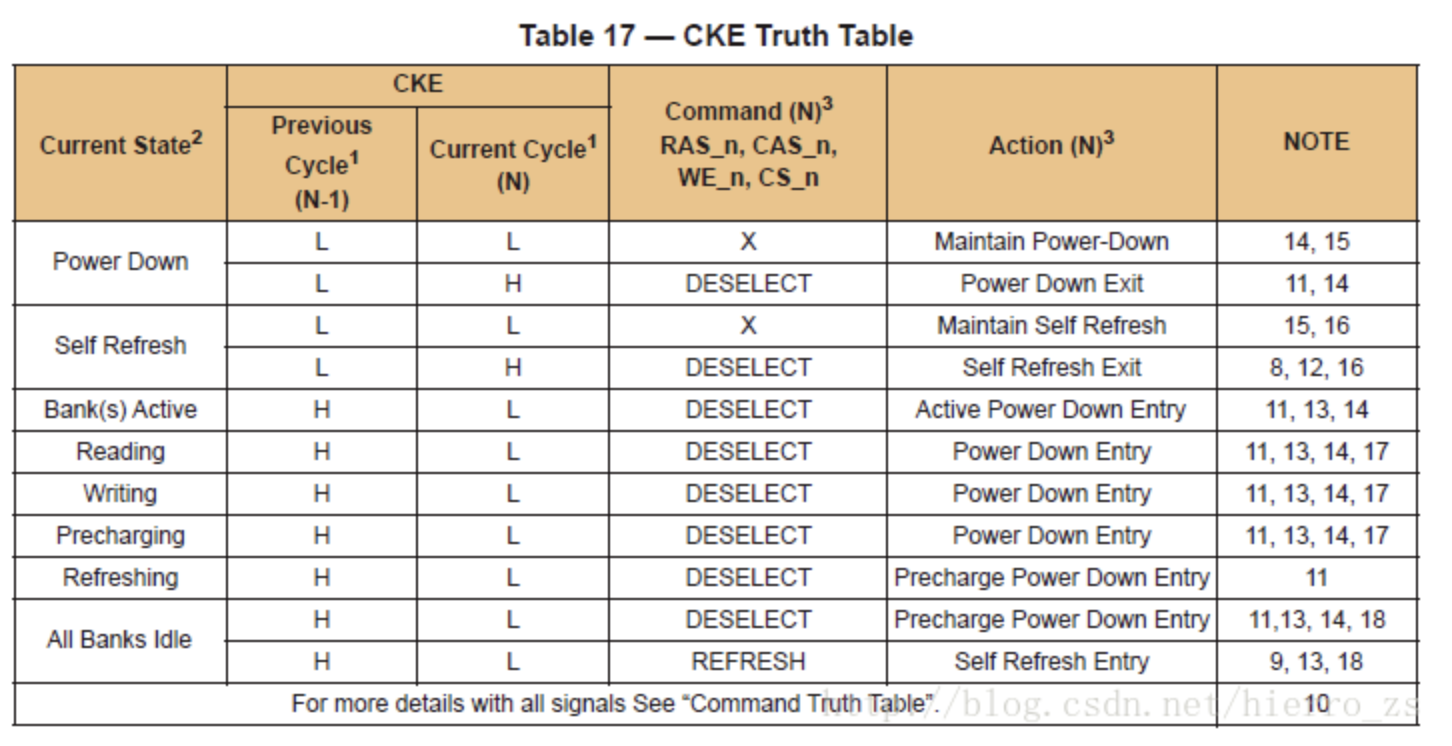

4.2 CKE真值表

- NOTE 1 CKE(N)表示在N时刻CKE信号的状态;CKE(N-1)表示在N时刻前一拍的CKE信号的状态

- NOTE 2 当前状态表示在DDR4 SDRAM的N时刻前的状态

- NOTE 3 Command(N)表示在N时刻锁存的命令。ACTION(N)为COMMAND(N)触发的动作。ODT操作没有包含在此表内。

- NOTE 4 此表中没有提及的状态与序列都是非法或保留的,除非在此文档的其他位置有明确描述。

- NOTE 5 ODT的状态并不影响此真值表中的任何状态,且在Self-refresh模式中ODT功能不可用。

- NOTE 6 在任何的CKE传输过程中(CKE H->L或者CKE L->H),都必须满足CKE电平保持时间(1nCK至tCKEmin)。

- NOTE 7 DESLECT与NOP命令在命令真值表中有定义

- NOTE 8 在退出Self-refresh命令中,在tXS时间内必须每一个时钟周期都发射DESLECT命令。tXSDLL满足之后才可以发射READ或ODT命令。

- NOTE 9 Self-refresh命令仅可在所有bank都处于空闲状态时发射

- NOTE 10 必须为命令真值表中定义的合法命令

- NOTE 11 在Power Down进入或者退出时,仅可发射DESLECT命令

- NOTE 12 在Self-refresh退出时仅可发送DESLECT,在Gear Down或者最大低功耗退出时仅不然,而NOP对于前面两种状态的都是可以的。

- NOTE 13 在读写操作时,不可以进入Self-refresh状态。在4.27章节“Self-refresh操作”与4.28章节“Power Down模式”有更多细节。

- NOTE 14 Power Down模式中不执行任何刷新操作

- NOTE 15 Self-refresh与Power Down状态中的X表示不关心状态(包含悬空状态),对于地址引脚也是同样。

- NOTE 16 在Self-refresh操作中VPP与VREFCA必须保持,且Self-refresh结束后的TBD个ck时钟周期内都不能出现写命令以及write leveling的触发命令

- NOTE 17 如果在写命令、读命令或者Precharge命令结束时所有的BANK都已经关闭,那么进入Precharge Power Down模式,否则进入Active Power Down模式

- NOTE 18 空闲模式表示所有的BANK都已经关闭(满足tRP、tDAL时序),Burst进程中没有数据,CKE为高电平,所有时序参数都满足(tMRD, tMOD, tRFC, tZQinit, tZQoper, tZQCS等),以及Self-refresh退出时序和Power Down退出时序满足(tXS、tXP)。

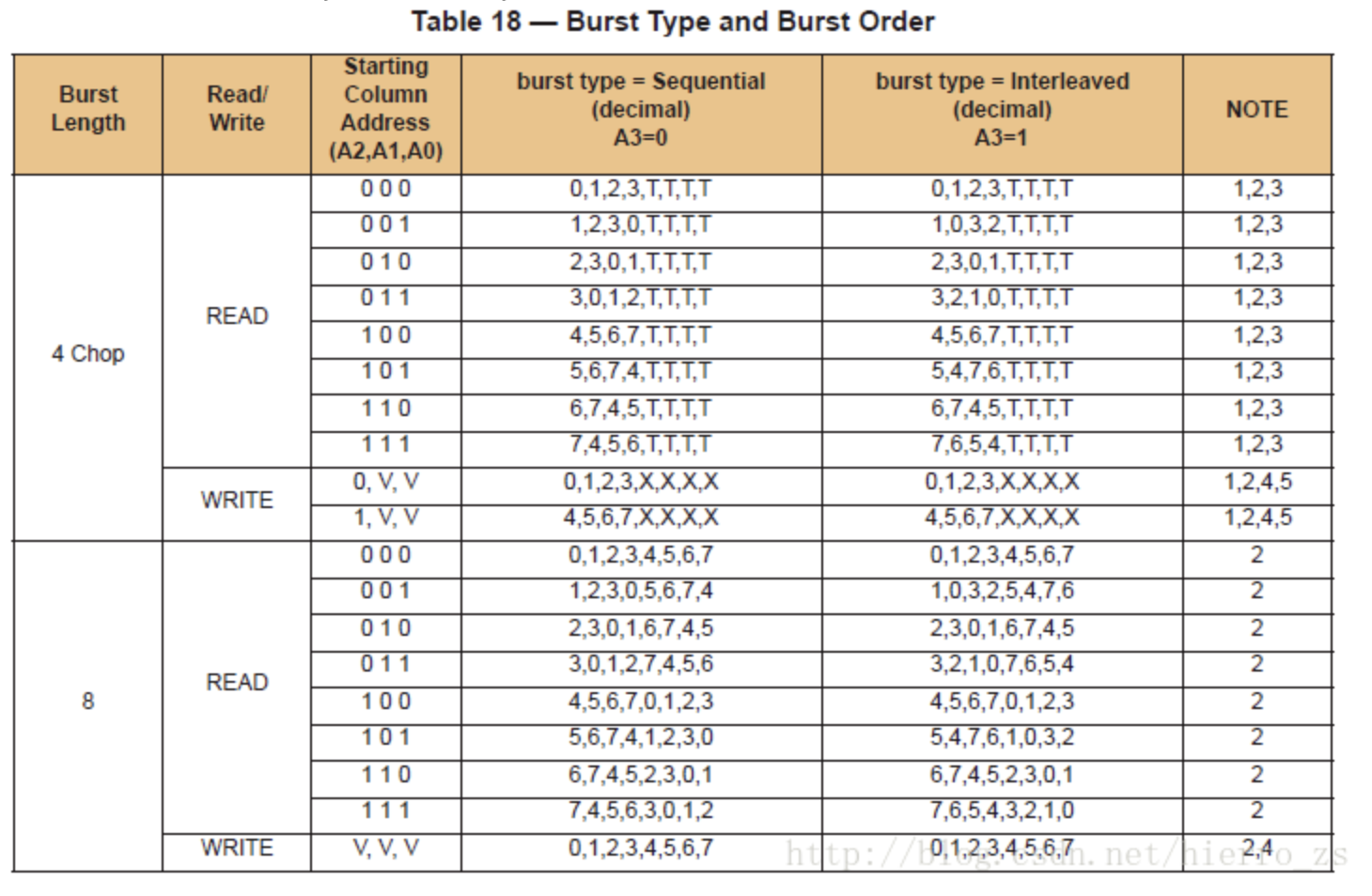

4.3 Bust类型、长度与顺序

- NOTE 1 一旦burst长度固定为4,内部的写操作将比BL8模式下提早开始两个周期。这就意味着,tWR与tWTR的起始点都将提前两个周期。如果采用OTF模式,通过A12来确定burst长度,那么内部写操作的起始点与BL8模式下的起始点都将相同。也就是说在OTF模式下,,tWR与tWTR的起始点不会提前两个周期。

- NOTE 2 0…7为CA[2:0]的值,此位可确定读burst的起始位置。

- NOTE 3 数据与选通信号的输出驱动都将处于高阻状态。

- NOTE 4 V:表示有效的逻辑值,但在具体操作中0或1栋可能出现

- NOTE 5 X:不关心,可为悬空,或者是任何状态。

4.3.1 CRC开启时的BL8 burst顺序

DDR4 SDRAM在CRC开启状态时,所有BL8的burst顺序都是用[A2:A1:A0=0:0:0]。

4.4 DLL-off模式与DLL打开关闭流程

4.4.1 DLL打开关闭流程

通过配置MR1寄存器的A0位可使得DDR4 SDRAM的DLL-off模式;当A0位被写成1时,会将DLL禁止,以方便后面的操作。

4.4.2 DLL开启到DLL关闭的流程

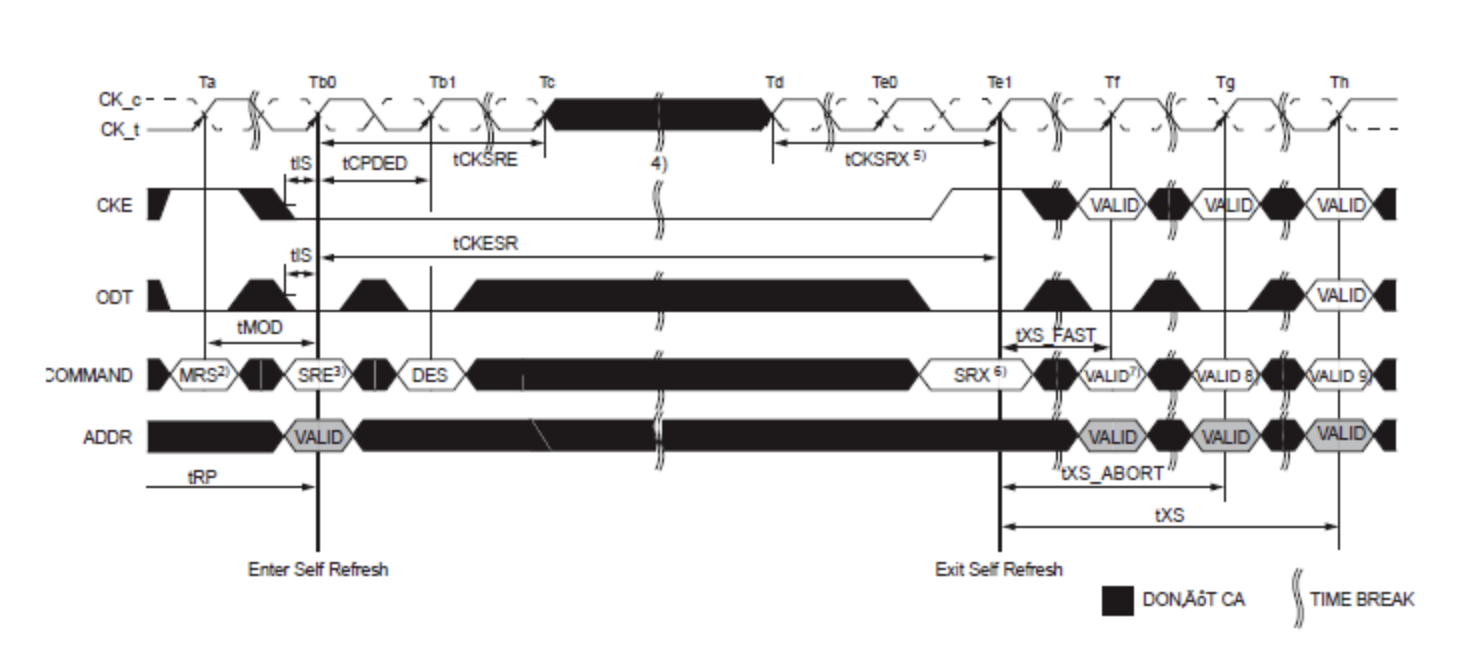

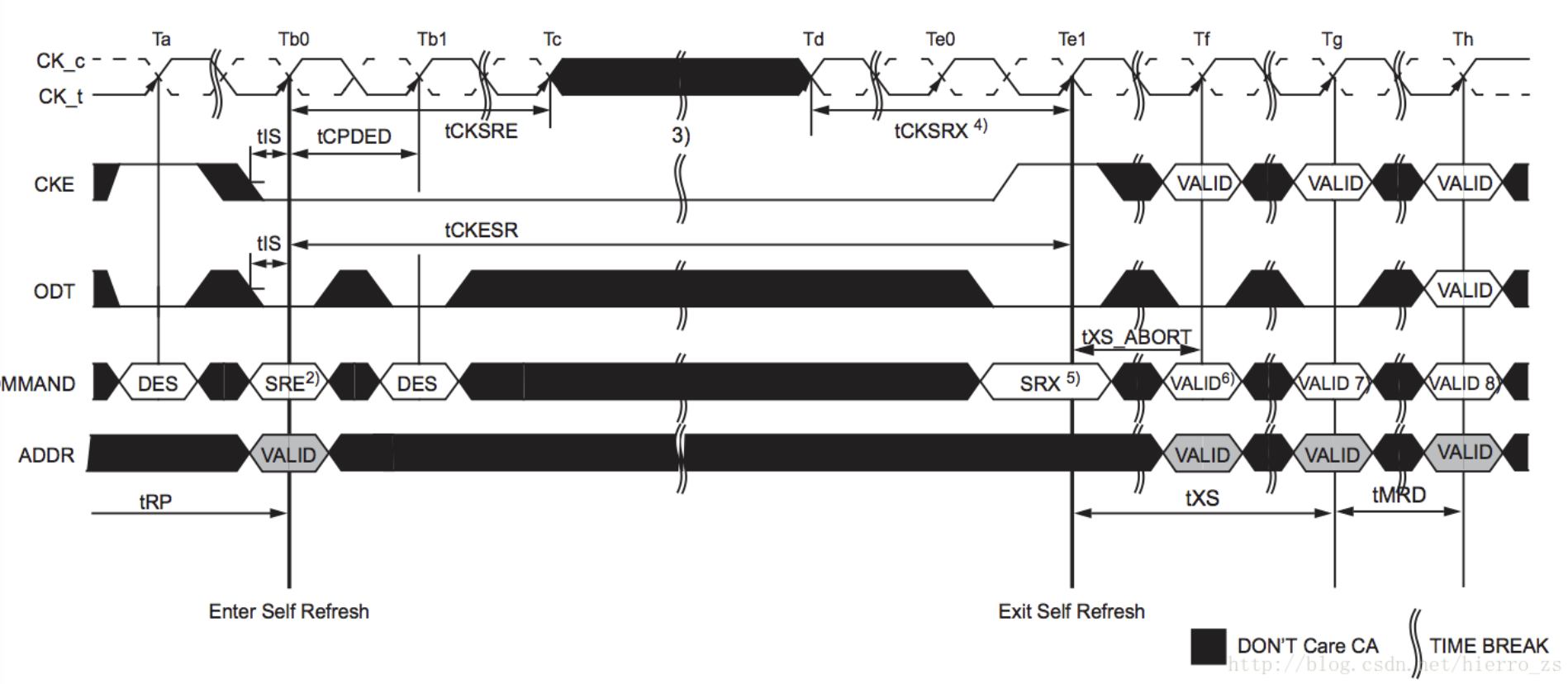

切换DLL的开启与关闭时,需要在Self-refresh时改变时钟频率。以下流程为切换流程:

- 从空闲状态开始,即所有BANK预充电,所有时序参数满足,在通过MRS修改MR1来关闭DLL之前,所有DRAMs的ODT电阻、RTT_Nom都必须处于高阻状态。

- 将MR1的A0为设置为1,禁止DLL

- 等待tMOD

- 进入Self-refresh模式,等待tCKSRE时间满足

- 改变时钟频率,参考4.6节的“改变输入时钟频率”

- 等待时钟稳定,DRAM输入端至少等待tCKSRX时间

- 发出Self-refresh退出命令,在MRS名之后的tMOD时间内CKE信号都必须保持为高电平。此外,若在Self-refresh模式下任何ODT特性被开启,在MRS命令后的tMOD时间内ODT信号都必须保持为低电平。当RTT_Nom功能被关闭时,那么在Self-refresh模式下ODT信号是不关心的。

等待tXS_Fast或tXS_Abort或tXS,然后对模式寄存器配置合适的值。(特别是CL、CWL、WR,在tXS_Fast之后将发送ZQCL命令)

- tXS -ACT, PRE, PREA, REF, SRE, PDE, WR, WRS4, WRS8, WRA, WRAS4, WRAS8, RD, RDS4, RDS8, RDA, RDAS4, RDAS8

- tXS_Fast -ZQCL, ZQCS, MRS命令。在MRS命令中仅可以改变MR0中的DRAM CL、WR/WTR,MR2中的CWL,MR3中的Gear Down,并不是所有课寻址的模式寄存器都可以改变。其他的模式寄存器都必须满足tXS时间。

- tXS_Abort - 如果MR4中的A9位使能了,那么DRAM将忽略所有正在进行的刷新命令,并且不增加任何刷新计数器。控制器可在tXS_Abort时间之后发射有效命令。一旦退出了Self-refresh模式,DDR4 DRAM需要至少执行一个refresh命令,来重新进入Self-refresh模式。此需求与使用MRS命令设置Self-refresh abort模式无关。等待tMOD时间,DRAM既可执行下一命令。

- 初始与IDLE状态,RTT保持稳定状态

- 禁止DLL,通过配置MR1中的A0为0

- 进入Self-refresh

- 改变频率

- 在tCKSRX时间内时钟稳定

- 退出Self-refresh

4.4.3 DDL从关闭到打开的流程

在Self-refresh过程中需要修改时钟频率时,会将DLL的状态由关闭变为打开。

- 从空闲状态开始,即所有BANK预充电,所有时序参数满足,在通过MRS修改MR1来关闭DLL之前,所有DRAMs的ODT电阻、RTT_Nom都必须处于高阻状态。

- 进入Self-refresh模式,等待tCKSRE时间满足

- 改变时钟频率,可参考第4.6章节的“改变输入时钟频率”

- 等待DRAM输入时钟稳定,至少tCKSRX时间

- 由Self-refresh退出命令开始,CKE信号必须保持锁存为高电平,直到DLL复位命令之后满足tDLLK时间。此外,此外,若在Self-refresh模式下任何ODT特性被开启,在MRS命令后的tMOD时间内ODT信号都必须保持为低电平。当RTT_Nom功能被关闭时,那么在Self-refresh模式下ODT信号是不关心的。

- 由MR4中的A9决定,在配置MR1寄存器的A0位高电平来使能DLL时,满足的时间参数为tXS或tXS_ABORT。

- 当配置MR0中的A8为1时,等待tMRD时间

- 当配置MR寄存器后,必须等待tMRD时间,尤其是在更新CL、CWL以及WR时。在MRS与ZQCL命令发出之后,需要等待tMOD或者时tDLLK时间。

- 当DRAM准备好接受下一个命令时,需要等待tMOD。当需要一个锁定的DLL时,需要在DLL复位之后等待tDLLK时间。此外,等待tZQoper时间来满足ZQCL命令的时间要求。

- 由初始状态开始

- 进入SR

- 改变时钟频率

- 时钟需要在tCKSRX内稳定

- 推出SR

- 配置MR1的A0为1,来开启DLL

- 触发DLL复位

- 在tDLLK时间后更新其他的MR寄存器值(图中未显示)

- 在tDLLK时间后,DRAM可执行其他的命令(图中未显示)

原文:CSDN

作者:hierro_sic

相关文章推荐

- JESD79-4 第3章 功能描述

- JESD79-4 第2章 DDR4 SDRAM 的引脚封装与寻址

- DDR 学习时间:学习 Micron DDR4 TN-40-07: DDR4 功耗估算 (2)

- DDR 学习时间 (Part C - 1):DFI 协议简介、演进和协议下载

- DDR 学习时间:学习 Micron DDR4 TN-40-07: DDR4 功耗估算 (1)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。