本期以 Micron 的 DDR3 Model 为例,介绍模型如何下载和如何仿真,以及对模型中的各个文件进行解析。

本系列连载于 OpenIC SIG,除了 DDR 学习时间专栏外,OICG 目前正在陆续上线 HDLBits 中文导学的优化版本,欢迎关注/支持/加入我们

DDR 学习时间 - OpenIC SIG 开源数字IC技术分享

DDR 行为仿真模型

DDR 行为仿真模型可以在仿真中模拟 DRAM 时钟周期级别的行为,用于测试和 DRAM 交互的数字逻辑的功能和时序(后仿),关于仿真模型的一些概论可以通过以下这篇文章了解:

LogicJitterGibbs:DDR 学习时间 (Part Z - 1):芯片设计中的 DDR 模型杂谈

市面上主流的仿真模型包括 Cadance 的 Denali Model ,DRAM 芯片原厂提供的模型(比如 Micron)等等。其中有些模型需要收费,有些是 DDR IP 的赠品,还有些则可以免费下载。

免费使用的模型,想要一窥其中实现就不太可能了,往往是加密的,比如 Micron 的 DDR4 Model。不过好在 Micron 的 DDR3/4 模型都可以免费下载,DDR3 模型还是非加密的。

下载

在 Micron 官网搜索 Model 可以找到,本文也提供了下载链接:

DDR4 Model

Micron DDR4 模型是一个免费,核心代码加密的行为级模型,基于 SystemVerilog 开发。

基于加密的模型,镁光提供了一个示例 testbench 以及在三种仿真器上运行 testbench 的脚本,三种仿真器分别是来自御三家的:VCS/NCVerilog/Modelsim。

DDR3 Model

Micron DDR3 模型是一个 Verilog 编写的未加密的模型,因为 DDR3 模型没有加密,同时文件结构更加简单,被用于很多开源项目的仿真中,本期文章首先深入分析并运行 DDR3 Model。

DDR3 Model 文件分析

DDR3 Model 整个目录中包括以下几类文件:

- DDR3 Model

- 示例 Testbench

- DDR3 时序参数头文件

- Readme

Readme

通过 Readme 文件,我们可以知道 DDR3 model 中有哪些支持定义的变量,这些变量在编译时通过 define 传入,比如使用 VCS 编译时,定义 DDR3 速度等级为 sg25,使用如下命令

vcs +define+sg25 ddr3.v

可以定义的变量有:

- DDR3 颗粒大小,1024/2048/4096/8192Mb

- DDR3 速度等级,也就是平时说的 DDR3 数据速率,比如 sg25 对应 DDR3-800

- DDR3 颗粒位宽,x4/x8/x16

- DDR3 的 rank 数量,如果支持的话

- DDR3 内存条的类型,UDIMM/RDIMM/SODIMM

- 是否支持 ECC

- 仿真时为模型提供的内存大小,如果定义最大内存则仿真的速度也会越快

DDR3 Model

ddr3.v 是 DDR3 颗粒的模型,可以将其例化到 Testbench 中与待测试设计连接,就好比给待测试模块连到一个实际的 ddr3 颗粒。

目录中其他几个 verilog 文件,则是 ddr3 颗粒以不同方式封装后的 DDR3 内存条/内存模块模型,其中例化了 ddr3.v 中的 module。在编译时指定相关文件和宏定义后调用。

- ddr3_dimm.v 是 DDR3 内存条(Dual-inline-memory-module)模型

- ddr3_mcp.v 是多晶圆封装(Multi-Chip Package)后的 DDR3 颗粒模型

- ddr3_module.v 是多 rank ddr3 内存条模型

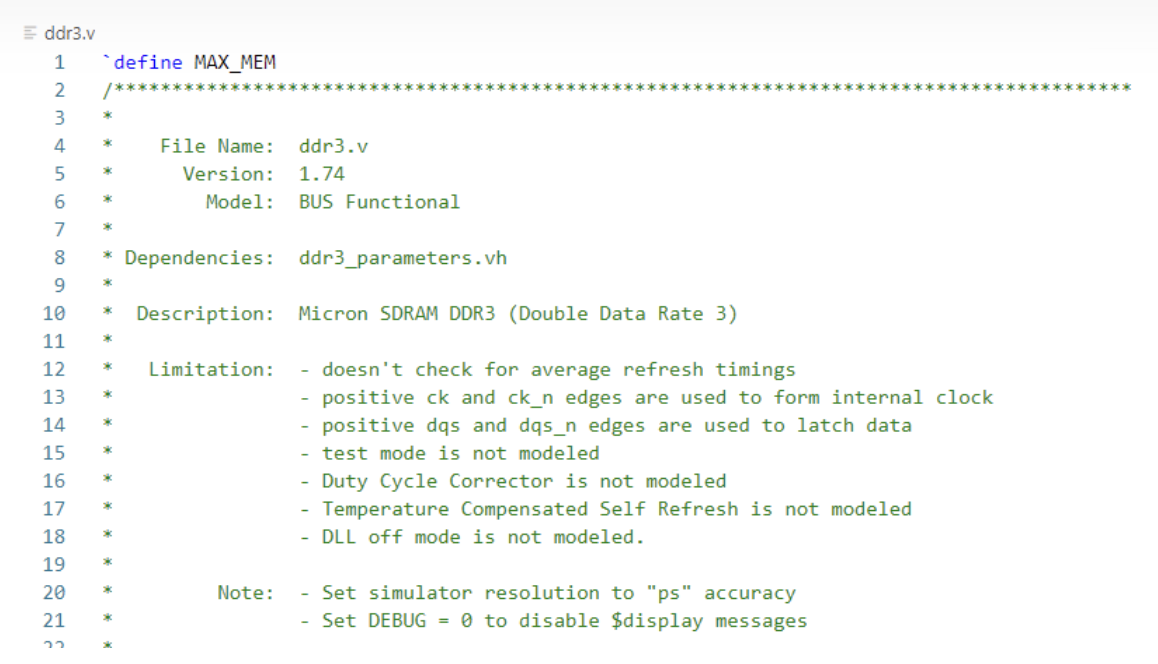

ddr3.v 的开头的注释列出了模型不支持建模的特性

DDR3 示例 Testbench

tb.v 中定义了用于仿真的各类 task 以及 function,并 include subtest.vh。subtest.vh 是真正的 testbench 文件,进行 DDR 的初始化和读写操作,并对读写的数据进行对比操作。

DDR3 参数头文件

参数头文件(vh 文件)中定义了各种颗粒大小的 DDR3 的时序参数,会根据传入的宏定义 include 不同的参数头文件。

这样设计是因为不同大小的 DDR3 颗粒的时序参数可能不同。

运行 DDR3 Model 仿真

使用

- 解压文件

- 启动仿真工具,运行 Micron 的仿真示例

Micron 在 Readme.txt 中提供了御三家仿真工具的启动命令,如果读者有相应的工具和配置好的环境,可以直接启动一个仿真。

simulator command line

--------- ------------

ModelSim vlog +define+sg25 ddr3.v

VCS vcs +define+sg25 ddr3.v

NC-Verilog ncverilog +define+sg25 ddr3.v使用 IVerilog+GTKWAVE 仿真

但如果你像笔者一样,没有相应的环境,或者懒得启动自己的 Linux 虚拟机,想在 Windos 上仿真,那么比较方便的方法是使用支持 Windows 平台,并且小巧开源的 IVerilog+GTKWAVE 工具。

笔者把相关的教程放在了本文的最后,安装使用都是比较简单的。笔者使用的是最新的 IVerilog 版本。

Icarus Verilog version 12.0 (devel) (s20150603-1539-g2693dd32b)

仿真分为几步,首先稍许改动 Testbench

1 改动 subtest.v

在 subtest.v 中增加 dump 波形的命令

initial

begin

$dumpfile("wave_ddr3.vcd"); //生成的vcd文件名称

$dumpvars(0, tb); //tb 就是示例里 tb模块名称

end再给 TZQINIT 手动定义一个初始值,这个值本身应该会由 ddr3.v 中根据时钟频率动态定义,但至少在笔者使用的 iverilog 版本中,这个变量会一直为 x 态,所以为这个常量手动添加了初始值,本身不会影响仿真。

initial

begin

TZQINIT = 512;//add by fan, to fix x on TZQINIT

end2 编译文件

D:\iverilog\bin\iverilog.exe -o wave_ddr3 -D den1024Mb -D x8 -D sg25 -g2012 -I .. ..\ddr3.v ..\tb.v

这里解释下几个主要的参数

- -D 表示 define 宏,这里需要传入所需要 DDR3 模型的位宽 (x8) 、速度等级 (sg25) 以及颗粒大小 (den1024Mb),缺少这些信息会报错

- -I 表示头文件 vh 所在的路径

- -g2012 表示使用 verilog 2012 标准,如果不定义使用 iverilog 默认 verilog 标准时,编译会报错

- 编译成功后会生成 -o 参数指定的中间文件 wave_ddr3

至于为什么示例命令中不需要指定所有宏,笔者目前还不是很清楚,可能是 iverilog 对默认宏定义的解析和御三家的商用编译器不同。

3 生成 VCD 波形

D:\iverilog\bin\vvp.exe .\wave_ddr3 +model_data+.

+model_data+. 表示向设计传入名为 model_data 的 plusargs 参数,设置为 .

表示将中间文件的生成目录设置为当前目录,不设置的化会默认使用 /tmp 目录,但是 Windows 又没有这个目录,所以会报错。 Linux 环境可以不设置,就使用默认路径 /tmp 好了。

4 使用 GTKWave 在 GUI 界面中查看波形

D:\iverilog\gtkwave\bin\gtkwave.exe .\wave_ddr3.vcd

Trouble shooting

../1024Mb_ddr3_parameters.vh:538: assert: ../iverilog/net_design.cc:700: failed assertion param_type1 iverilog 编译命令中未定义速度等级或者 DDR 位宽

..\ddr3.v:420: syntax error

..\ddr3.v:420: error: malformed statement

..\ddr3.v:421: syntax error

..\ddr3.v:421: error: malformed statement

..\ddr3.v:617: syntax error

..\ddr3.v:617: error: Syntax error defining function.

..\ddr3.v:621: syntax error

..\ddr3.v:621: error: Syntax error defining function.2 iverilog 编译命令中未指定 2012 Verilog 标准

tb.sdramddr3_0.file_io_open: at time 0 WARNING: no +model_data option specified, using /tmp.

tb.sdramddr3_0.open_bank_file: at time 0 ERROR: failed to open /tmp/tb.sdramddr3_0.open_bank_file.0.

..\ddr3.v:637: $finish called at 0 (1ps)3 在 vpp 命令中增加 +model_data+. ,用于设置中间文件的存放路径

4 如果 RTL 或者 Testbench 改动未生效,删除中间文件后重新编译

5 仿真在初始化完成后卡住,需要检查是否给 TZQINIT 赋初值

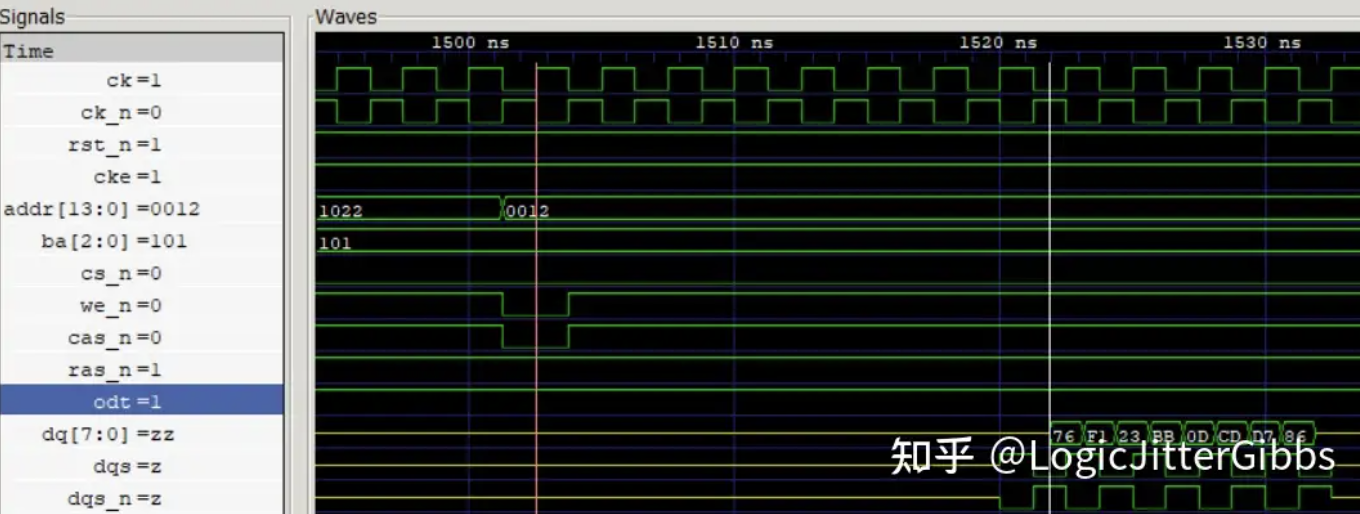

波形

参考资料

全平台轻量开源verilog仿真工具iverilog+GTKWave使用教程

documentation for Icarus Verilog

结语

本期我们讨论 Micron DDR3 模型的文件结构,以及如何在 Windows 平台上,使用小巧的开源工具 iverilog 启动仿真和查看波形。

后续我们会讨论 Micron DDR4 模型的文件构成和如何运行仿真。

作者:LogicJitterGibbs

原文:知乎

相关文章推荐

- DDR 学习时间: DDR 开源实现 高云 GW2A FPGA 的 DDR3 低延迟控制器

- DDR 学习时间 (Part I - OS1):DDR IP 开源实现 DDR5 PHY 数据通路

- IC 工程师视角:恒玄科技 2023 年报

- DDR 学习时间 (Part C - 5):DFI 架构

- DDR 学习时间 (Part B - 6):DRAM ZQ 校正

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。