DDR 学习时间 Part I 将关注 DDR IP 实现,包括开源项目以及商业 IP。

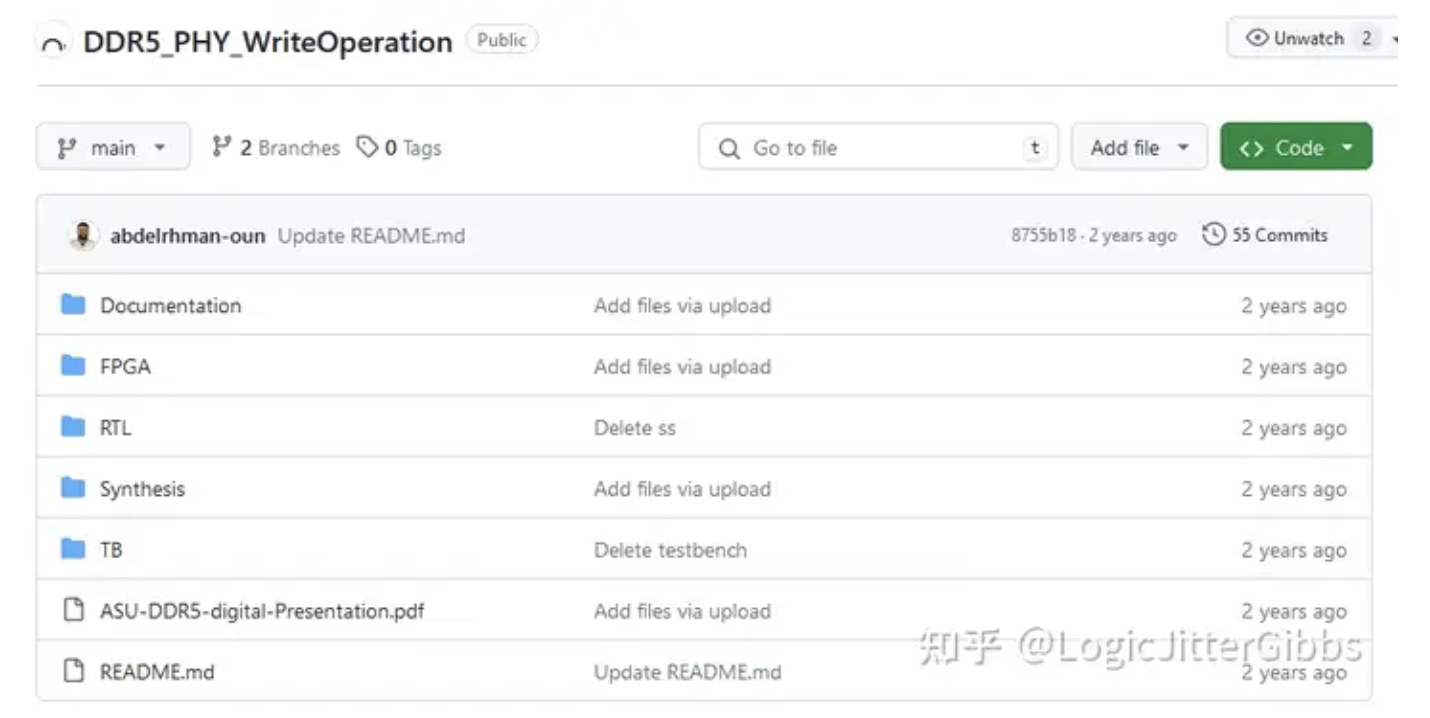

本期写的是一个 Github 上的开源项目,实现的是 DDR5 PHY 的数据通路的数字部分,准确地说是 PHY 的写数据通路,看上去是一份埃及开罗 Ain Shams University (ASU) 学生的作业或者毕业设计,由企业进行了赞助(Si-Vision)。

- 项目地址:https://github.com/abdelrhman-oun/DDR5_PHY_WriteOperation

- 实现: DDR5 PHY 数字数据通路

- 平台: FPGA/ASIC

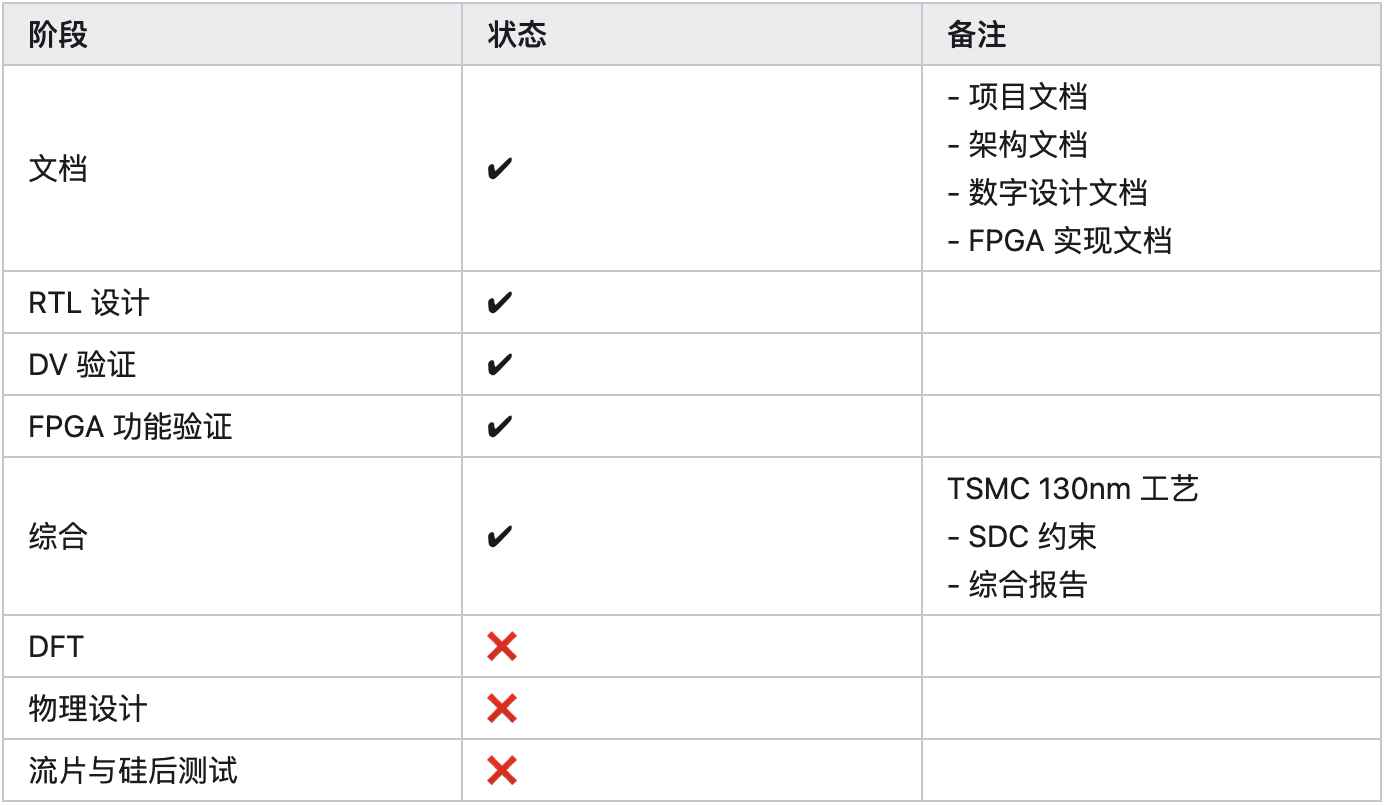

完成度

- 文档 ✔

- RTL 设计✔

- DV 验证✔

- FPGA 功能验证✔

- TSMC 130nm 工艺综合✔

- Formality 验证 ✔

项目介绍

项目设计了 DFI 5.0 接口的 DDR PHY,实现了写操作、CRC 校验和这两者相关 DRAM 命令。

项目使用 System Verilog 开发,进行了 DC 综合以及 Formality 验证,并在 FPGA 上验证了功能。

PHY 功能

PHY 的主要功能是将 MC 的命令和数据传输给 DRAM,以及将 DRAM 的数据传输给 MC。

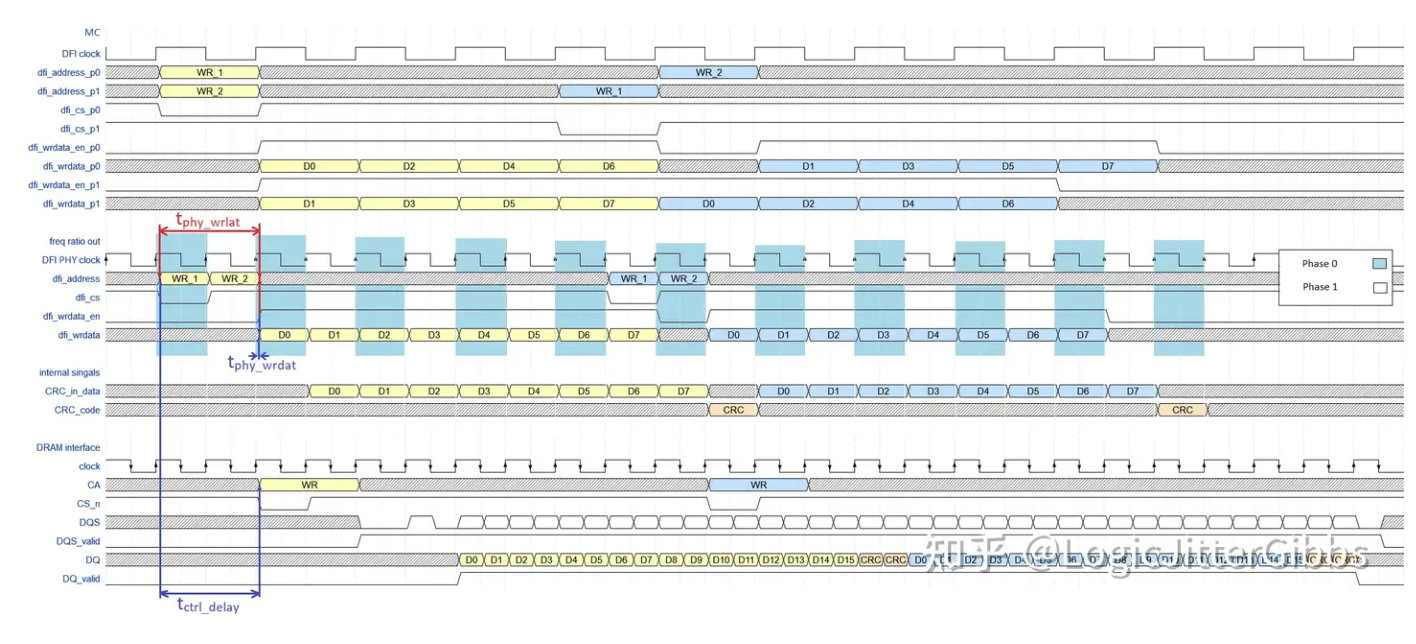

本项目 PHY 实现的功能包括为 MC 写数据生成对应的 DQS 信号、pre-amble,inter-amble 以及 post-amble,另外 PHY 也能够进行 DFI 时钟多倍频率比模式下 MC DFI 数据相位到 PHY 时钟域的转换。

本项目中 PHY 重点实现的功能还包括为 MC 的写数据计算并附上 CRC 校验值。

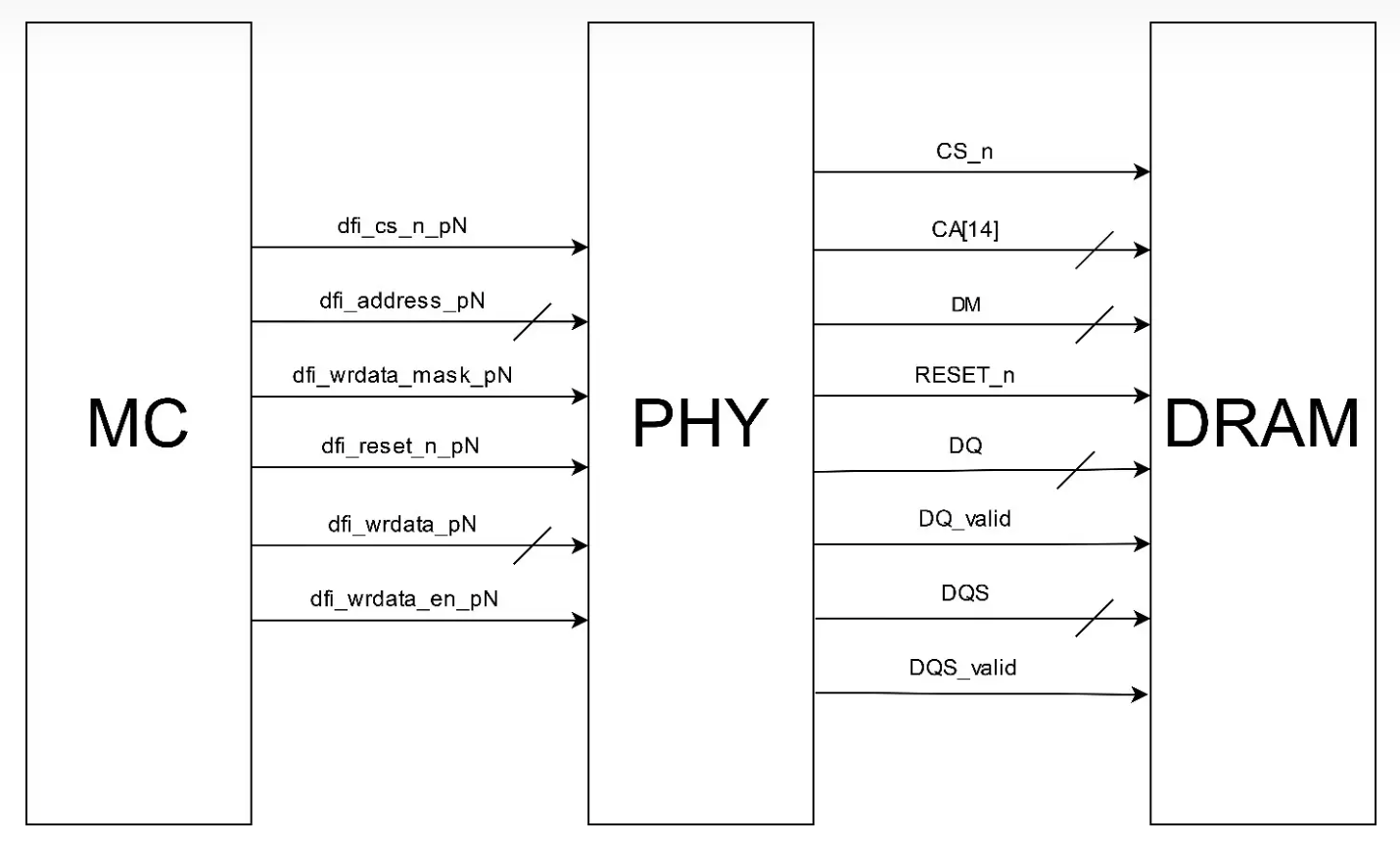

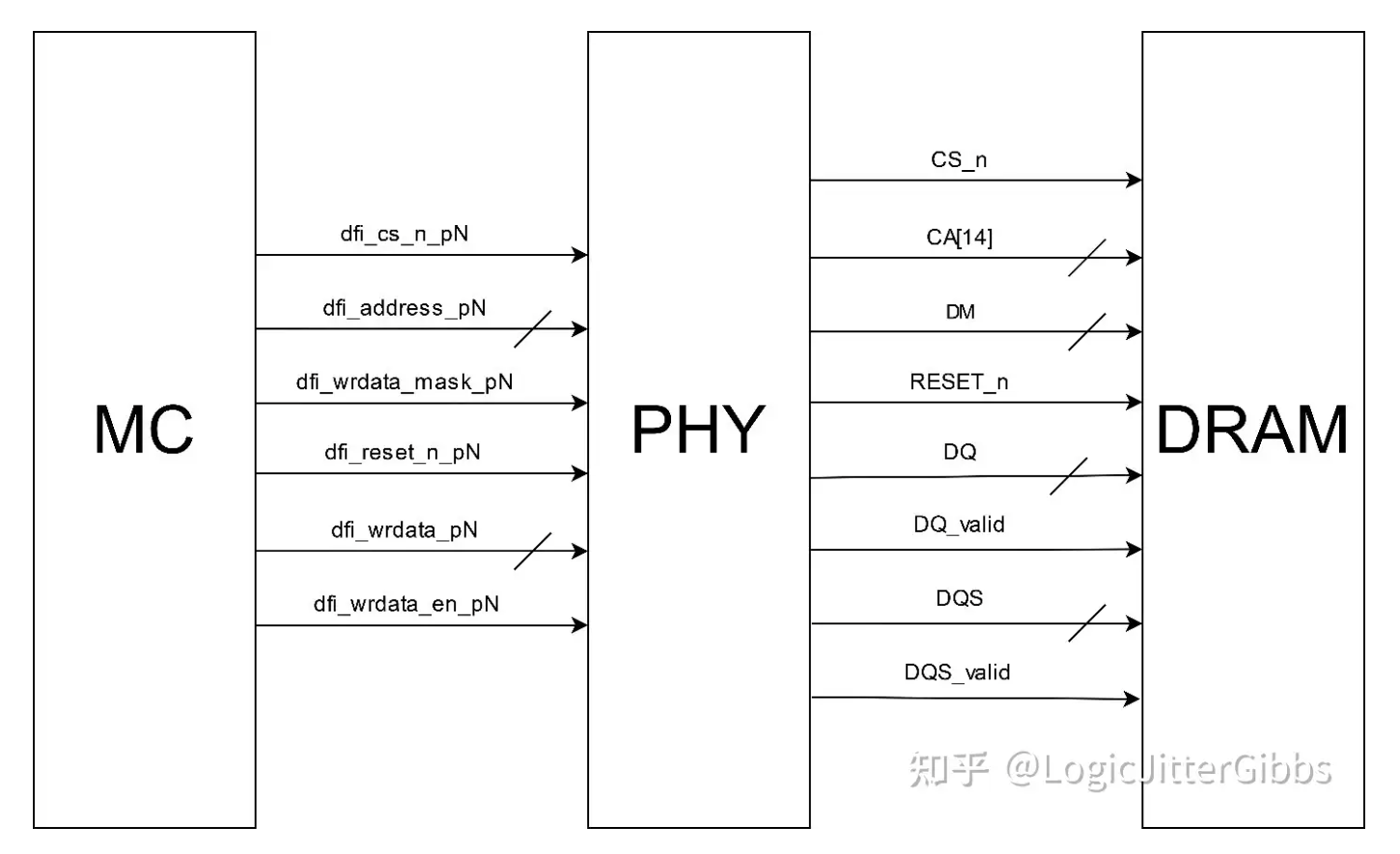

PHY 与 MC 和 DRAM 连接的结构如下图所示:

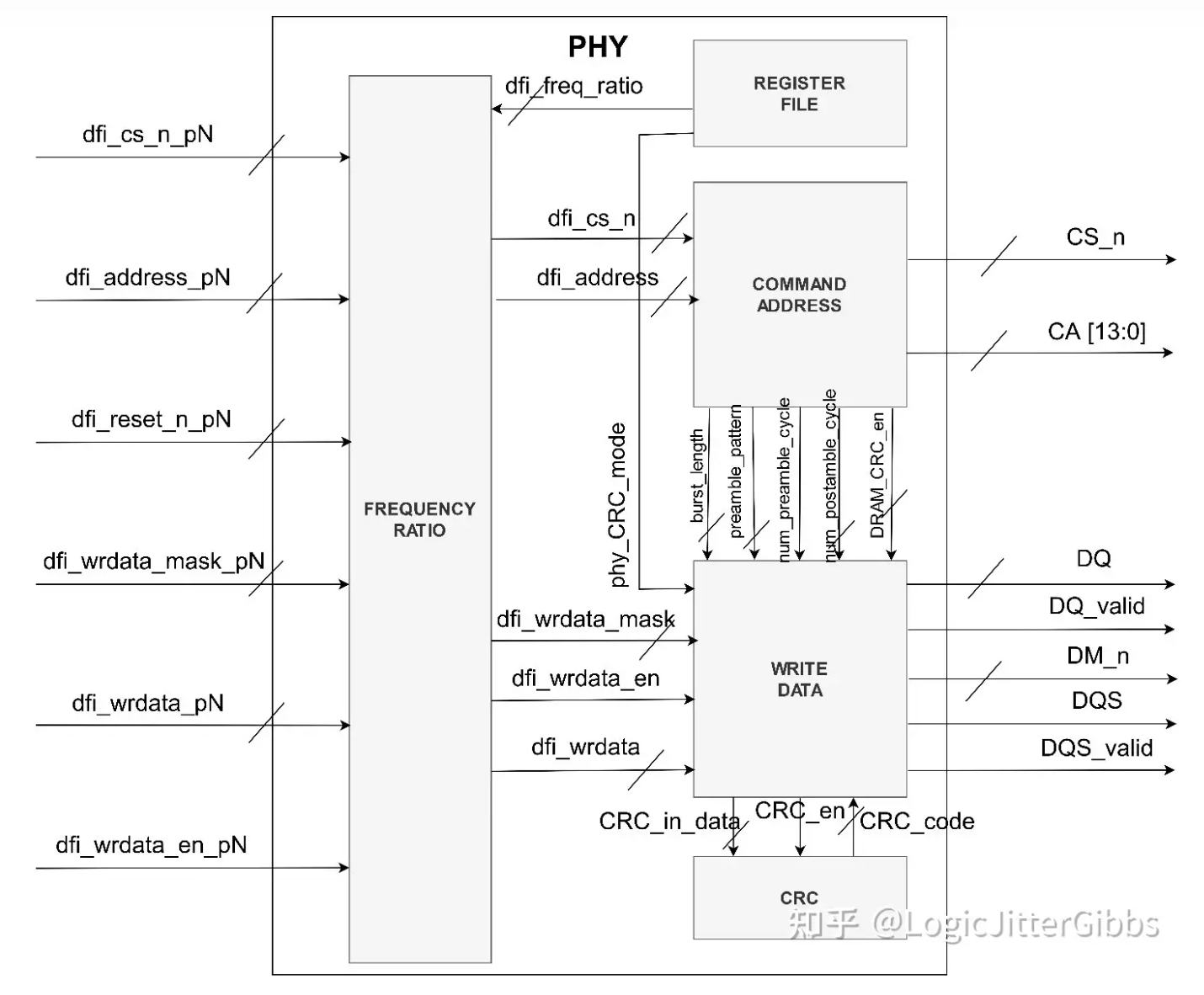

PHY 架构

PHY 通过以下五个模块实现上述的功能:

- FREQUENCY RATIO //DFI 频率比处理

- COMMAND ADDRESS //命令与地址通路

- WRITE DATA // 写数据模块

- CRC //CRC 生成模块

- REGISTER FILE //控制寄存器模块

PHY 结构如下图所示

PHY 主要模块

Frequency ratio 模块

模块根据 dfi_freq_ratio 信号指示的 MC DFI 时钟与 PHY DFI 时钟的频率比,将 MC DFI 多相位信号转换到 PHY DFI 接口。

模块结构如图所示,简单来说是每个 DFI 多相位信号上有个 MUX,在每个 PHY DFI 时钟周期依次轮流选通 MC 各相位信号。

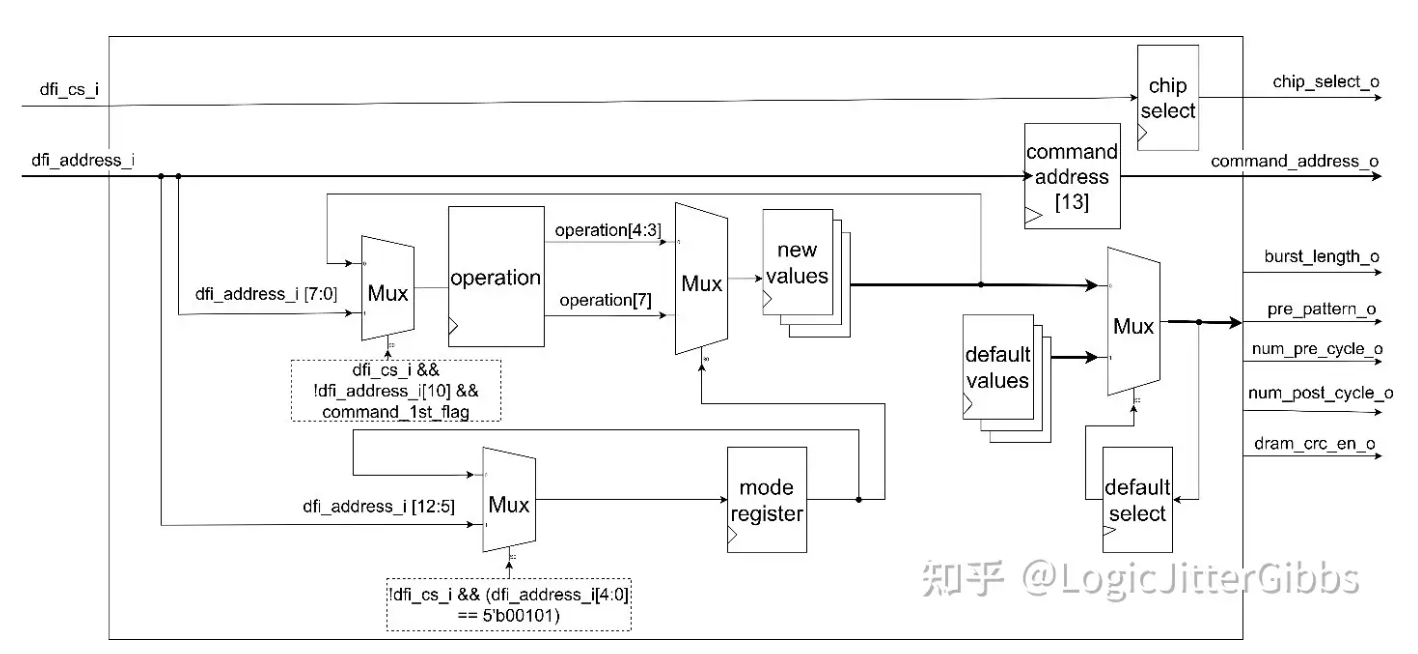

Command Address 模块

CA 模块将 DFI 的 dfi_address 和 dfi_cs 信号转换为 DRAM 上的 CA 和 CS 信号。项目中的 CA 模块支持 MR write 和 DRAM write 命令,CA 模块会自动提取并应用 MR write 命令中 MR 寄存器各个数值。

Write Manager 模块

Write Manager 模块将 DFI 的 dfi_wrdata 信号转换为 DRAM 的 DQ 信号,以及发送 CRC 值。Write Manager 模块本身只是一个 Wrapper,具体功能由三个子模块 Write FSM、Write Shift 和 Write Counter实现。

Write FSM 模块

Write FSM 包括以下状态跳转,实现 Preamble/Interamble/Postamble 与有效的写信号和 CRC 信号。

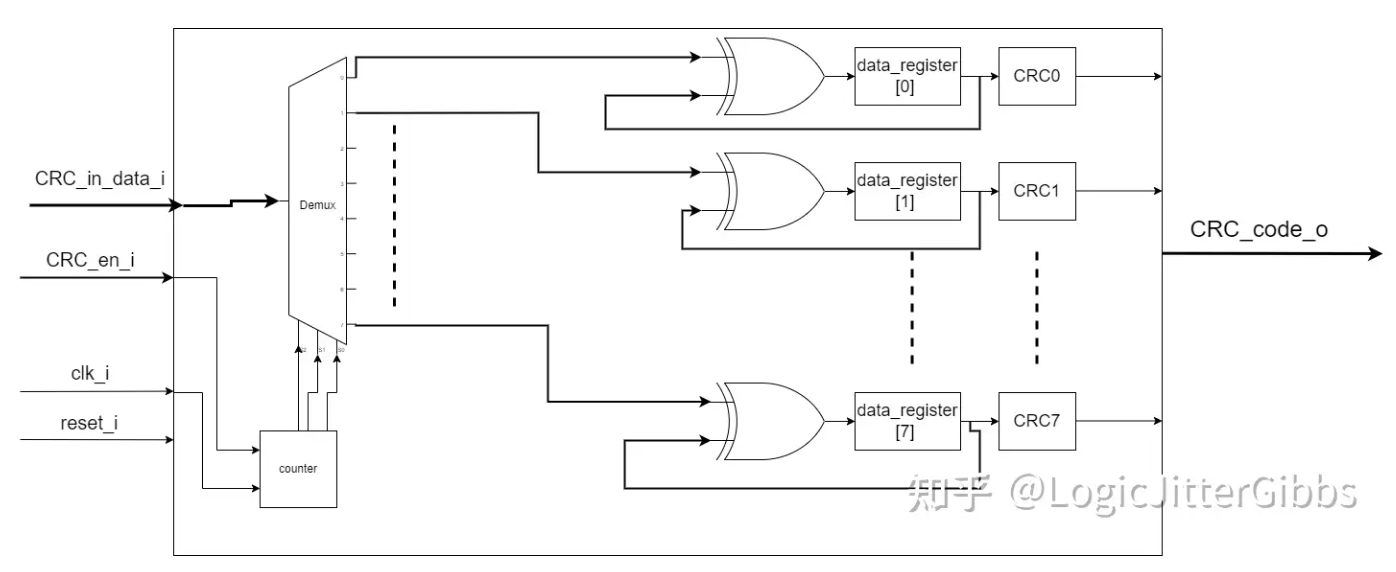

CRC 模块

CRC 模块使用 DDR5 的 ATM-8 多项式 X^8+X^2+X^1+1 生成 CRC,支持 x4/x8/x16 device。

实现的完整写传输时序如下图所示:

项目源文件分析

项目文件十分完善,包括文档、RTL 代码、Testbench、FPGA 实现(报告、代码、Testbench、比特流、XDC)与综合脚本与报告。

文档

首先让笔者印象深刻的是比较完善的文档,可能因为这是份大作业或者毕业设计。所有文档包括整个项目的 Presentation,架构设计文档,设计实现文档,各类时序图以及 FPGA 实现文档。

这个项目的文档可以说十分讲究了,值得所有开源项目、学生作业甚至公司项目学习。

- 项目 Presentation PPT

- PHY 架构设计文档

- 数字设计架构

- PHY 写流程描述报告

- FPGA 实现 PPT

- FPGA 实现报告

- 板级测试截图

RTL 代码

完整的 RTL 代码包括顶层与各子模块。

Testbench

Testbench 覆盖了几种基本场景,其中包括了不同的 Preamble 长度,各类 DRAM 器件,CRC 使能与否等。

项目完成度

结语

这个项目实现功能比较有限,只有 DDR PHY 的数字写数据通路,并不包括 Pad 和 delay lane 等模拟模块。验证方面也是比较简单,通过灌激励然后观察波形验证了基本的功能,没有用到 DRAM 和 DFI model 或者 VIP。但是项目完善的文档和完整的代码与 Testbench 可以给同类项目提供不少有用的参考。

使用了 TSMC 130nm 工艺对项目进行了综合,为类似工艺的实现提供了参考,不过讲道理在这个工艺去做 DDR5 PHY 还是仅仅是学术性的实现,距离产业界较远。

本期我们讨论了:

- PHY 写数据通路实现项目介绍

- 项目源文件分析

后续将继续发掘 DDR IP 相关开源实现,以及整理商业 DDR IP 实现,为计划中的更完善、更具工业界使用价值的 DDR IP 开源项目打基础。

作者:LogicJitterGibbs

原文:知乎

相关文章推荐

- IC 工程师视角:恒玄科技 2023 年报

- DDR 学习时间 (Part C - 5):DFI 架构

- DDR 学习时间 (Part B - 6):DRAM ZQ 校正

- DDR 学习时间 (Part C - 4):DFI 协议功能 - 初始化

- JESD79-4 第4章 SDRAM命令描述与操作(4.30-4.31)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。