本期我们将基于 DDR4 讨论 DRAM 的 ZQ Calibration 的需求以及相应的 ZQCS/ZQCL 命令。

基于 JESD79-4B / 4.12 节

本系列连载于 OpenIC SIG,除了 DDR 学习时间专栏外,OICG 目前正在陆续上线 HDLBits 中文导学的优化版本,欢迎关注/支持/加入我们

DDR 学习时间 - OpenIC SIG 开源数字IC技术分享

导言

DRAM 颗粒需要控制器在初始化以及外部环境条件急剧变化时发送 ZQ Calibration 命令,以校正 DRAM 内部集成的发送与接收阻抗。

最近笔者在工作中就遇到了一个和 ZQ Calibration 相关的问题,客户反应他们在使用协议分析仪对产品和 DRAM 颗粒联调时发现,没有采样到芯片发送 ZQCS 命令。虽然客户产品没有遇到具体的功能或者性能问题,但 DRAM 厂商还是建议他们搞清楚没有采样到 ZQCS 命令的原因,因为他们担心缺少 ZQCS 命令,DRAM 在有些极端情况下工作会不正常。

那么 DRAM 为什么需要 ZQ Calibration?相应的命令有哪些时序和在实现中有什么考虑?本期文章就来讨论 ZQ Calibration 相关的问题。

ZQ Calibration 作用

DRAM ZQ Calibration 校正因为外部环境变化而变化的片上电阻值,Ron 和 ODT,分别是发送驱动逻辑的输出阻抗和接收逻辑的终结电阻值,以保证传输信号的质量。

Ron 和 ODT 数值

以下是笔者对这两个数值的大致理解,因为笔者不太熟悉 DRAM 的内部结构,因此可能说的不完全对,欢迎读者指正。问了 ChatGPT ,说这么理解没问题。

ODT 是 On-Die-Termination 片上终结电阻的缩写,是 DRAM 接收电路中匹配传输线特征的终端电阻。终结电阻的作用是吸收信号线上的反射和干扰。笔者理解 ODT 为 DRAM 的输入阻抗。

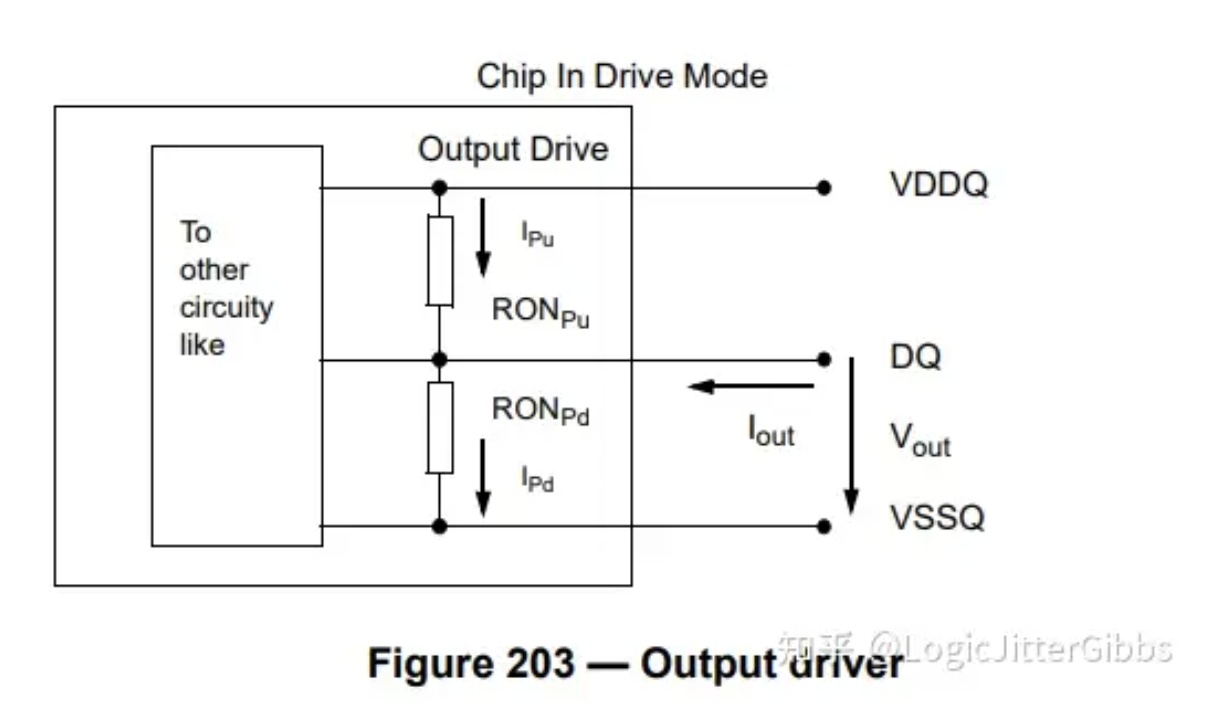

Ron 是 DRAM 输出驱动逻辑的内部电阻,笔者理解相当于 DRAM 的输出阻抗,下图是协议第九章给出的 Ron 功能示意图。

我们知道 DRAM 和控制器之间是一个点到点的传输系统,因此如果 DRAM 的输入输出阻抗与控制器端以及传输线并不互相匹配,那么信号传输的质量会下降。因此,Ron 和 ODT 数值选取的原则之一是与传输系统匹配,系统主要包括对端控制器的输入输出阻抗,以及两者之间的传输线。

设置 Ron 和 ODT

DRAM 的 Ron 和 ODT 集成在 DRAM 内部,并且他们的数值是可通过 MRx 模式寄存器编程的。有几个固定档位可供选择,以 RZQ 的若干份之一为单位。比如 DDR4 的输出阻抗,可以为 RZQ/5 或者 RZQ/7 。

RZQ 是一个 PCB 上阻值固定的分立电阻元件,一般选取 240 欧这个阻值。RZQ 一端连接到 DRAM 的 ZQ pin,另一端接地。RZQ 对电阻是有要求的,首先阻值需要足够高的精度,另外阻值随温度变化的程度尽可能小。

在设计 DRAM 系统时,会根据传输线的情况,计算或者仿真出一组信号完整性最佳的控制器输出输出阻抗与 DRAM 输入输出阻抗。在 DRAM 初始化时,通过 MRx 模式寄存器配置选取的这个最佳值。DRAM 调节内部输入输出阻抗值,将分压后的电压与 RZQ 上电压进行比较,如果二者相等,那么 DRAM 就调节出了一个 RZQ 阻值若干份之一的内部电阻阻值。

笔者对 DRAM 内部调节电阻的电路并不十分清楚,这里根据自己见过的一些内容,简单写了下,具体的电阻调节做法更复杂一些。

举个例子,信号完整性仿真得到最佳的 DRAM 输出阻抗值为 50 欧,RZQ 为 240 欧,因此 DRAM 支持 34 欧(RZQ/7)和 48 欧(RZQ/5)两种配置,选取更接近的 RZQ/5 配置。 DRAM 在一定范围内调节电阻值(调节并联的电阻数量),发现并联 N 个电阻时,输出电阻上的电压的 1/5 分压与 RZQ 上的电压相等,即选择并联 N 个电阻作为输出电阻。

校正 Ron 和 ODT

DRAM 初始化后,我们设置了预期的 DRAM 输入输出阻抗值,系统工作一切正常,但是好景不长。系统的外部环境条件逐渐变化,最主要的是 V 和 T 的变化,分别是 Voltage 电压和 Temperature 温度。比如系统开始工作后,热量逐渐累积,DRAM 结温逐渐上升。或者系统负载加大,电源供应能力不足,电压出现了下降。

因为 Ron 和 ODT 是集成在 DRAM 芯片内的电阻,他们也会随 V 和 T 变化而变化,阻值可能发生较大的变化,此时传输系统的阻抗逐渐进入不匹配区间,信号质量下降,系统就可能出现信号收发错误的问题。

为了防止出现上述这种糟糕的情况,我们需要在 V 和 T 发生急剧变化之后,重新校正 Ron 和 ODT 的阻值。ZQ Calibration 需要一个几乎不随 V 和 T 变化的电阻作为参考来调节变化的电阻,那么哪里去找一个几乎不变的阻值呢?

这个电阻就是前文提到的 RZQ——PCB 上的分立高精度电阻。因为 RZQ 在 DRAM 芯片外部,所以 RZQ 阻值几乎不会被 DRAM 芯片上的温度和电压变化所影响。虽然,整个系统的温度,包括芯片和 PCB 的温度都会上升,但是 PCB 上的温度一般比芯片内部温度低得多,并且通过选取特定的,阻值对温度不敏感的电阻能够尽量克服系统的温度变化。

在新的温度和电压下,重复 DRAM 初始化时的电阻 Calibration 流程,DRAM 就可以把阻值调节回预期的数值。

接着上文举的例子,DRAM 此时发现并联 N 个电阻时,电压值已偏离 RZQ 上的电压值,重新调节发现选取 M 个电阻并联时,输出电阻上的电压的 1/5 分压与 RZQ 上的电压相等,即重新选择并联 M 个电阻作为输出电阻,完成 ZQ Calibration。

ZQ Calibration 命令

DRAM 共有 2 种 ZQ Calibration ,ZQCS 和 ZQCL,名字中的最后一个字母,顾名思义表示前者时间较短,而后者校正的时间更长。

在 ZQCS/ZQCL 命令发送前,DRAM 所有 Bank 需要处于 precharge 状态(并满足 tRP 参数,即 PRE 命令后已满足所需延时),并且在 ZQCS/ZQCL 期间不能发送任何命令或者数据,以使 DRAM IO 应用新的输入输出阻抗。

ZQCL 命令

ZQCL 用于上电初始化时的 ZQ 校正,在上电之后 DRAM 需要从整个 Calibration 窗口中找到 MRx 中设置的 ODT 与 Ron 值,所需的时间会比较长。

当然,在 DRAM 初始化之后,控制器也可以根据需要发出 ZQCL 命令,只不过除了退出自刷新等少数场景,不会这么做,因为长时间的 ZQ Calibration 会停止 DRAM 读写命令,影响性能甚至导致 SoC 上的缓冲区被填满。

时序参数

ZQCL 相关的时序参数是

- tZQinit

- tZQoper

如图 2 所示,在 Reset 之后的第一个 ZQCL 命令发送之后,需要等待 tZQinit ,即ZQ 校正完成后,控制器才可以发送后续的其他命令。DDR4 所有速率下,tZQinit 均为 1024 个 CK 周期。

第一个 ZQCL 之后的 ZQCL 命令,还需要注意和 Reset 要保持 tZQoper 的间隔,所有速率下均为 512 个 CK 周期。

ZQCS 命令

ZQCS 用于正常工作时的周期性 ZQ 校正,以应对环境温度和电压的变化。因为此时 DRAM 只需要检查现有阻值是否满足需求,或者在临近的 Calibration 窗口寻找满足需求的新阻值,所以需要的 Calibration 时间相对 ZQCL 较短。

时序参数

如图 2 所示,在 ZQCS 命令发送之后,需要等待 tZQCS ,即 ZQ 校正完成后,控制器才可以发送后续的其他命令。

DDR4 所有速率下,tZQCS 均为 128 个 CK 周期,所以较短的 ZQCS 命令只需要 ZQCL 1/8 的时间完成。

合适的发送 ZQCS 的频率

DRAM 协议规定,ZQCS 可以在 128 个 CK 周期内,校正最大 0.5% 的 Ron 和 RTT (ODT 电阻) 阻值偏移,因此 ZQCS 命令之间的间隔设置取决于系统具体的 VT 变化情况,即可接受的最大电压变化率 Vdriftrate 与温度变化率 Tdriverate。已知这两者参数的情况下,可以根据协议给出的这个公式计算最大 ZQCS 间隔。

其中,分母上的 ZQCorrection 是一个定值,DDR4 为 0.5。TSens 和 VSens 则可以从具体的 DRAM 的数据手册获得(这点有待笔者去确认下)。

控制器实现

DRAM 控制器一般会把 ZQCS 间隔以配置寄存器的形式开放给用户。用户可以根据需求设置 ZQCS 间隔,一般来说太大的间隔会导致系统在 VT 变化时失效的风险,而太小的间隔会导致系统的性能下降,因为 ZQCS 期间不能发送其他 DRAM 命令及其数据。

还记得开头那个用户反馈的问题吗?笔者分析了控制器代码和配置后认为,客户没有观察到芯片发送 ZQCS 的原因可能是他们的采样窗口比较小,小于 ZQCS 命令发送的间隔。

结语

本期我们讨论了:

- DRAM 为什么需要 ZQ 校正

- DRAM ZQ 校正命令的时序以及相关分析

作者:LogicJitterGibbs

原文:知乎

相关文章推荐

- DDR 学习时间 (Part C - 4):DFI 协议功能 - 初始化

- JESD79-4 第4章 SDRAM命令描述与操作(4.30-4.31)

- JESD79-4 第4章 SDRAM命令描述与操作(4.28-4.29)

- JESD79-4 第4章 SDRAM命令描述与操作(4.26-4.27)

- JESD79-4 第4章 SDRAM命令描述与操作(4.25)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。