本节基于 DFI 协议 2.0 节(协议 4.0 版本)讨论 DFI 的基本架构。

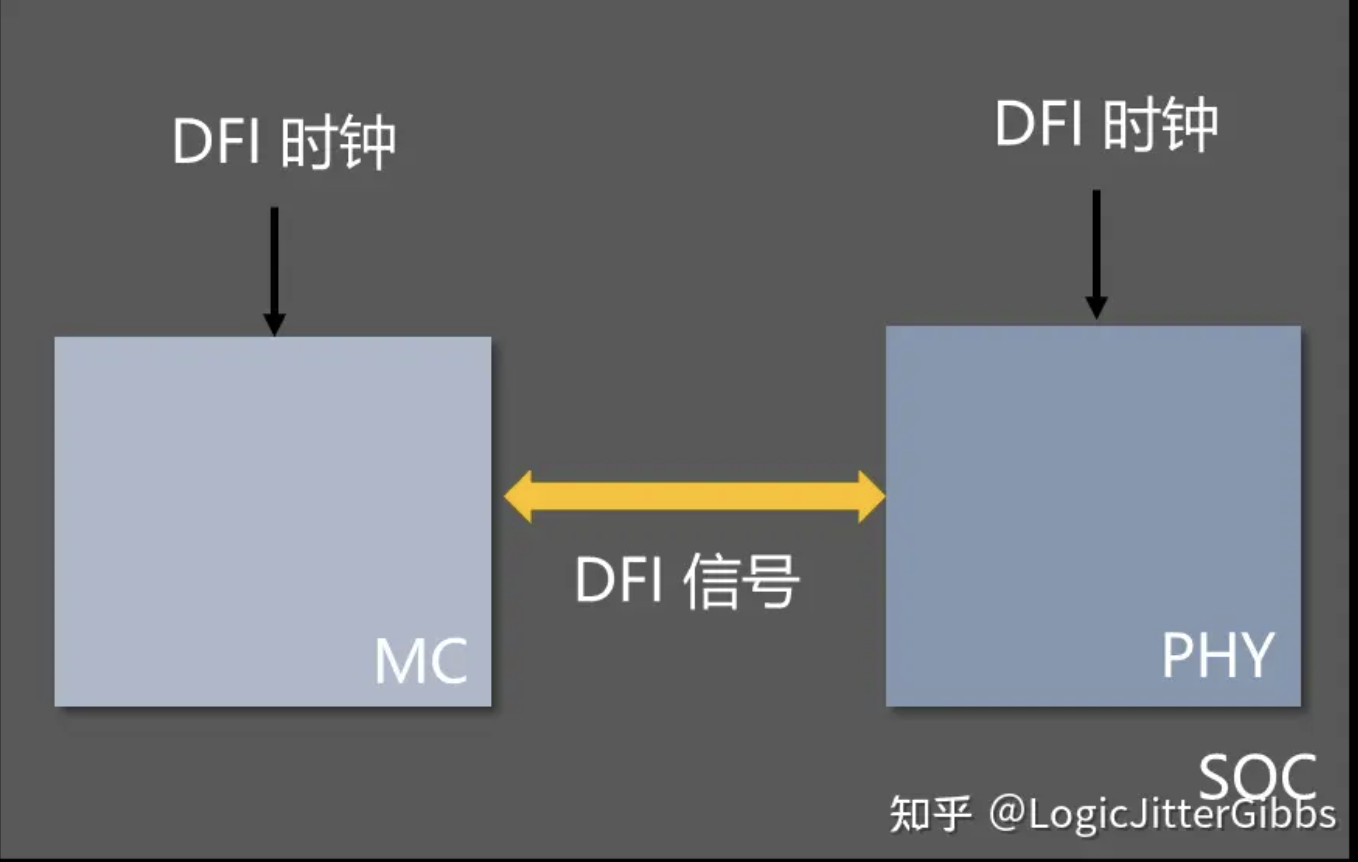

DFI 协议定义的是 Memory controller (以下简称 MC)和 PHY 之间的接口的信号、时序以及交互行为。

DFI 协议中另外两个基本要素分别是 DFI 时钟(DFI Clock)以及 DFI 定义信号(DFI-defined signal ),下图是关于 DFI 基本要素的示意图。

DFI 时钟

DFI 定义 DFI 信号都在 DFI 时钟上升沿发送。虽然, DFI 协议没有定义如何接收 DFI 信号,但是接收端一般还是同步地也在 DFI 时钟上升沿接收采样。

DFI 协议没有定义 DFI 时钟来源(Clock source),那么 DFI 时钟有来自 SoC 或者 PHY 两种方案:

- SoC 时钟源,比如来自 SoC GCC(Global Clock Control) 或者 DDRCC 中的 PLL。

- PHY 时钟源,来自 PHY 中 PLL

一般实现中大多采取 SoC 时钟源,此时 DFI 时钟对于 MC 和 PHY 来说都是输入时钟,设计者根据两者时序的余量,在 SoC 或者 DDRSS (DDR SubSystem)中平衡 DFI 时钟到 MC 和 PHY 的时延,下图是这种时钟结构的示例。

至于采用 PHY PLL 时钟源作为 DFI 时钟的方案,笔者没有在实际应用中见到过,参照 PCIe PHY 中的 PHY PCLK output 方案,这样应该也是可行的。此时,PHY 中的 PLL 倍频低速参考时钟(Reference clock)为高频 DFI 时钟,参考时钟一般选取 SoC 的低速参考时钟。

这个方案下,DFI 时钟的时延平衡会是一个问题,因为 PHY 内部的 DFI 时钟的时序路径会比较短,而 MC 和 PHY 之间的时序路径会很长,这种路径长度的不平衡会对后端工具时钟树生成产生影响,可能工具自动长出的时钟树不是最好,下图是这种时钟结构在 1:1 DFI 时钟频率比时的示例。

值得注意的是,这里的 DFI 时钟指的是 DFI 接口上的时钟,PHY 内部还存在 PHY DFI 时钟。一些情况下,PHY DFI 时钟频率可能是 DFI 时钟的倍数。更多相关解析可以参见 DFI 时钟频率比一节的文章。DDR 学习时间 (Part C - 3):DFI 协议功能 - DFI PHY 与 DFI 时钟频率比

DFI 信号

DFI 协议信号本质上是 DRAM 总线信号加上一些额外的用于初始化、更新、训练等功能的信号。

DFI 信号具体有哪些信号,与 DFI 系统频率比和 Memory 类型等相关。因为 DFI 信号茫茫多,所以本文不会一一列出,详情请参看协议 3.0 节,本文仅只列出了 DFI 信号组。

DFI 信号组

DFI 信号互操作性

DFI 协议定义 MC 和 PHY 之间需要保证 DFI 信号的互操作性,有以下几个方面:

- 信号位宽 //Signal widths

- 交互时序 //Interconnect timing

- 时序参数 //Timing parameters

- 频率比 // Frequency ratio

- 功能 // Function

信号位宽自不必说,MC 和 PHY 有效信号的位宽必须相等,对于一些位宽不匹配的信号,需要确保对功能不会有影响。

交互时序指的 MC 和 PHY 之间发送信号的时序,和接收信号时的 setup 和 hold 时序需求。

第一节说到 DFI 协议定义了信号在时钟上升沿发送,没有定义如何接收 DFI 信号,那么 MC 和 PHY 双方就需要在如何接收信号上达成一致。一般来说,双方就约定为同步地也在 DFI 时钟上升沿接收采样,这样一来信号接收时的 setup 和 hold 时序由在 DFI 时钟上升沿上的静态时序分析保证。

时序参数指的是 DFI 命令执行时,特定的 DFI 信号变化之间的延迟时间需求。这些延迟需求可能是固定常值,也可以是最小或者最大值。DFI 时序参数在 DFI 命令执行期间不能变化,只能在系统 DFI 频率发生变化或者总线空闲时改变。

频率比指的是 DFI 时钟和 PHY DFI 时钟的比值,MC 和 PHY 接口部分工作在 DFI 时钟域,而 PHY 内部逻辑工作在 PHY DFI 时钟域。MC 和 PHY 的 DFI 频率比设置必须一致。在频率一致的系统中,MC 和 PHY 工作在完全相同的时钟频率,而在多倍频率比系统中,MC DFI 时钟频率和 PHY DFI 时钟频率的比值可以为 1:2 或者 1:4。

DFI功能基于特定的 Memory 类型(Class)和拓扑结构,会有不同的 DFI 功能以及 DFI 信号。Memory 类型指的就是 LPDDRx 或者 DDRx,拓扑结构指的 DDRx 的 DIMM,RDIMM(Registered DIMM) 或者 LRDIMM(Load Reduced DIMM)。

在 MC 和 PHY 就以上 DFI 互操作性达成一致后,DFI 信号可以正常交互。MC 和 PHY IP 大部分的 DFI 互操作性通过 RTL 中的参数或者配置寄存器来设置,而一小部分则是在选型之后就不能更改。

所以,确定和配置 MC 和 PHY 之间的 DFI 互操作性是 DDRSS 或者 SoC 集成工程师的主要工作,包括:

- MC 和 PHY DFI 信号位宽一致,如果有不一致的地方,确保通过合适的处理(浮空或者固定为电平 0 或者 1)不会影响 DFI 功能。

- MC 和 PHY 在 DFI 时钟边沿发送和采样 DFI 信号,通过静态时序检查 DFI 信号接收时的 setup/hold 时序。

- MC 和 PHY 的时序参数的取值范围没有冲突,选取双方共同支持的时序参数,在集成阶段配置 Verilog 参数,或者初始化前配置寄存器。

- MC 和 PHY 均支持选取的 DFI 时钟频率比,选定初始化频率比,并验证双方能动态切换到新的频率比。

- MC 和 PHY 均支持所需要的 DFI 功能。

DFI 功能

DFI 协议的功能(Feature)分为两类,全局功能与特定 Memory 类型功能,前者是应用于所有 Memory 类型的 DFI 功能,后者只应用于特定 Memory 类型。

但注意这里提到的功能并不是对所有 DFI 系统都是必须的,打个比方,对于整体不支持低功耗的系统来说,DFI 的低功耗功能也就不需要支持。

全局功能

- 改变 DFI 频率比

- 改变 DFI 频率

- 低功耗控制

- 错误报告

- 更新接口

- PHY master 接口

- 时钟停止功能

- 数据比特停用功能

- DFI 连接断开

- 支持独立通道

特定 Memory 类型功能

DFI 支持多种 Memory 类型(Class,即 DDRx/LPDDRx)与拓扑结构,DFI 功能支持与否本质上这来自于 DDRx/LPDDRx 本身支持或者不支持某项特性。比如,DDRx 从 DDR4 开始支持 DBI 特性,而 DDR3 则不支持,DFI 基本沿用了 DDR4/DDR3 支持或者不支持这些功能的规则。

关于特定 Memory 类型的功能,可参见协议 2.2 的表 2。

结语

本期我们讨论了:

- DFI 架构

- DFI 时钟

- DFI 信号

- DFI 功能

作者:LogicJitterGibbs

原文:知乎

相关文章推荐

- DDR 学习时间 (Part B - 6):DRAM ZQ 校正

- DDR 学习时间 (Part C - 4):DFI 协议功能 - 初始化

- JESD79-4 第4章 SDRAM命令描述与操作(4.30-4.31)

- JESD79-4 第4章 SDRAM命令描述与操作(4.28-4.29)

- JESD79-4 第4章 SDRAM命令描述与操作(4.26-4.27)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。