DDR 学习时间 Part I 将关注 DDR IP 实现,包括开源项目以及商业 IP。

本期写的是一个 Github 上的开源项目,基于 Tang Primer 20K 开发板和高云 GW2A FPGA 的 DDR3 控制器 IP。

- 项目地址:https://github.com/nand2mario/ddr3-tang-primer-20k?tab=readme-ov-file

- 实现: 基于高云 GW2A FPGA 的 DDR3 控制器

- 平台: FPGA (高云 GW2A)

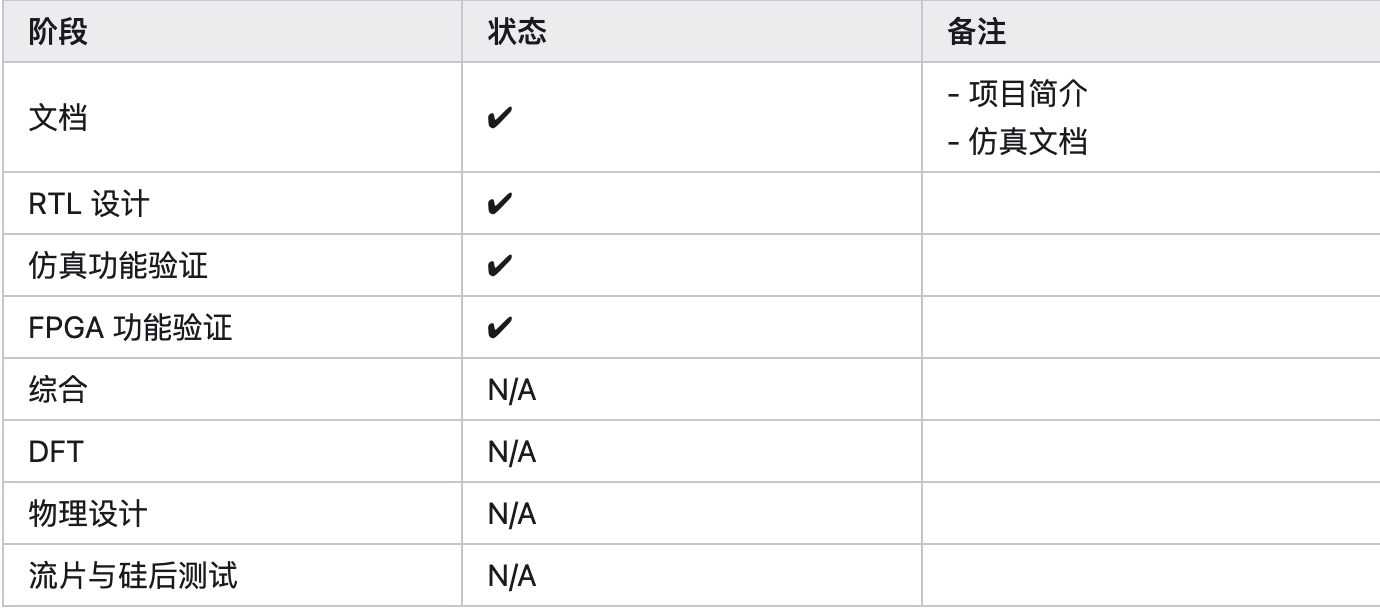

完成度

- 文档 ✔

- RTL 设计✔

- 仿真功能验证✔

- FPGA 功能验证✔

项目介绍

这个项目是基于高云 FPGA 开发板 Tang Primer 20K 的 DDR3 控制器,使用了高云 OSER_MEM/DQS 等原语,因为实现比较高频的 DDR 速率(DDR3-800)需要借助芯片本身的高速 Pad 原语,所以本身只能用于高云的 FPGA,当然理论上在改动 PAD 相关的原语后也可以移植到别的 FPGA 上。

特点

据笔者了解,芯片厂家高云本身是提供了一个包含控制器和 PHY 的完整 DDR3 Memory Interface IP 的,也提供了只包括 PHY,由用户自行实现控制器的 DDR3 PHY Interface IP。如果开发者想实现特殊需求,可以基于 PHY IP 开发控制器逻辑。具体用法可以参考高云提供的文档和参考设计:

但是,这个项目中开发者连高云的 PHY IP 都没有使用,相当于开发了独立的 MC+PHY IP,只用到和 PAD/DLL 等高云 FPGA 原语。

但是,这个项目中开发者连高云的 PHY IP 都没有使用,相当于开发了独立的 MC+PHY IP,只用到和 PAD/DLL 等高云 FPGA 原语。

开发者的目标是低延迟的 DDR 控制器,以用于一些低延迟的场景,开发者举例道比如 FPGA Gaming(笔者:FPGA 怎么还有 gaming 一说)。控制器实现的最低读延迟是 90ns。

实现

项目的基础代码看起来基于 Tang 的相关例程,如串口打印模块等。

时钟与接口

控制器分别有三个时钟输入,包括一个低速的 100MHz 主时钟,高速的 DRAM ck 时钟,以及一个经过 90 度相移的高速时钟。高速时钟在 DDR3-800 时,频率为 400MHz。主时钟供逻辑使用,高速时钟只提供给 PAD 使用。

控制器 DRAM 侧的接口是基于开发板上的 16bit DRAM,注意这里实现中不支持突发操作,只支持 Signle 操作。

控制器用户逻辑这一侧实现的是一个简单的自定义接口,包括读写命令与地址输入,写数据输入和读数据输出。此外,还包括 writing leveling 和 read calibration 的完成状态和训练结果输出。

此外提供了 refresh 输入控制信号,可以由用户逻辑定时周期性触发控制器对 DRAM 的 refresh 操作。

特性

支持 ZQ calibration 和 dynamic ODT,用于优化 DRAM 信号完整性。

支持 writing leveling 和 read calibration 训练,用于找出最佳的写操作和读操作时的 DQSO 和 DQSI 时延。

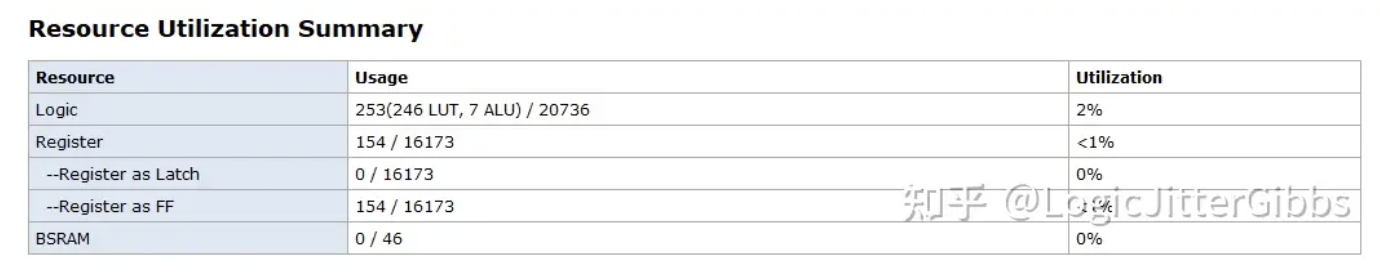

资源

- 1377 logic elements (6% on GW2A-18C)

- 1 PLL

- 1 DLL

- 55 IO

其中控制器本身消耗的资源如下

仿真

项目使用 iverilog 和 gtkwave 的工具组合进行仿真,并提供了一个简单的仿真说明文档。

因为高云 FPGA 的 IDE 目前没有集成仿真功能,所以提取原语的行为级模型,和 RTL 以及 DDR3 行为级模型一起通过 iverilog 进行仿真,项目开发者提供的步骤如下(Windows 平台):

- Icarus Verilog 11. This particular version works for me. The latest version has some issues (assertion errors) with the Micron DDR3 model.

- Micron DDR3 memory model. Get it from Micron's website ("DDR3 SDRAM Verilog Model, version 1.74"). Extract the source files to this dir.

- Gowin's

prim_sim.v. It comes with Gowin IDE: for exampleGowin_V1.9.8.07/IDE/simlib/gw2a/prim_sim.v. - GNU make:

choco install make

运行命令

make run.controller

项目源文件分析

文档

项目提供了项目简介文档和仿真运行文档,但是缺少功能描述文档和设计描述文档。

RTL 代码

控制器代码在 ddr3_controller.v 中,ddr3_top.v 例化了 ddr3_controller 与 PLL,另外实现了一些用于测试的用户逻辑。

代码风格还不错,有提供不少注释,但所有控制器的逻辑都写在一个文件中,比较杂乱。

ddr3_controller.v 中的主体代码是 DDR3 控制状态机,控制状态跳转实现 DDR 初始化和读写时序,和在不同状态下控制 DDR Pad 的输入输出使能信号。

另外,ddr3_controller.v 例化了一些原语用于实现 DDR 的 PAD 功能,包括

- OSER8 原语用于实现输出 pad

- DQS 原语用于实现双向,延迟可调的 DQS pad

- OSER8_MEM 和 IDES8_MEM 原语用于实现双向 DQ 和 DM pad,这个原语带有跨时钟域 FIFO

使用 DLL 原语来实现 DQS 的 90/270 度时延,产生相位延迟的 DQS,用于接收和发送 DQ。

Testbench 与仿真

如上文所述,项目了提供了一个与 Micron DDR model 一起仿真的 testbench。

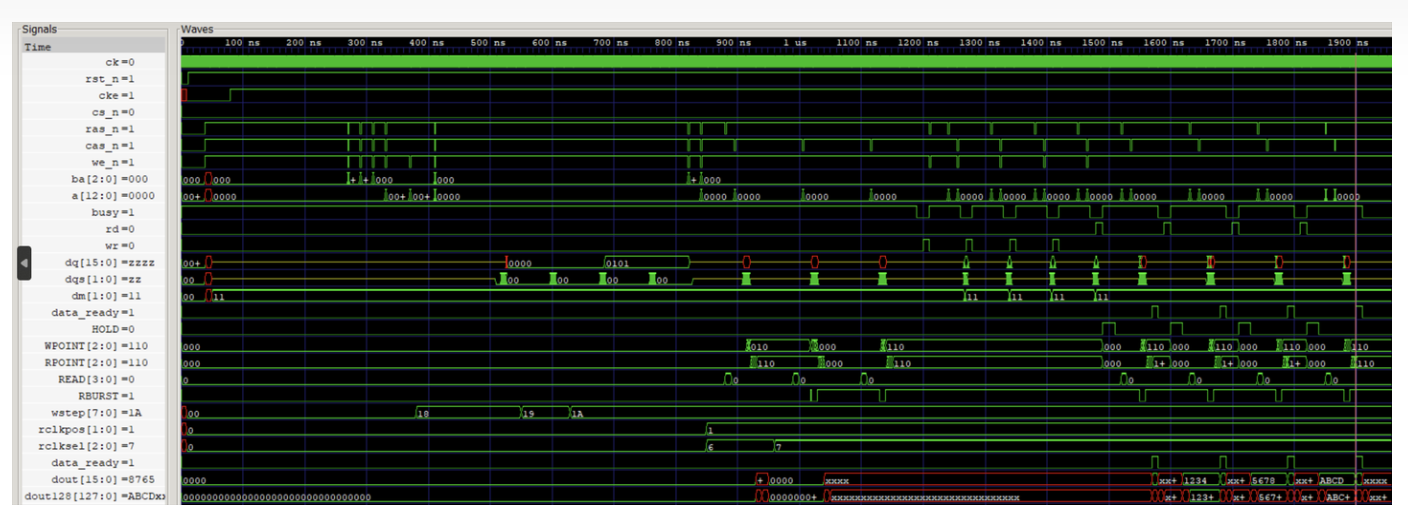

项目中附上的完整流程仿真图如下

FPGA 实现

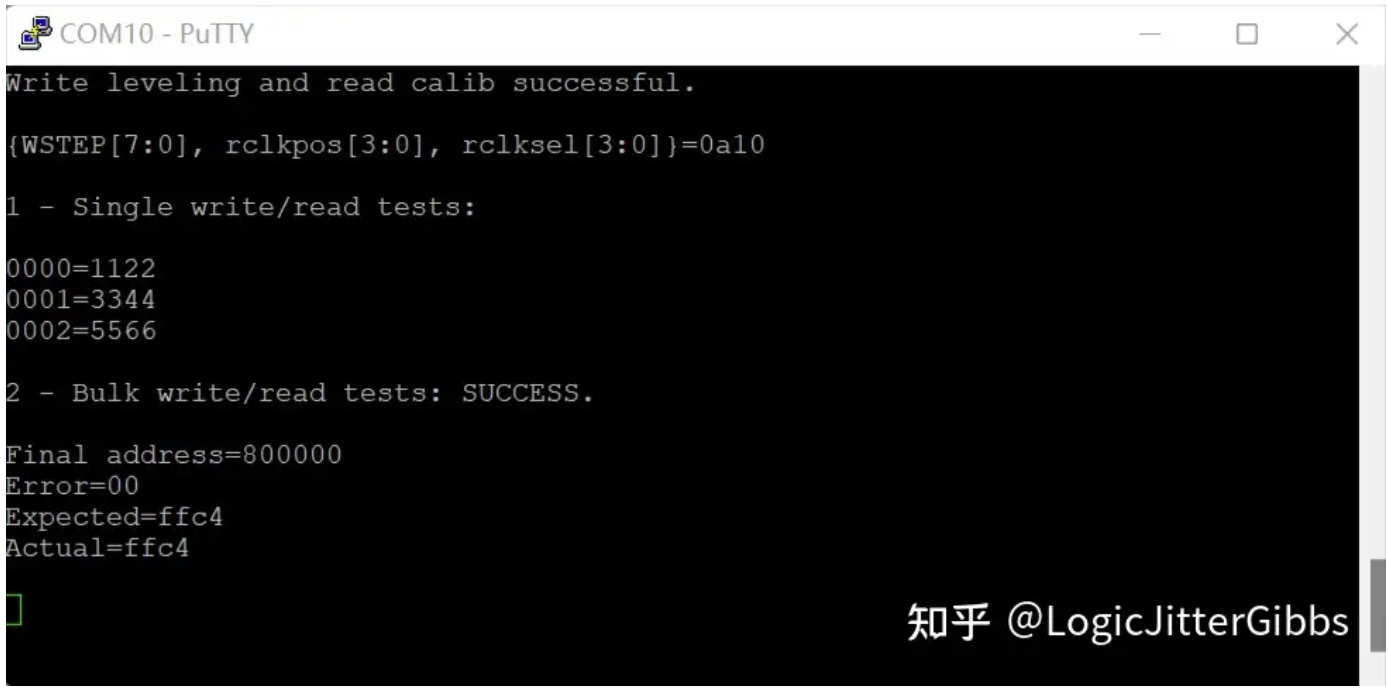

开发者实际上板测试时,通过串口打印的信息判断读写成功,

项目完成度

结语

这个 DDR 控制器项目只用到 PAD/DLL 相关的高云 FPGA 原语,实现了一个独立的 MC+PHY IP,不依赖于高云 FPGA 自身的 DDR MC 或者 PHY IP。控制器的特点是可以实现 DDR3-800 下低至 90 ns 的读延迟,相当于 400MHz 控制器时钟的 36 个周期。另外从资源使用情况来看,小于官方提供的 MC+PHY Memory Interface IP。

控制器在正常读写操作以外,还支持 ZQ calibration, writing leveling, read calibration and dynamic ODT 等功能。但是,控制器只支持 Single 不支持 Burst 操作,这让实用性方面打了不少折扣。尽管如此,这个项目还是给高云 FPGA 和 Tang 开发板的 DDR 开发提供一些参考。

本期我们讨论了一个基于高云 FPGA 和 Tang 开发板的 DDR3 MC+PHY 控制器方案:

- 项目介绍

- 项目源文件分析

后续将继续发掘 DDR IP 相关开源实现,以及整理商业 DDR IP 实现,为计划中的更完善、更具工业界使用价值的 DDR IP 开源项目打基础。

作者:LogicJitterGibbs

原文:知乎

相关文章推荐

- DDR 学习时间 (Part I - OS1):DDR IP 开源实现 DDR5 PHY 数据通路

- IC 工程师视角:恒玄科技 2023 年报

- DDR 学习时间 (Part C - 5):DFI 架构

- DDR 学习时间 (Part B - 6):DRAM ZQ 校正

- DDR 学习时间 (Part C - 4):DFI 协议功能 - 初始化

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。