Inheritance

SystemVerilog的OOP实现提供了从基类(base class)继承,并在子类(subclass)中对基类功能进行扩展(extending )的功能。 这个概念称为继承(inheritance)。

当从一个类继承到另一个类时,原始的类定义不会更改,但是新的子类包含基类的所有属性(properties)和方法(methods),然后可以添加其他属性和方法。

Overridden Members

我们可以给从基类扩展的子类的方法提供新的定义。

program class_inherit;

class A ;

integer j = 5;

task print();

begin

$display("j is %0d",j);

end

endtask

endclass

class B extends A;

integer i = 1;

// Override the parent class print

task print();

begin

$display("i is %0d",i);

$display("j is %0d",j);

end

endtask

endclass

initial begin

B b1;

b1 = new;

b1.print();

end

endprogram输出

i is 1

j is 5

super

super关键字用于在派生类( derived class)中引用父类(parent class)的属性。

program class_super;

class A ;

integer j;

function new();

begin

j = 10;

end

endfunction

task print();

begin

$display("j is %0d",j);

end

endtask

endclass

class B extends A;

integer i = 1;

function new();

begin

// call the parent new

super.new(); // constructor chaining

$display("Done calling the parent new");

i = 100;

end

endfunction

// Override the parent class print

task print();

begin

$display("i is %0d",i);

$display("Call the parent print");

super.print();

end

endtask

endclass

initial begin

B b1;

b1 = new;

b1.print();

end

endprogram

输出

Done calling the parent new

i is 100

Call the parent print

j is 10

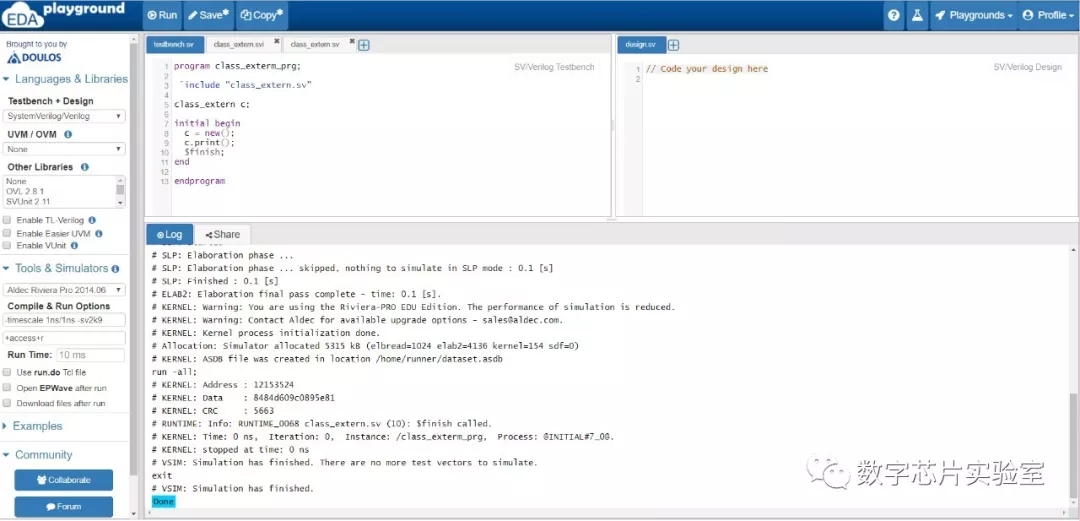

Out-of-block declarations

就像在C ++中一样,Class原型也可以在头文件中声明。并且可以在seprate文件中对 functions/tasks的主体进行描述。

这时候需要在头文件中添加extern关键字,如下例所示。

Header File

`ifndef CLASS_EXTERN_SVI

`define CLASS_EXTERN_SVI

class class_extern;

int address;

bit [63:0] data;

shortint crc;

extern function new();

extern task print();

endclass

`endif

Body File

`ifndef CLASS_EXTERN_SV

`define CLASS_EXTERN_SV

`include "class_extern.svi"

function class_extern::new();

this.address = $random;

this.data = {$random,$random};

this.crc = $random;

endfunction

task class_extern::print();

$display("Address : %x",address);

$display("Data : %x",data);

$display("CRC : %x",crc);

endtask

`endif

Program File

program class_exterm_prg;

`include "class_extern.sv"

class_extern c;

initial begin

c = new();

c.print();

$finish;

end

endprogram输出

Address : 12153524

Data : c0895e818484d609

CRC : 5663

SystemVerilog系列所有文章都可以在下面这个网站上在线仿真哦。

本文转载自公众号:芯片数字实验室

原文链接:

https://mp.weixin.qq.com/s/ngRoCSOS8km\_EJMcX-HuPg

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏