使用Constraint-driven(约束驱动)可以让用户自动生成测试激励进行功能验证。

随机测试比传统的定向测试方法更有效。通过指定约束,可以轻松进行难以触及的corner cases(极端情况)的验证。 的验证。

在Verilog中,我们使用**$random**方法生成随机整数值,它返回32位随机值。

为了帮助基于类的对象进行随机化,SystemVerilog支持rand变量和**randomize()**方法。

Random Variables

可以使用rand和randc声明随机变量。

rand

使用rand关键字声明的变量是标准随机变量。它们的值在允许范围内均匀分布。

randc

使用randc关键字声明的变量是随机循环(random-cyclic)变量, 随机循环遍历其声明范围的所有值。随机循环变量只能是reg或enum类型,并且最大限制为16位,因此任何randc变量的最大范围是0到65535。

constraint\_mode()

Systemverilog提供预定义的**constraint\_mode()和rand\_mode()**方法来控制某些约束是active的还是 inactive的。所有约束最初都是active的。

当我们想要为不同的配置进行不同的类随机化时,管理约束模式非常有用。

randomize() with

此方式允许在调用randomize()类方法的位置处增加新的约束。 这些附加约束与随机类中声明的约束形式相同。

pre/post randomize()

每个class 都包含内置的pre\_randomize()和post\_randomize()任务,这些任务在计算新的随机值之前和之后由randomize()自动调用。

您可以使用pre\_randomize()以执行初始化并在对象随机化之前设置条件。然后使用post\_randomize()以在对象随机化后执行清理,打印诊断和检查。

program pre_post_randomize;

class frame_t;

rand bit [7:0] data;

bit parity;

constraint c {

data > 0;

}

function void pre_randomize();

begin

$write("pre_randomize : Value of data %b and parity %b\n",data,parity);

end

endfunction

function void post_randomize();

begin

parity = ^data;

$write("post_randomize : Value of data %b and parity %b\n",data,parity);

end

endfunction

endclass

initial begin

frame_t frame = new();

integer i = 0;

$write("-------------------------------\n");

$write("Randomize Value\n");

$write("-------------------------------\n");

i = frame.randomize();

$write("-------------------------------\n");

end

endprogram

输出

-------------------------------

Randomize Value

-------------------------------

pre_randomize : Value of data 00000000 and parity 0

post_randomize : Value of data 00000110 and parity 0

-------------------------------

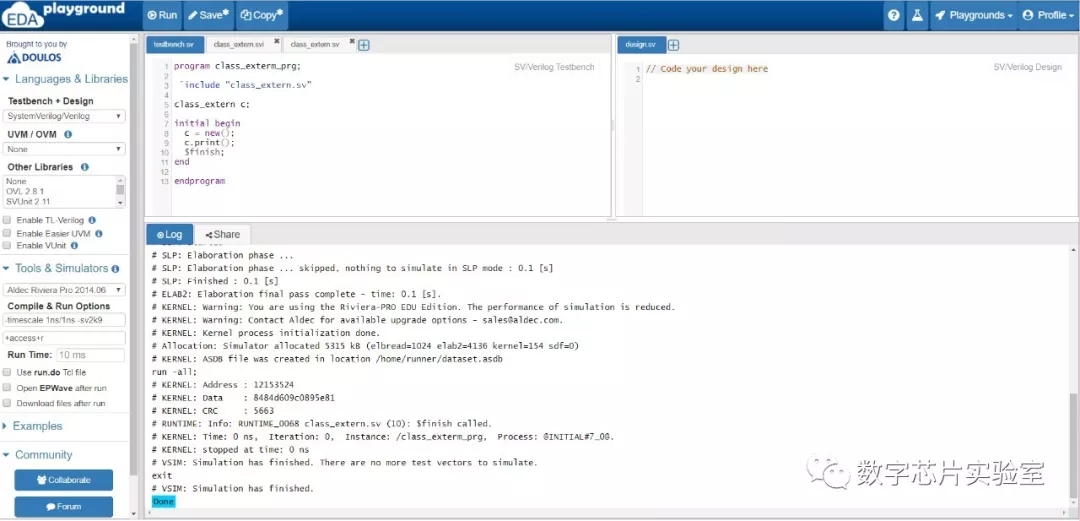

SystemVerilog系列所有文章都可以在下面这个网站上在线仿真哦。

本文转载自公众号:芯片数字实验室

原文链接:

https://mp.weixin.qq.com/s/ngRoCSOS8km\_EJMcX-HuPg

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏