本文的目标是在 ZCU102 开发板上搭建可以运行 SDK LwIP Demo 的硬件平台。并在搭建平台的过程中熟悉 Zynq ultraScale+ 平台,并观察下 ZCU 平台和普通 Zynq 平台的区别。

作者:李凡

来源: https://zhuanlan.zhihu.com/p/87081378

配置 PS 外设

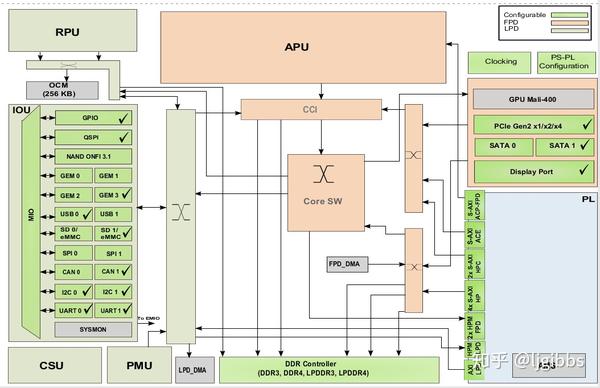

运行 LwIP 需要以太网 MAC,定时器等外设,此 Demo 运行完全基于 ARM 的 processor system,所以只需要配置 ARM 的外设即可。ZCU102 的 PS 部分基于四核的 A53 处理器,性能强劲,后续测试环节中的性能令人期待。

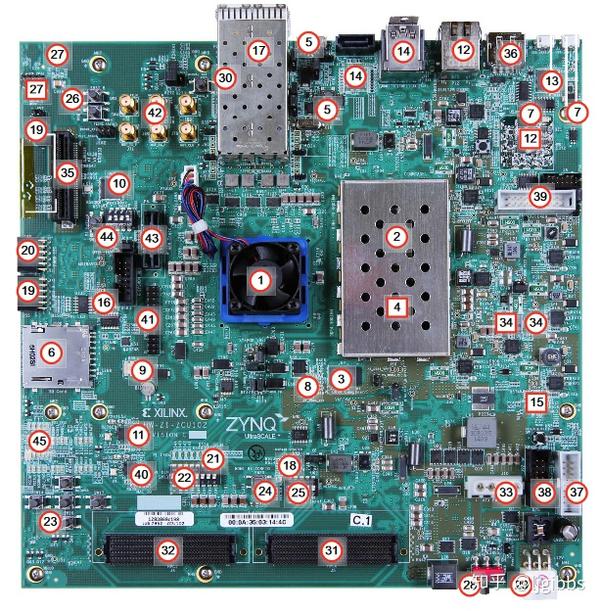

配置以太网外设,ZCU 共有四个以太网外设,我们需要使能开发板上 RJ45 口对应的外设,下图中上方的 12 号外设。

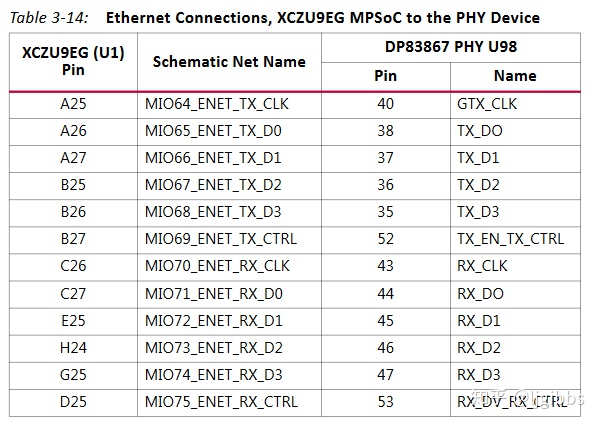

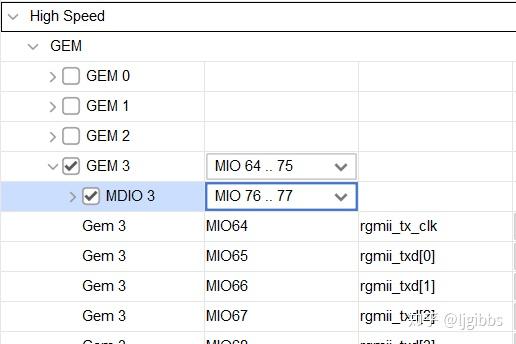

根据开发板手册,该网络使用的是 MIO64-72,所以使能 GEthernet3

这里吐槽下手册,手册也不直接告诉我是哪个以太网外设,还要我一个个找过来-\_-||\,同时勾选 MDIO,这个在开发板上也是连接好的。

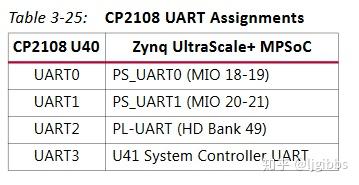

配置串口,连接开发板上的串口 usb 接口(13)后,可以找到 4 个外设设备,分别有不同的连接

这里我们使能连接在 MIO 上的两路串口

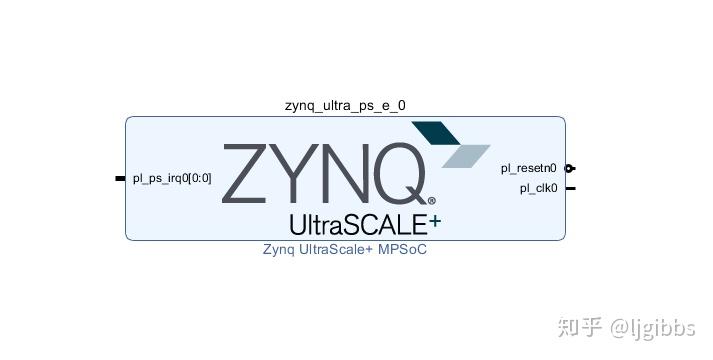

因为我们的Demo完全在PS上运行,所以不需要添加其他逻辑 IP,时钟复位也不需要在硬件上设置,也不用进行 IO 约束,所以我们的系统如下,目前 ZCU102 还只是一个昂贵的 A53 开发板。

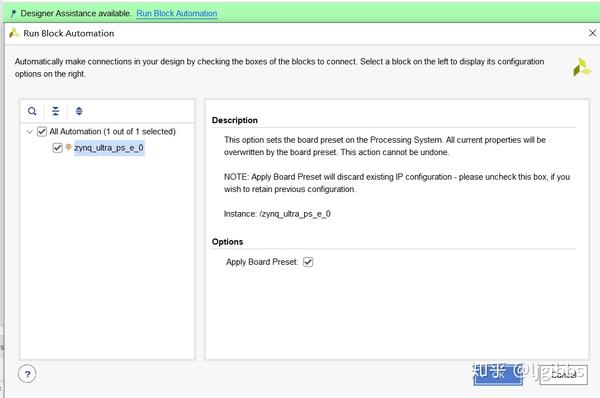

其实可以一键搞定

我在配置完之后发现,其实还有一种自动配置的方式,在添加处理器子系统之后,自动生成开发板预设模式,包括外设的配置以及各项参数,都会自动设置为开发板对应的选项。

不过自动设置会使能很多不需要的外设,还是可以自己手动设置一次,在设置的过程中熟悉整个系统。

软件部分

生成硬件平台后,将比特导出到 SDK 中,新建一个软件 LwIP Echo 实例工程,就可以运行啦。这个过程和普通的 Zynq 没有区别。

整个 Demo 搭建流程结束后,发现整个流程非常简单,简单到好像没有必要写这篇文章 -\_-, 不过这都有赖于 Xilinx 的软硬件环境,以及老师买了 Xilinx 的评估板。

总结

本文愉快地搭建了基于赛灵思 ZCU102 评估板的硬件平台,在后续的文章中我们将深入 zcu 平台,分析一些与普通 Zynq 平台的区别,比如 AXI 接口的名字就发生了改变。同时我们将在工程中引入 PL 部分完善系统。

推荐阅读

关注此系列,请关注专栏FPGA的逻辑