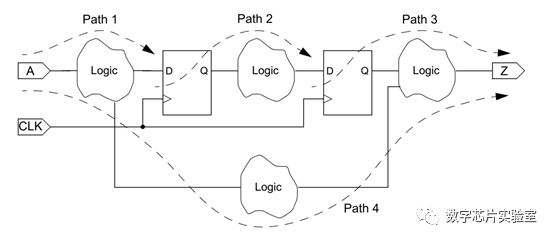

时序分析工具可以查找并分析设计中的所有时序路径(timing paths)。每条时序路径有一个起点(startpoint)和一个终点(endpoint)。

起点是设计中数据由时钟边沿触发的位置。数据通过时序路径中的组合逻辑传播,然后被另一个时钟边沿在终点捕获。

时序路径的起点是时序元件的时钟引脚或设计的输入端口。

时钟边沿在起始点触发数据。输入端口也能被视作起点,是因为输入端口是由外部源触发的。

时钟边沿在终点捕获数据。输出端口也能被视作终点,是因为输出端口是在外部捕获的。

每条路径从时序路径起点开始,经过一些组合逻辑,然后在终点被捕获:

•Path 1:从输入端口开始,到达时序元件的数据输入。

•Path 2:从时序元件的时钟引脚开始,到时序元件的数据输入。

•Path 3:从时序元件的时钟引脚开始,到输出端口结束。

•Path 4:从输入端口开始,到输出端口结束。

设计中的每条路径都有一个相应的时序slack(timing slack)。slack是一个时间值,可以是正的,零或者负的。具有最差slack的单一路径称为关键路径(critical ****path)。

我们可以将设计的时序路径分组,以便进行时序分析、报告和优化。例如,可以将输入到寄存器(input-to-register),寄存器到寄存器(, register-to-register)和寄存器到输出(register-to-output)路径分成三个单独的组,因为它们具有不同类型的时序约束。

默认情况下,设计中使用的每个时钟都有一个时序路径组(path group)。

以下是report\_timing命令生成的典型时序报告:

默认情况下,report\_timing命令报告每个路径组(path group)中建立时间最差的时序路径。

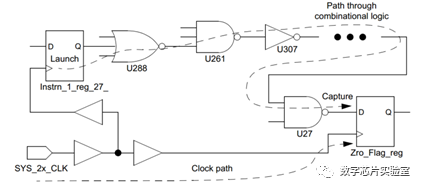

在此示例中,与时序报告的路径关联的逻辑如下图所示:

时序报告首先显示时序路径起点(Startpoint),时序路径终点(Endpoint),时序路径组(path group)名称和时序路径检查类型。

在此示例中,时序路径检查类型为**“max”,表示最大延迟或建立时间检查**; “min”表示最小延迟或保持时间检查。

时序报告显示了沿着路径的延迟计算。该表包含Point,Incr和Path的列,分别列出了沿着时序路径的点(引脚),每个点对延迟的贡献,以及到那一点的累积延迟。

Incr列中的星号(*)符号表示SDF反标延迟的位置。“Path”列中的字母“r”和“f”表示在时序路径中的那个点上,信号转换是上升还是下降。

表中显示的“数据到达时间(data arrival time)”是path group中延迟最长的路径延迟。

“数据所需时间(data required time)”是时序路径中数据的允许到达时间,考虑了捕获时钟边沿时间,时钟网络延迟,时钟不确定性以及库的建立时间要求。

时序报告末尾显示的slack值是data required time减去data arrival time。

在这个例子中,slack是一个非常小的正值,这意味着时序约束恰好得到满足。负slack需要改变设计来fix 时序违例。

例如,时序路径中的驱动单元可以用更大的单元替换,以获得更大的驱动强度,这将减少线延迟。另一方面,一个很大的正slack可以将时序路径中的驱动单元可以替换成较慢,较小的单元来减少面积或较慢的,较高阈值的单元来减少泄露功耗。

本文转载自公众号:芯片数字实验室

原文链接:

https://mp.weixin.qq.com/s/\_a71IuilEX9JONLKbrd86g

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏