//来自微信公众号 "数字芯片实验室"

降低功耗可以从RTL-level和Gate-level设计策略着手。诸如时钟门控(clock gating)之类的方法已被广泛地使用。其他的方法,例如动态电压和频率调节,由于难以实施,还没有被广泛地使用。在更先进地工艺中,功耗变得越来越重要,正在开发更多的方法来实现设计的功耗要求。

1、降低电源电压

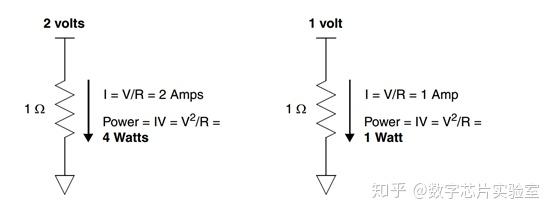

降低功耗的最基本方法是降低电源电压。 功耗与电源电压的平方成正比,如图1中的示例所示。 电源电压降低50%会导致75%的功耗减少。

CMOS技术使用越来越低的电源电压来减少功耗。 从20世纪80年代双极TTL电路的5 V供电电压开始,目前的先进工艺,电源电压已降至约1 V。但是降低电源电压来降低功耗的同时,但也降低了开关速度。

此外,降低晶体管阈值电压,会导致更多的问题,例如抗噪声能力,泄漏电流。 较低的电压摆幅使芯片与外部设备接口变得更加困难。

2、时钟门控

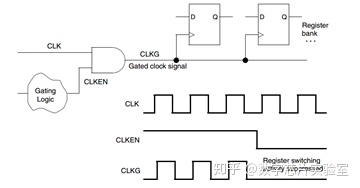

时钟门控是一种动态功耗降低方法,在寄存器存储的逻辑值不变的时候,停止其触发时钟信号。时钟门控的实现如图2所示:

时钟门控对于在许多时钟周期需要保持相同逻辑值的寄存器特别有用。 关闭时钟可以消除不必要的开关活动,否则会在每个时钟周期都会重新触发寄存器。 时钟门控的主要挑战是找到使用它的最佳位置,并在正确的周期创建时钟门控的开关逻辑。

时钟门控是一种成熟的降低功耗技术,已经使用了很多年。

Power Compiler等综合工具可以在时钟路径适当的位置自动插入时钟门控单元。 时钟门控实现起来相对简单因为它只需要改变网表。

3、多阈值标准单元库

一些CMOS标准单元工艺库具有不同的阈值(Vt)。 在这种情况下,标准单元库可以提供带有不同阈值电压的标准单元来实现相同的逻辑功能。例如,该库可以提供两个反相器单元:一个使用Low -Vt晶体管,另一个使用High-Vt晶体管。

Low -Vt单元具有更高的速度和更大的泄漏电流。 High-Vt单元漏电流小,但速度较慢。 综合工具可以基于速度和功耗之间的trade off选择合适类型的标准单元。 例如,它可以在关键路径使用Low -Vt单元,在非关键路径使用High -Vt单元

4、多电压设计

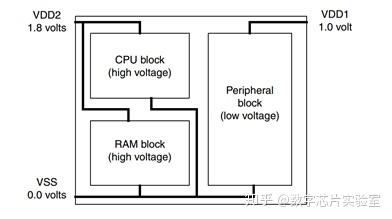

芯片的不同部分可能具有不同的速度要求。 例如,CPU和RAM模块可能需要比外围模块更快。 如前所述,较低的电源电压降低功耗,但也会降低速度。 所以,CPU和RAM以更高的供电电压运行,而外围模块在较低电压下工作,如图3所示。

在单个芯片上提供两个或更多电源电压会带来一些复杂性。 必须有额外的引脚来提供芯片电压和电源网格必须将每个电压源分别分配给适当的模块。

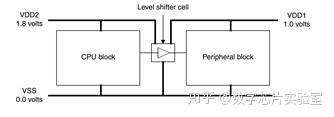

如果逻辑信号离开一个电压域并进入另一个电压域,则需要一个level-shifter单元产生带有合适的电压摆幅的信号。 在图4所示的示例中,level-shifter转换1.8V电压摆幅的信号到1.0V电压摆幅的信号。 level-shifter单元本身需要两个与输入和输出电源电压相匹配的电源。

5、电源开关

电源开关是一种降低功耗的技术,其中芯片的一部分在不活动期间被完全关闭。 例如,在手机芯片中,当手机处于待机模式时,可以关闭语音处理功能。 当用户拨打电话或接听外线电话的时候,语音处理块必须从断电状态“唤醒”。

电源开关可以大幅降低总体功耗,因为它同时降低了泄漏功耗以及动态功耗。 它还引入了一些其他挑战,包括对电源控制,电源开关网络,isolation cells和retention registers 的需求。

电源控制是一个逻辑块,用于确定何时断电和上电。 打开和关闭电源需要一定的时间和功耗成本,电源控制器应确定适当的断电时间。

可以被断电的模块必须连接到由大量源 - 漏连接的,在always-on的电源轨道和cell的电源引脚之间的晶体管组成的电源开关网络。 电源开关网络分布在模块的周围或内部。 电源开关网络被打开时,将电源连接到模块中的逻辑门。 关闭时,电源从模块中的逻辑门断开。

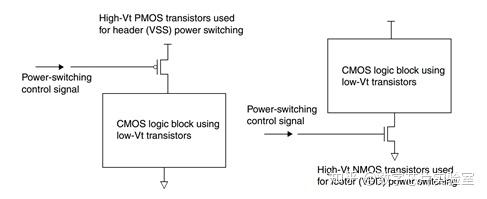

采用多阈值CMOS(MTCMOS)工艺的High-Vt晶体管作为电源开关是因为它们可以最大限度地减少功耗泄漏,并且它们的开关速度不是非常的关键。PMOS开关可以放置在VDD和模块的电源引脚之间,NMOS开关可以放置在VSS和模块接地引脚之间,如图5所示。要合适地选择开关的数量,驱动强度和位置,以使得在模块中的峰值功耗使用期间达到可接受的电压降(IR Drop)。

图5所示的电源开关策略称为粗粒度策略,因为电源开关应用于整个模块。 并联的多个晶体管共同驱动为模块供电的电源网络。 在细粒度策略中,每个库单元都有自己的电源开关。 细粒度策略有更好的功耗降低潜力,但需要更多的面积。

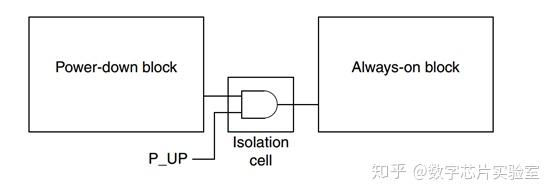

在信号离开断电模块并进入always on模块的地方,任何电源开关的使用都需要isolation cells。当断电模块被断电时, isolation cells提供一个已知恒定逻辑值给always-on模块,从而防止可能的电流泄露。

isolation cell 的一个简单实现如图6所示。 当左边的模块上电时,信号P\_UP为高电平,输出信号通过isolation cell不变(除了延迟)。 当左边的模块关闭时,P\_UP为低电平,保持恒定逻辑0进入always-on模块。 其他类型的isolation cell可以保持逻辑1而不是0,或者可以保持电源关闭时刻当时锁存的信号值。 在模块断电期间,isolation cell本身必须具有供电。

电源开关可与多电压结合使用。不同的模块可以在不同电压下工作,并且在它们也可以单独断电。 在这种情况下,不同模块之间的接口单元必须执行level shifting 和isolation功能。 执行这两种功能的单元称为enable level shifter。 该单元必须具有两个独立的电源,就像其他level shifter一样。

当模块被断电然后再上电时,通常需要模块恢复到掉电之前的状态。 有几种方法可以达到这样的效果。例如,断电前模块寄存器内容可以复制到模块外面的RAM,然后在上电后复制回来。

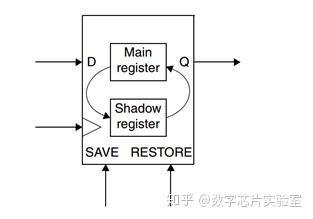

另一种策略是在掉电模块中使用retention registers。 断电前,retention registers通过将数据保存到shadow register(也称为bubble register),可以在断电期间保留数据。 上电后,它将数据从shadow register恢复到主寄存器。 shadow register具有always-on的电源,

但它采用high-Vt晶体管,以最大限度地减少掉电期间的泄漏功耗。 主寄存器采用快速但漏电的low-Vt晶体管。

一种retention register实现如图7所示。 SAVE信号在掉电和恢复之前将寄存器数据保存到shadow register中,上电后RESTORE信号恢复数据。 retention register使用电平敏感的控制信号,而不是边沿敏感的SAVE和RESTORE信号。

retention register占用比普通寄存器更大的区域,除了模块其余部分使用的电源,它还需要一个always-on的always-on电源连接。

6、动态电压和频率调节

扩展多电压的原理,可以允许在芯片工作期间改变电压以匹配当前的工作负载。 例如,笔记本电脑中的处理器芯片进行简单的电子表格计算时可以在较低的电压和较低的时钟频率下工作,从而节省功耗; 然后继进行3-D图像渲染时,在更高的电压和更高时钟频率下工作。 芯片工作期间供电电压和工作频率的变化满足工作负载要求称为动态电压和频率调整。

芯片电源可以设计为多个级别,甚至是连续的电源范围。 动态电压调节需要多级电源和逻辑模块确定用于给定任务的最佳电压电平。由于电源范围以及电压电平和工作频率的组合,设计,实现,验证和测试都特别具有挑战性。

动态电压调节可以与电源开关技术相结合。设计中的模块可以在多个电压电平下工作,以实现不同的性能要求,或在不需要时完全关闭。

欢迎关注微信公众号 数字芯片实验室

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/xyd0gTwyhNAH3pk9OTiqhg

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏