标准单元placement是ASIC物理设计中非常重要的阶段。

标准单元placement的目标是将ASIC设计中的标准单元映射到core区域中标准单元placement的位置(row)。

ASIC物理设计中标准单元placement对物理设计的面积优化、走线拥塞和时序收敛有非常关键的影响。

当今的物理设计工具不断优化算法来自动place标准单元,但基本理念相同。

大多数布局布线工具使用两步(global placement和detail placement)来place标准单元。global placement的目标是最小化互连线长度,而detail placement的目标是满足设计的时序、拥塞等要求,并最终确定标准单元的placement位置Global Placement完成floorplan之后,标准单元的位置还没有确定。布局布线工具支持很多选项(cluster和region)用于指导标准单元的placement。

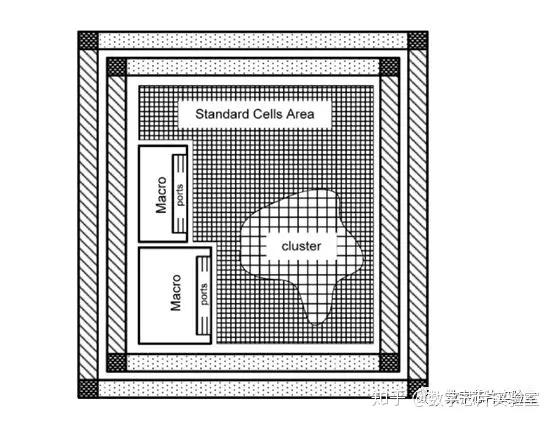

cluster是指在placement期间,一组标准单元彼此靠近放置。在所有标准单元被完全放置之前,cluster的位置是未知的。 cluster选项主要用于在placement期间控制timing-critical模块placement的接近程度。但是由于互联线长度驱动的placement算法的发展,该选项不是很常用。

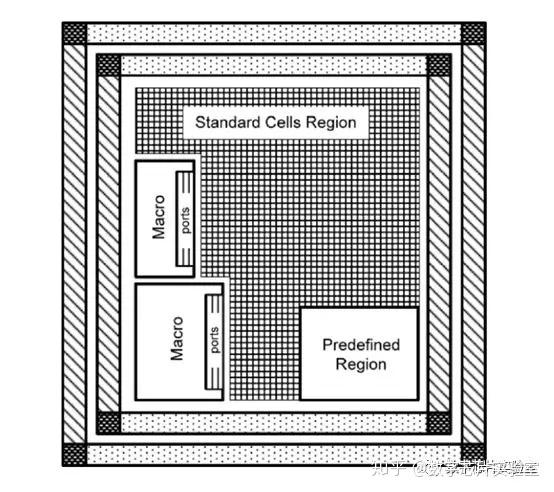

Region与cluster相似,但是Region是在标准单元placement之前设置的。

Region的类型可以是soft或这hard。hard region比soft region更加严格,它在placement期间阻止标准单元穿越“hard”边界。

global placement定义了标准单元初始placement位置。同时工具会插入buffer来解决高扇出,长走线的问题的,如果关键路径有较大的时序违例还会对设计进行逻辑上的优化。

如果ASIC设计考虑了DFT,placement还会根据标准单元placement位置进行扫描链reorder。扫描链reorder可以改善走线拥塞。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/HHnhXro8A84gFybWrXpfSA

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏