在floorplan时,需要进行宏模块placement。 这些宏模块可能是存储器或者模拟模块。在层次化物理设计中也可能是单独布局布线的子模块。 正确place这些宏模块对ASIC设计最终物理实现的质量有很大影响。

宏模块placement可以是**手动或自动的。**通常在宏模块数量较少,并且知道这些模块之间的关系时,会选择手动place宏模块。如果不知道宏模块之间的关系,或者宏模块数量较大时可以使用工具自动place宏模块。

在宏模块placement过程中需要确保模块之间存在足够大的区域用于互连。

大多数的物理设计工具都使用global placer来执行自动宏模块placement以减少互连线长度

一个成熟的宏模块placement算法必须能够处理不同的形状、大小和方向的拥塞或者时序驱动(congestion-driven or timing-driven)的placement。 但是,为了以确保placement的质量,还需要根据需要手动修改这些宏模块的位置和方向。

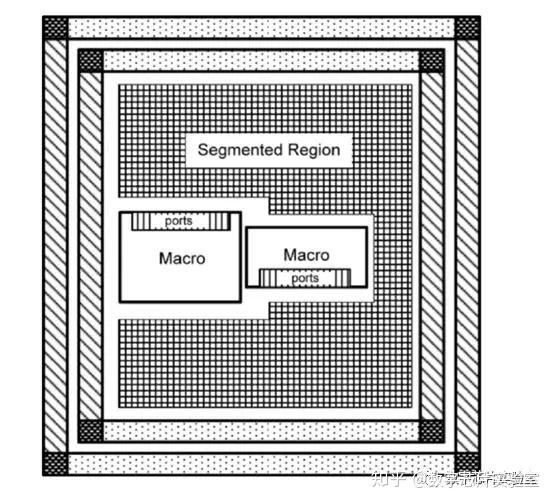

总的走线长度是衡量宏模块placement的一个指标。为了减少总的走线长度,要确保core区域不被宏模块分割。

标准单元placement区域应该是连续的,此时能够充分利用芯片core区域, 有效地减少总的走线长度。

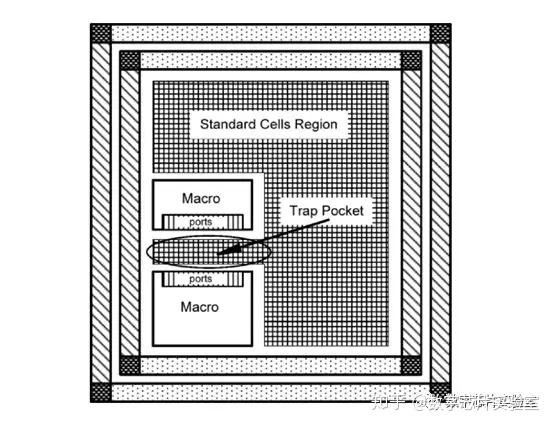

宏模块placement的pin的方向不同,总的走线长度是不同的。

宏模块的pin应该朝向标准单元或者core区域。

衡量芯片布局的另一个方面是global router评估出来的“可走线性”,即走线拥塞(routing congestion)。

大多数global router工具都能够生成图形和文本报告。图形报告,也称为congestion map,在视觉上报告出拥塞的位置(hot spots)。文本报告统计出了走线拥塞的具体数据。

最可能导致走线拥塞的原因是宏模块之间可能没有足够的空间用来走线

在宏模块placement之后,global routing之前,你可能需要画一个包含宏模块的keep-out或者buffer-only区域,以防止标准单元被place到这些区域。

很显然,这些区域内的走线会比较长,我们可以通过buffer-only允许插入buffer,从而避免长走线造成的大transition time值。

当宏模块上添加了Blockage layers时,宏模块corner周围的走线容易发生拥塞,这种拥塞也是可以继续通过Blockage layers解决。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/aIzCBjszg7RvMsl-gBq3TQ

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏