源自微信公众号 “数字芯片实验室”

设计完数字系统后,通过仿真进行逻辑功能验证非常重要。在Verilog中,可以编写testbench(测试平台)以验证代码。下面是编码testbench的一些基本指南(guideline):

1、Testbench实例化设计的顶层并为其提供激励(stimulus)。

2、设计(DUT)的输入激励声明为'reg'类型。 reg数据类型在always或者initial语句块中重新赋值。

3、设计(DUT)的输出声明为“wire”类型。 “wire”类型数据不能在always或者initial语句块内赋值。

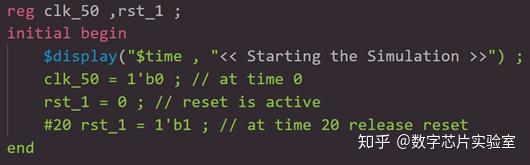

4、always和initial语句块是两个时序控制块,它们相互之间是并行执行的。 initial语句块的示例如下所示:

设计完数字系统后,通过仿真进行逻辑功能验证非常重要。在Verilog中,可以编写testbench(测试平台)以验证代码。下面是编码testbench的一些基本指南(guideline):

1、Testbench实例化设计的顶层并为其提供激励(stimulus)。

2、设计(DUT)的输入激励声明为'reg'类型。 reg数据类型在always或者initial语句块中重新赋值。

3、设计(DUT)的输出声明为“wire”类型。 “wire”类型数据不能在always或者initial语句块内赋值。

4、always和initial语句块是两个时序控制块,它们相互之间是并行执行的。 initial语句块的示例如下所示:

initial语句块在仿真时间0开始按顺序执行“begin end”之间的语句。当到达延迟时,该语句块等待延迟,然后继续执行。

示例中的initial语句块首先打印<< Starting the Simulation>>,并在时间0将clk\_50和rst\_l初始化为0。然后,仿真时间前进到20 ns,并且rst\_l赋值为1’b1。

结果是,仿真中复位脉冲从低到高持续20 ns。

5、系统任务。 综合工具会忽略这些系统任务,因此可以在设计代码中使用它们。 系统任务以'$'符号开头。 一些系统任务如下:

$display:仿真过程中,在屏幕上显示文本

$ monitor:每当参数变化时,在屏幕上显示文本

**$strobe**:与$ display相同,但仅在仿真时间单位结束时打印文本

$ stop:停止仿真。

$ finish:退出仿真

$ dumpvar,$ dumpfile:dump波形,转储到文件中。

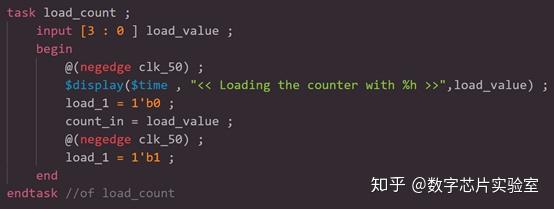

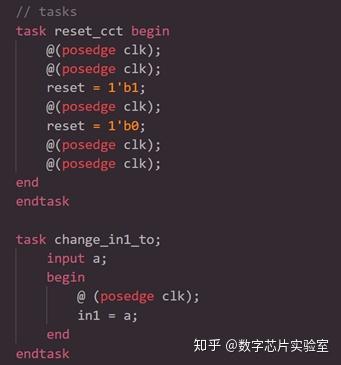

6、tasks用于实现常用的验证功能。tasks可以有输入,输出,并且可以包含时序控制。 下面是一个task的例子:

此task采用一个4位输入,并在下一个clk\_50的下降沿打印文本到屏幕,驱动load\_l为低,并赋值count\_in为输入值 load\_value。 然后在clk\_50的下降沿,load\_l信号被释放。

必须在always和initial语句块中调用该task。

还可以使用不同的输入值对该task多次调用。

7、编译指令\`timescale:

这行命令在Verilog仿真中很重要,因为它设置了时间单位和时间精度。

8、Verilog测试平台可以使用包含C语言描述的编程语言接口(PLI)。

9、在编写testbench之前,了解设计规范(spec),并且创建所有可能的测试用例列表非常重要。

10、可以根据波形检查信号值是否正确

11、在编写testbench时,可以设置断点,也可以单步执行

12、进行功能仿真时,最好进行受约束的随机仿真。受约束的随机仿真可以提供有效输入的随机组合。当随机仿真运行很长时间时,它可以覆盖大部分所有的corner cases。在verilog中,可以使用$ random在testbench中创建随机变量。

13、覆盖率统计:观察存在多少种可能性以及有多少种可能性已经通过仿真。

13.1、行覆盖率:代码中的行仿真覆盖百分比,由仿真工具统计。

13.2、条件覆盖:它检查代码中的各种条件语句覆盖百分比。

13.3、状态机覆盖率:检查状态转换覆盖百分比

13.4、 回归测试(Regression):将新的模块添加到已验证的代码中。代码需要再次进行验证,查看新的功能模块是否正常工作并验证旧功能模块是否会由于添加了新功能出现功能故障。

仿真的目标是:

1.功能正确:通过验证来验证设计的功能,主要的test cases(主要功能)和corner cases(特殊条件下)

2.设计的错误处理

3.性能

Testbench示例:

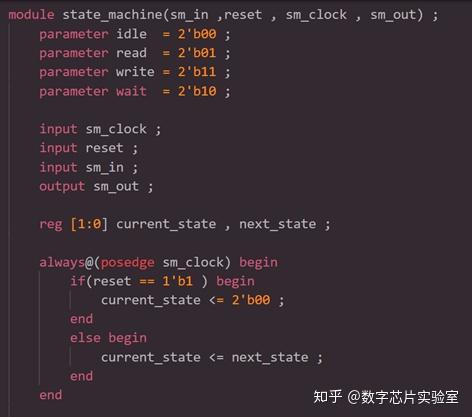

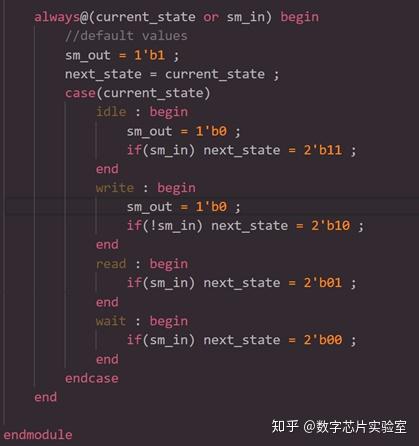

以下是简单的状态机设计:

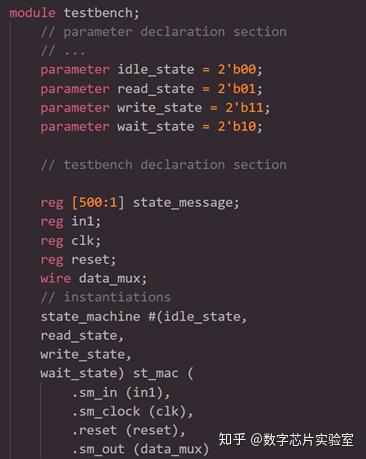

验证状态机的testbench的示例:

在软件的功能仿真之后,如何在真实世界中仿真你的设计呢?

1、 FPGA原型:加快验证速度。

2、硬件加速器:将一些可综合的代码映射到FPGA上。其他不可综合的部分,如testbench用仿真工具驱动。当设计非常大时,这种硬件加速验证方法能大幅度提高验证效率。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/bVsqMnDwTyEXsDoH2z\_efw

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏