来自微信公众号 “数字芯片实验室”

门级仿真(Gate level simulation)是对综合后,已经完成映射(mapping )到工艺库的数字设计进行验证的方法。

在进行门级仿真时,综合后的网表和仿真模型被加载到仿真器中。仿真器根据仿真模型确定逻辑门的输出是否会根据输入的变化而变化,追踪每个逻辑门的输入输出状态。

门级仿真可以不添加延迟(zero delay)或带有延迟(back-annotated)进行仿真。

VHDL和Verilog都提供非“0”和非“1”的值('X'、'Z'等)来表示一个未知逻辑值。

在门级模拟时,一个cell确定的输入必须要知道相应的输出,逻辑“0”或逻辑“1”。

但是如果cell library无法确定输出的逻辑值,就会输出未知的逻辑值X。

不定态X的来源

大多数设计在上电时不能保证cell的特定的逻辑状态。flip flop或memory根据环境因素,芯片间的工艺差异等可能会有不同的初始态(可以根据这种特性设计出SRAM PUF)。

因此,在仿真时间0时,flip flop或memory会输出X,直到在第一个时钟沿被加载一个新的逻辑值。

在仿真中还有其他一些常见的不定态X来源:

•缺少仿真模型,或仿真设置中出现其他错误。

•对于testbench外部输入信号没有设置初始值

•一些锁相环时钟仿真模型输出X ,直到lock

•发生时序违例(timing violation)

•当使用back annotated时序进行仿真时,输入信号传播到之前还是不定态X

•一些cell library在任何一个输入是X时,就会输出X,即使已知输出的逻辑值。

不定态X的传播

在现实中不会存着真正的X逻辑值,只是cell library考虑到所有可能组合,最终无法确定输出的逻辑值。

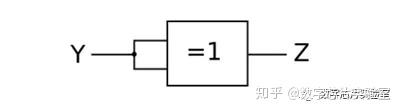

module xor_usr(

input xor_in ,

output xor_out );

assign xor_out = xor_in ^ xor_in ;

endmodule

module xor_tb;

reg xor_in ;

wire xor_out ;

xor_usr xor_usr(

.xor_in(xor_in) ,

.xor_out(xor_out) );

initial begin

#10 ;

#10 xor_in = 1 ;

#10 ;

$finish ;

end

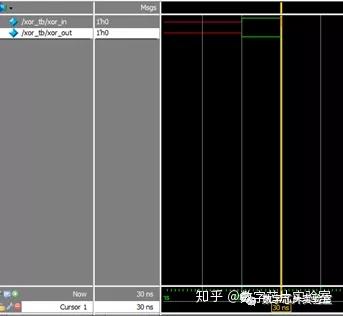

endmodule这个简单的例子只是一个XOR门,其输入连接在一起。这样的门将始终输出逻辑“0”,但在输入为X时,结果会输出X。

在实际设计中,这种输入连接在一起的异或门会被综合工具优化掉。

在设计上解决不定态X的传播的方法就是对设计进行复位操作,在testbench中就是初始化输入和强制调整传播不定态的信号。

强制调整传播不定态的信号非常有效,但是会减少test coverage。也可以对这些强制调整的不定态信号设置随机启动值进行仿真。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/kd4mHMPBL1riZhYVj\_AyTw

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏