来自微信公众号 “数字芯片实验室”

要获得一个高质量的Topographical synthesis结果,需要一个良好的physical start point。

我们习惯使用后端工具做floorplan,使用Topographical synthesis工具进行综合,但是这导致了前端和后端团队之间的迭代。

本文通过实际设计展示Design-Compiler Graphical(DC-G)如何提供帮助消除前端/后端迭代并简化修改floorplan流程。

DC-G根据最初的floorplan分析congestion和timing,然后在DC-G内修改floorplan优化综合结果。

1. Introduction

Since many years, topographical synthesis is the master word andtalking about wire load model based synthesismakes any user appear as an obsolete designer.

但是,topographical mode需要确定的floorplan信息,这需要在前后端之间进行多次的迭代。

2. Design Presentation

As we all know, in thistechnology using 40nm (<= 40nm》)transistor channellength, capacitive and resistive wire values are a key factoron timing effectand early back-end oriented estimation are mandatory to allow timing closurebetween front-endand back-end world.

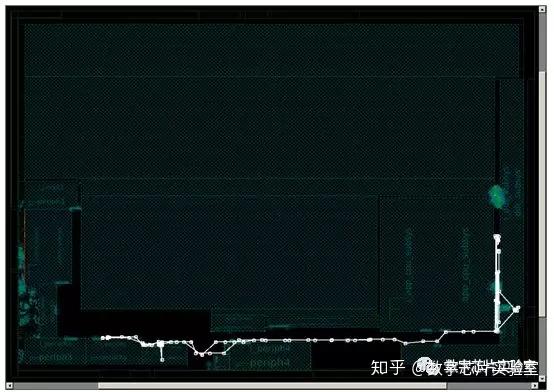

由后端团队进行的初步研究,以估计芯片的total die size、routability和area estimation foreach IP,获得下图所示的第一个Floorplan信息。

3. Design Status with currentflow

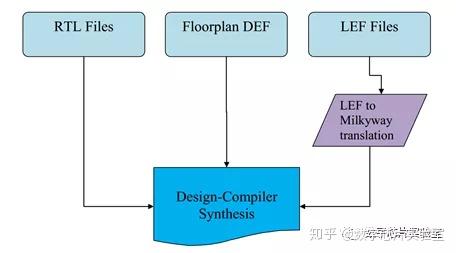

3.1. Design Flow

现在,使用第一个floorplan信息,进行初步的topographical synthesis

1. RTL files

2. floorplan DEF file

3. LEFfiles (Milkyway physical database)

3.2. Design result

初步的topographical synthesis具体步骤如下

RTL analysis and elaboration

Timing Constraints read

DEF floorplan read (extract_physical_constraint)

Compilation (compile_ultra -scan -no_autoungroup -gate_clock)

Reports and database save3.2.1. Routablity analysis

我们可以看到congestion map和worst timing path.

3.2.3. Preliminary conclusi

结论很清楚:

performing early floorplanning and using Design-Compiler intopographical mode is bringing early information to the design team and allows anticipationon backend problems

下一步的工作也很清楚: refine thefloorplan

4. Design-Compiler Graphical Improvement

4.1. DC-Graphical 2010.03 new features

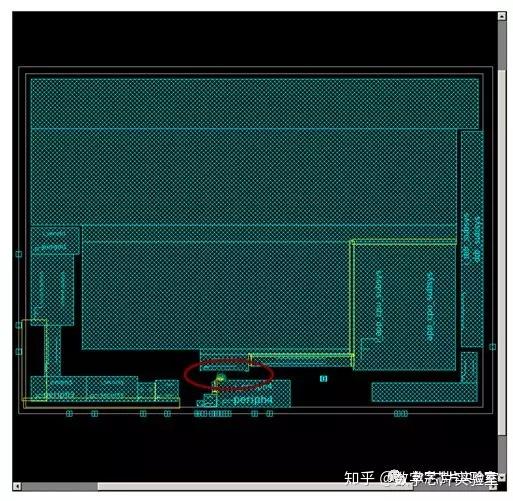

2010.03版本在Design-Compiler Graphical中引入了一项新feature:直接在DC-G内更新floorplan,然后进行第二次综合。

“Floorplan → Createplacement blockage” ,最后获得下面更新后的floorplan。黄色的为placement blockage

在完成floorplan更改之后,工具会自动使用新的floorplan信息。然后我们可以write\_floorplan \<floorplan.tcl>,并使用新的floorplan.tcl文件从头开始综合,也可以 compile\_ultra -scan-incremental

与最初floorplan的congestion map和worst timing path.相比,第二次的综合结果有了很大的改善。

5. Conclusion

使用Design-Compiler Graphical可以在后端物理实现之前检查设计中可能存在的congestion问题。

过去,当遇到congestion问题时,Synopsys工具提出的唯一解决方案是使用compile\_ultra的“ -congestion”选项,但这个选项会对时序收敛产生负面的影响

you gain on onehand what you loose on the other

在2010.03版本中,DC-Graphical引入了解决congestion问题的新方法,通过使前端工程师修改floorplan,避免了前后端团队之间的漫长的迭代。

Reference paper link :

How Design-Compiler Graphical helps solving floorplanning issues

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/1J8YiFmmx-1Sp4j18v3EoQ

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。