写此文时,时间临近国庆。中午的阳光还似盛夏,不过气温低了许多。路边插了很多红色的旗帜,超市的折扣让这几天更加喜庆。

在数字IC的相关笔试当中,不可避免会遇到各种时序分析笔试题,

1、求最大工作频率

2、分析设计setup/hold是否违例,违例了该怎样修复?等等

针对这样的问题,我们可以自己编码相应的设计,然后使用工具进行时序分析。这样就再也不用为了简单的时序分析问题去问大佬们了,才能有尊严地做一条咸鱼\~\~

经过研究,我发现使用set\_annotated\_delay/set\_annotated\_check,就足够满足我们的需求,即自定义反标设计中cell/net延时,自定义触发器的setup/hold检查。具体使用可以参考Synopsys工具的manpage或者google

也就是说,我们虽然使用了target\_library来综合我们的设计,实际上并不会用到std cell库里面的时序信息。使用set\_annotated\_delay/set\_annotated\_check也并不需要了解lib库的格式。

下面以几道时序分析题为例来演示如何使用set\_annotated\_delay/set\_annotated\_check命令,让工具替你完成时序分析以验证自己的计算结果。

示例

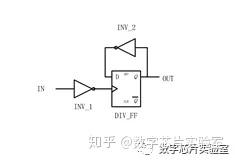

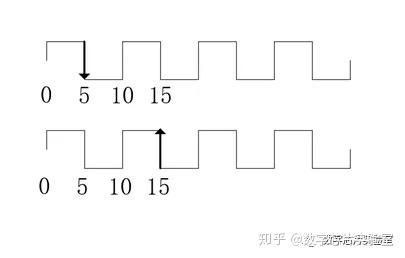

如下一个分频电路,触发器DIV\_FF的建立时间为2ns,保持时间为2ns,逻辑延时为6ns,反相器INV\_1,INV\_2的逻辑延时为2ns,连线延时为0.那么该电路正常工作的最高频率为多少?

STEP1 Verilog Coding

module test( output reg out , inout clk );

wire clk_inv ;

assign clk_inv = ~clk ;

always@(posedge clk_inv )begin

out <= ~out;

end

endmodule然后直接compile,工具并没有综合成我们想要的电路结构。

重新编码

module test_inv( input clk , output reg out);

wire clk_inv ;

not inv_ins1 (clk_inv,clk) ;

wire out_inv ;

not inv_ins2 (out_inv,out) ;

always@(posedgeclk_inv) begin

out <= out_inv;

end

endmodule设置

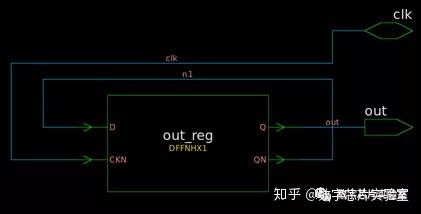

set_dont_touch [get_nets *] trueSTEP2 Compile

工具终于综合出了我们想要的电路结构

STEP3 定义延时

接下来,就需要为上述电路结构自定义我们的cell/net延时,施加约束,才能让工具进行时序分析

自定义cell延时:

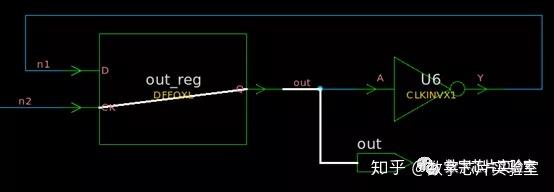

set_annotated_delay 6 -cell -from out_reg/CK -to out_reg/Q //dff CK->Q

set_annotated_delay 2 -cell -from U5/A -to U5/Y // inv_1

set_annotated_delay 2 -cell -from U6/A -to U6/Y // inv_1自定义触发器setup/hold检查要求:

set_annotated_check -setup -hold 2 -from out_reg/CK -to out_reg/D //dff setup/holdSTEP4 施加约束

create_clock -name clk -period 10 [get_ports clk]

set_output_delay 0 [get_portsout] -clock clkcheck\_timing:

dc_shell>check_timing

Information:Updating design information... (UID-85)

Information:Checking generated_clocks...

Information:Checking loops...

Information:Checking no_input_delay...

Information:Checking unconstrained_endpoints...

Information:Checking pulse_clock_cell_type...

Information:Checking no_driving_cell...

Information:Checking partial_input_delay...

1所有的路径都被约束上了。

STEP5 report\_timing -max\_paths 2

Path1:

Startpoint:out_reg (rising edge-triggered flip-flop clocked by clk')

Endpoint: out (output port clocked by clk)

Path Group: clk

Path Type: max

Point Incr Path -----------------------------------------------------------

clock clk' (rise edge) 5.00 5.00

clock network delay (ideal) 0.00 5.00

out_reg/CK (DFFQXL) 0.00 5.00 r

out_reg/Q (DFFQXL) 6.00 * 11.00 r

out (out) 0.00 11.00 r

data arrival time 11.00

clock clk (rise edge) 10.00 10.00

clock network delay (ideal) 0.00 10.00

output external delay 0.00 10.00

data required time 10.00

-----------------------------------------------------------

data required time 10.00

data arrival time -11.00

-----------------------------------------------------------

slack (VIOLATED) -1.00

我们发现在约束时钟周期为10ns时,存在-1ns的setup 违例,再进一步分析可以发现,违例原因是工具默认在输出out后被一个clk的上升沿触发器采样

上述如果需要指定被下降沿采样时,可以使用约束

set\_output\_delay 0 [get\_ports out] -clock clk -clock\_fall

Startpoint:out_reg (rising edge-triggered flip-flop clocked by clk')

Endpoint: out (output port clocked by clk)

Path Group: clk

Path Type: max

Point Incr Path

-----------------------------------------------------------

clock clk' (rise edge) 5.00 5.00

clock network delay (ideal) 0.00 5.00

out_reg/CK (DFFQXL) 0.00 5.00 r

out_reg/Q (DFFQXL) 6.00 * 11.00 r

out (out) 0.00 11.00 r

data arrival time 11.00

clock clk (fall edge) 15.00 15.00

clock network delay (ideal) 0.00 15.00

output external delay 0.00 15.00

data required time 15.00

-----------------------------------------------------------

data required time 15.00

data arrival time -11.00

-----------------------------------------------------------

slack (MET) 4.00我们发现时序还有很多余量

Path2 :

Startpoint:out_reg (rising edge-triggered flip-flop clocked by clk')

Endpoint: out_reg (rising edge-triggeredflip-flop clocked by clk')

Path Group: clk

Path Type: max

Point Incr Path

-----------------------------------------------------------

clock clk' (rise edge) 5.00 5.00

clock network delay (ideal) 0.00 5.00

out_reg/CK (DFFQXL) 0.00 5.00 r

out_reg/Q (DFFQXL) 6.00 * 11.00 f

U6/Y (CLKINVX1) 2.00 * 13.00 r

out_reg/D (DFFQXL) 0.00 13.00 r

data arrival time 13.00

clock clk' (rise edge) 15.00 15.00

clock network delay (ideal) 0.00 15.00

out_reg/CK (DFFQXL) 0.00 15.00 r

library setup time -2.00 * 13.00

data required time 13.00

-----------------------------------------------------------

data required time 13.00

data arrival time -13.00

-----------------------------------------------------------

slack (MET) 0.00

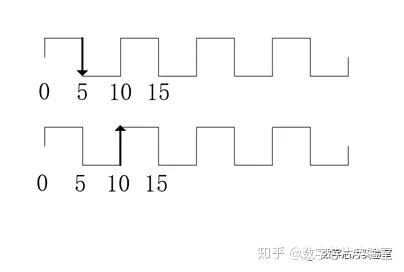

setup需要满足:

T/2 +6 +2<= T/2 + T -2T >=10,也就是说最大频率为100M

hold分析 同理

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/WzcfQeT1RMTUSShetI5n8Q

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。