转载自:知乎

本系列文章将和读者一起巡礼数字逻辑在线学习网站 HDLBits 的教程与习题,并附上解答和一些作者个人的理解,相信无论是想 7 分钟精通 Verilog,还是对 Verilog 和数电知识查漏补缺的同学,都能从中有所收获。

首先附上传送门:Dff16e - HDLBits

Problem 85 : DFF with byte enable(Dff16e)

本题中需要创建一个 16 路 D触发器。部分情况下,只需要多路触发器中的一部分触发器工作,此时可以通过 ena 使能端进行控制。使能端 ena 信号有效时,触发器在时钟上升沿工作。

byteena 使能信号以 byte 为单位管理 8 路触发器在时钟边沿触发与否。byteena [1] 作为 d[15:8] 高位字节的使能端,byteena [0] 则控制 d 的低位字节。

resetn 为同步,低电平有效复位信号。

所有的触发器在时钟上升沿被触发。

解答与分析

module top_module (

input clk,

input resetn,

input [1:0] byteena,

input [15:0] d,

output reg [15:0] q

);

always @(posedge clk) begin

if(~resetn)

q <= 16'd0;

else if(byteena[0] || byteena[1]) begin

if(byteena[1])

q[15:8] <= d[15:8];

if(byteena[0])

q[7:0] <= d[7:0];

end

end

endmodule

在按照上述的思路写代码时,注意不要在判断 byteena 时将 if...if 结构写成 if..else if ..结构,这样会在 byteena = 2'b11 时产生只判断 byteena [1],忽略 byteena [0] 的逻辑错误。

本题也可以从例化的思路进行,例化16 路带有使能端的触发器,分别将 byteena 作为高 8 位与低 8 位触发器的使能信号。

从做题的角度来说,作者曾搞反了两个使能信号导致了错误,所以做题要注意细节。

Problem 86 : D latch(Exams/m2014 q4a)

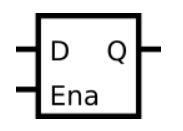

本题中需要实现一个如下的电路:

从做题的角度来说,首先你得认识这个元件。同 D触发器相比,这个元件没有 clk 端口,取而代之的是 ena 端口,所以这是一个锁存器。锁存器的特征在于,相较于 D触发器的触发事件发生于 clk 时钟的边沿,锁存器锁存的触发事件发生于使能端 ena 的电平。

当你成功实现了这个锁存器时,Quartus 会提醒(祝贺)你生成了一个锁存器。锁存器相比触发器会消耗更多的资源,所以综合器会在推断出锁存器时产生提醒,防止开发者在不想使用锁存器时,因为代码风格等原因误产生了锁存器。

解答与分析

module top_module (

input d,

input ena,

output reg q);

always@(*)begin

if(ena)begin

q<=d;

end

end

endmodule

产生锁存器的代码很简单,不是么?因为锁存器的触发事件不是时钟,所以只有在组合逻辑中才能产生锁存器,作者曾经还就锁存器做过一番探究:ljgibbs:Verilog 实验台(二):综合器,我想要一个锁存器

Problem 87 : DFF (Exams/m2014 q4b)

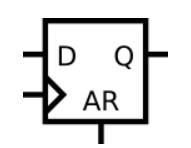

本题中需要实现一个如下的电路:

AR 代表 asynchronous reset,所以这是一个带有异步复位的 D 触发器,我们在先前的题目中讨论过异步复位的问题。

图中的三角形代表时钟,不再用 CLK 标出。

解答与分析

module top_module (

input clk,

input d,

input ar, // asynchronous reset

output reg q);

always@(posedge clk or posedge ar)begin

if(ar)begin

q <= 1'b0;

end else begin

q <= d;

end

end

endmodule

Problem 88 : DFF (Exams/m2014 q4c)

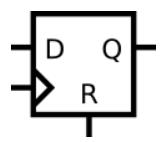

本题中需要实现一个如下的电路:

R 代表 synchronous reset,(就不用 SR 或者 SSR 表示了)所以这是一个带有同步复位的 D 触发器,我们在先前的题目中讨论过同步复位的问题。

解答与分析

module top_module (

input clk,

input d,

input r, // synchronous reset

output reg q);

always @(posedge clk) begin

if(r)

q <= 1'b0;

else

q <= d;

end

endmodule

Problem 89 : DFF+gate(Exams/m2014 q4d)

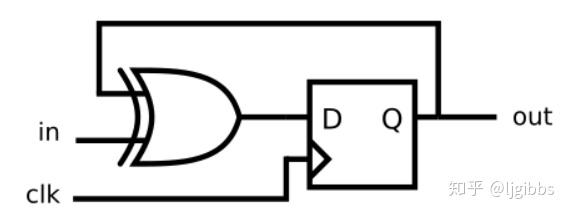

本题中需要实现一个如下的电路:

图中有一个 D 触发器与一个异或门,触发器的输出 q 和输入信号 in 一起作为异或门的输入。异或门的输入作为触发器的输入 d

解答与分析

module top_module (

input clk,

input in,

output reg out);

always @(posedge clk) begin

out <= in ^ out;

end

endmodule

在编写 Verilog 时,使用 ^ 符号抽象实现异或门。使用异或门的输出作为触发器的输入。

推荐阅读

- HDLBits:在线学习 Verilog (十七 · Problem 80-84)

- HDLBits:在线学习 Verilog (十六 · Problem 75 - 79)

- HDLBits:在线学习 Verilog (十五 · Problem 70 - 74)

- HDLBits:在线学习 Verilog (十四 · Problem 65-69)

- HDLBits:在线学习 Verilog (十三 · Problem 60-64)

关注此系列,请关注专栏FPGA的逻辑