使用OMI从内存、存储和IO中解耦合计算

目录

- OMI内存接口的容量和带宽优势

- POWER10的OMI& HBM支持、PowerAXON内存集群

- OCP的OAM-HPC新成员:价格有无吸引力?

- Shared Memory OMI Chiplet Buffer:以内存为中心计算?

OMI 内存接口的容量和带宽优势

在上一篇中,我已经写过AMD未来的EPYC服务器CPU与串行OMI(开放内存接口)之间的故事,今天沿着这个方向继续讨论。

点开可放大查看,以下同

本文图片部分引用自NALLASWAY的资料《Decoupling Compute from Memory,Storage & IO with OMI - An Open Source Hardware Initiative》。

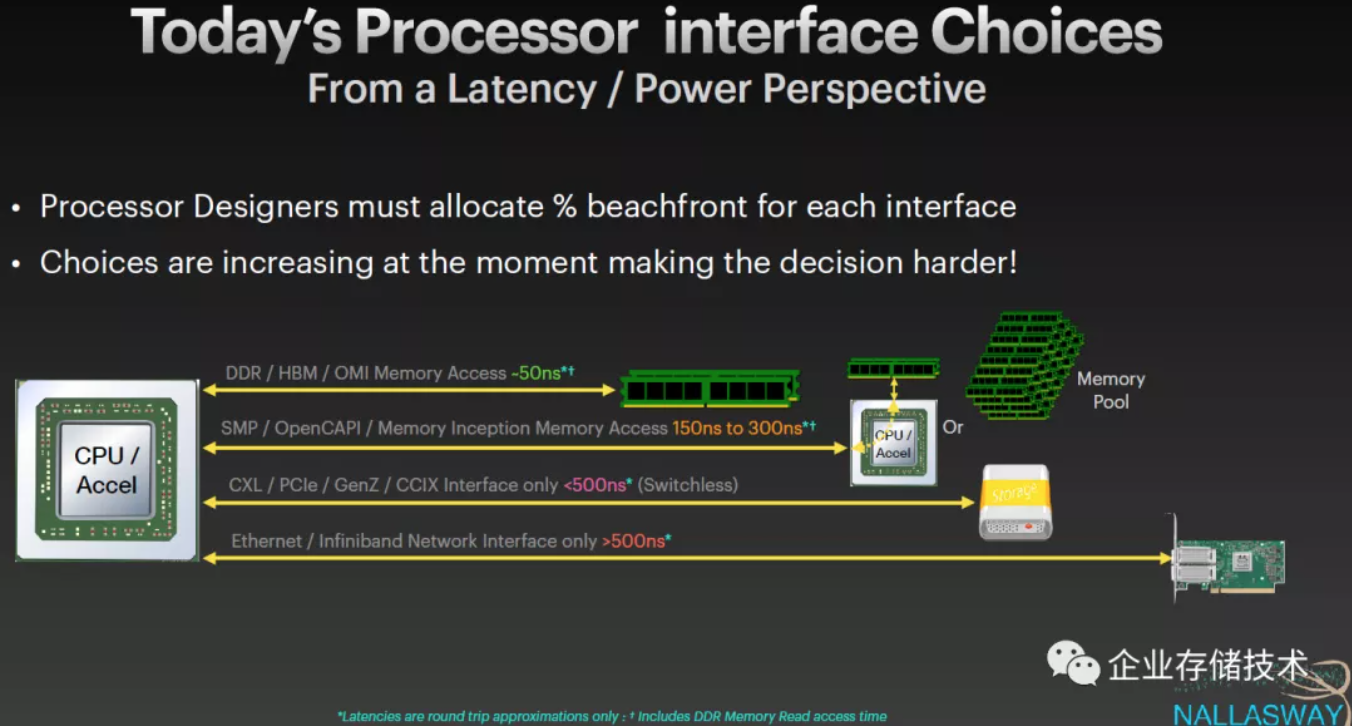

OMI内存接口与传统DDR、HBM同样属于50ns左右这个延时范围;如果是跨CPU(NUMA Node)/加速器(包括OpenCAPI连接)访问内存,延时可能会到150-300ns;而基于PCIe物理层的CXL内存一致性协议,如果不经过Switch交换芯片也能控制在500ns以内(我在《CXL、GenZ、CCIX架构以及未来的PM、内存和SSD形态》中提到是<350ns)。

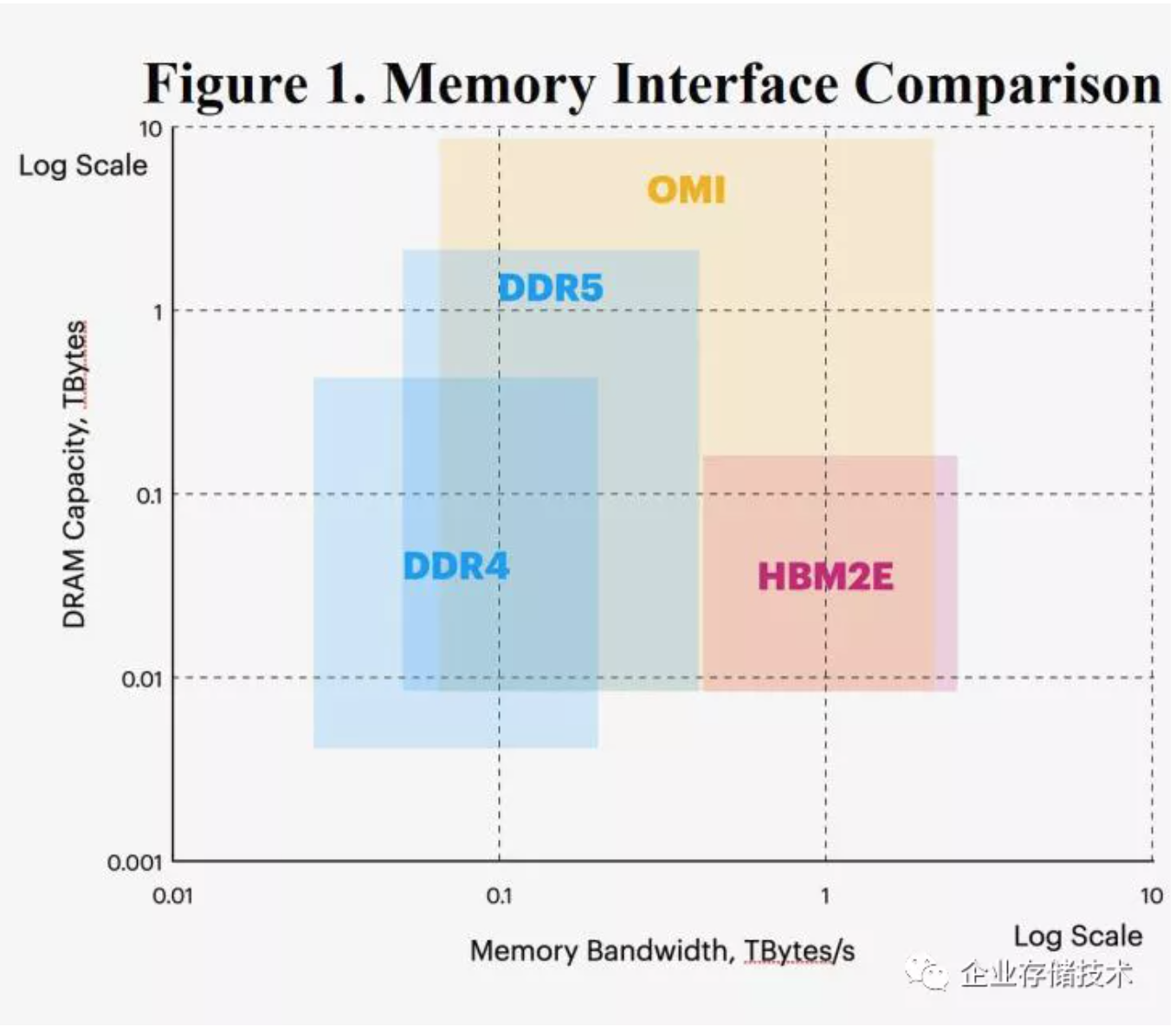

从某种角度来看,OMI(多通道)可以接近HBM2E的内存带宽性能,也能实现比传统DDR4/5 DIMM内存更高的容量。当然这里没有提成本,每个OMI内存模组上有一颗Buffer转接芯片,这个肯定要比CPU完全集成内存控制器要贵。我们以前只能在IBM POWER这样毛利润较高的服务器上看到OMI,Intel和AMD至少当前还没有。

为什么把OMI称为Shared Memory Interface(共享内存接口)呢?我想在本文结尾处告诉大家答案。

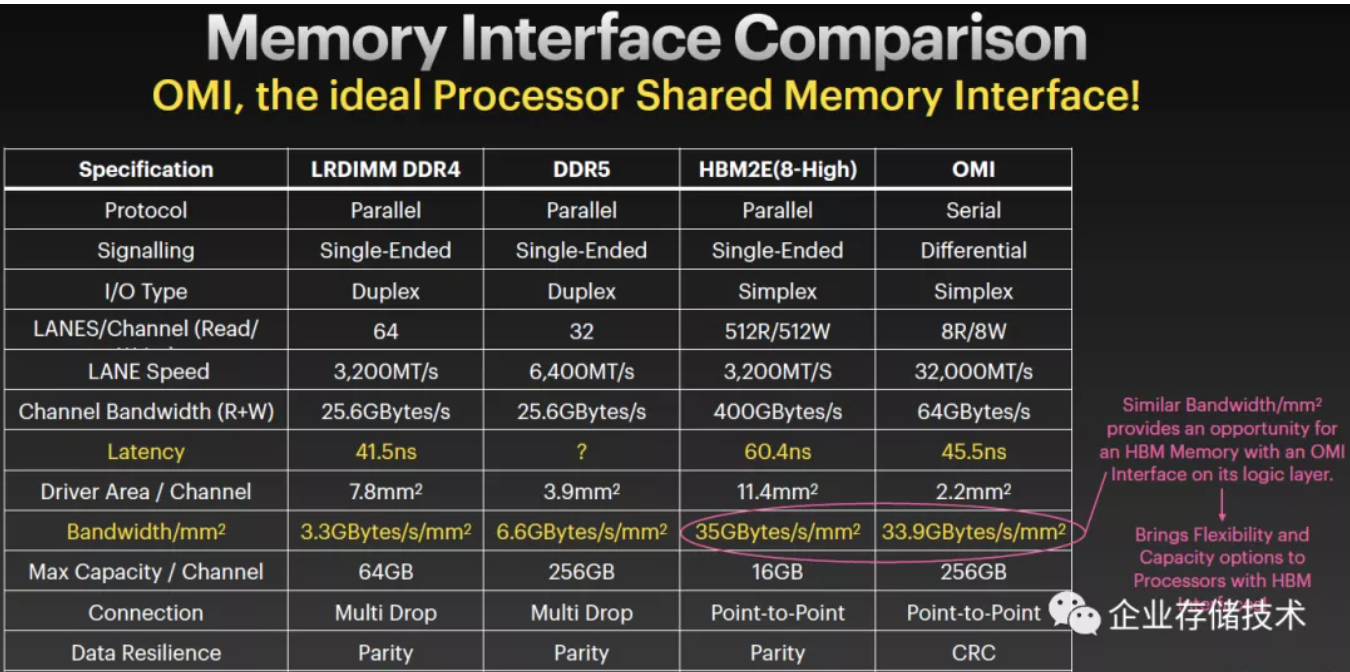

上面图表对比的这几种内存接口中,只有OMI是使用差分信号的串行协议,依靠LANE的速率来弥补传输位宽。HBM内存尽管带宽优秀,但较高的延时有人诟病,OMI在这方面与LRDIMM相对接近。尽管单通道带宽算不上惊人,但从单位芯片(内存控制器)面积所提供的带宽来看,OMI与HBM处于同一水平。因此右边的红字就提出在HBM的逻辑层上提供OMI接口的机会,这样就比传统的片上封装HBM增加了灵活性和容量选项。

最后一行,在数据恢复能力上,前几种内存接口都是支持奇偶校验(ECC);而OMI其实只是传输这块,所以只有CRC,具体的存储颗粒间校验在OMI模组上实现就好了。

POWER10的OMI& HBM支持、PowerAXON内存集群

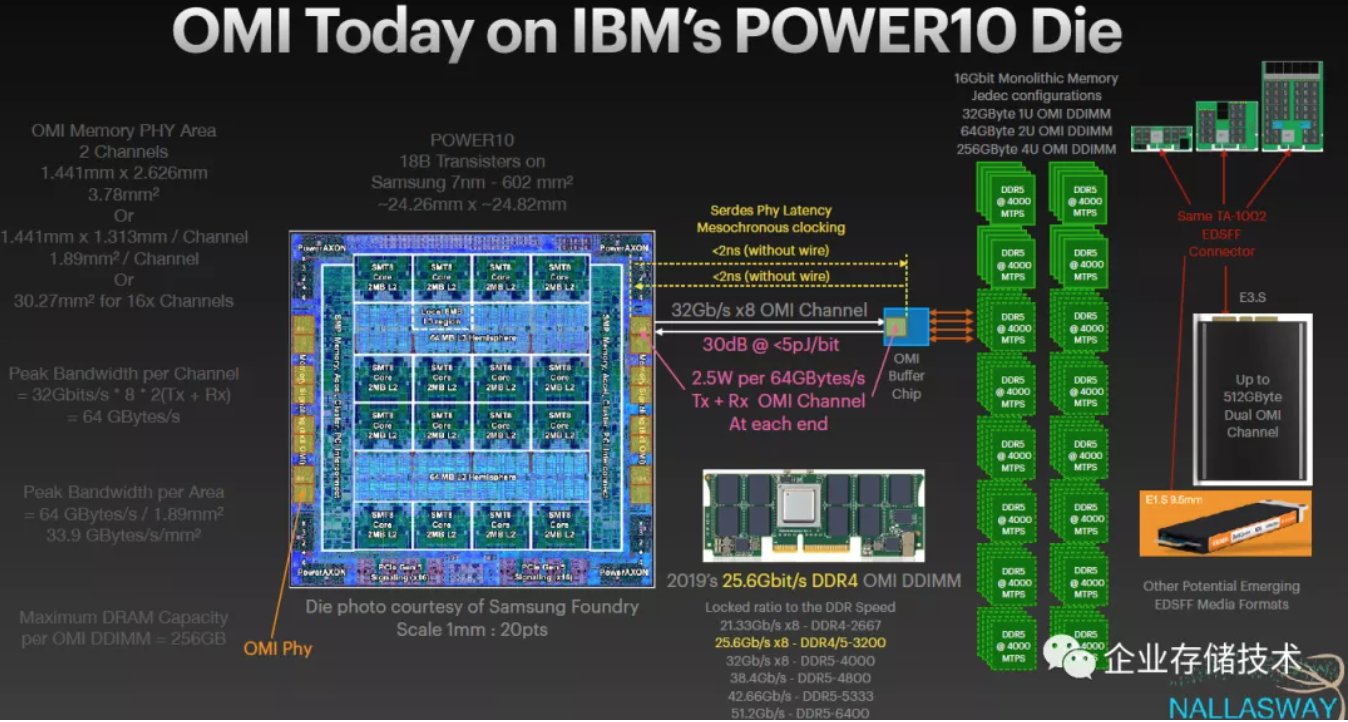

IBM从POWER9开始支持OMI,下面则是今天的POWER10 Die设计。

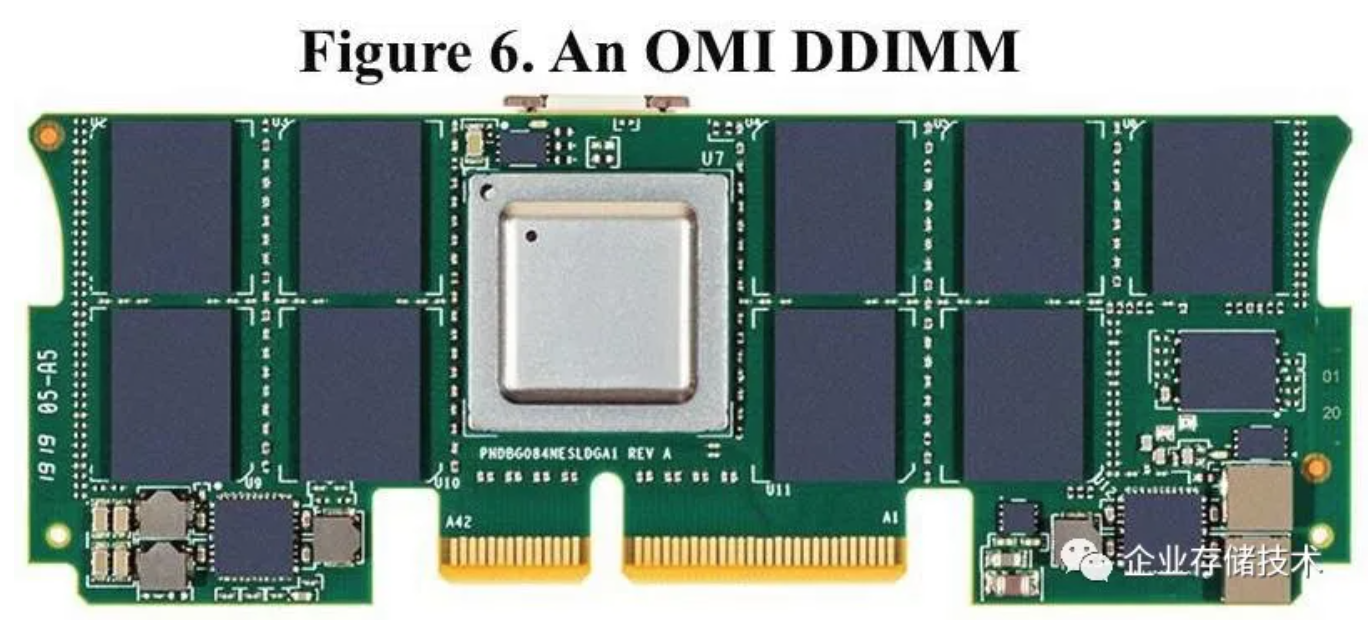

如图所示,从POWER10处理器的OMI Phy,到内存模组上OMI Buffer芯片之间的延时只有不到2ns(不算导线上的“光速”延时)。OMI模组形态上的发展方向我之前讲过,会从2019年的DDR4 DDIMM向EDSFF发展。

扩展阅读《数据中心NVMe SSD和EDSFF前瞻:来自Intel、HPE、Dell& SNIA等》

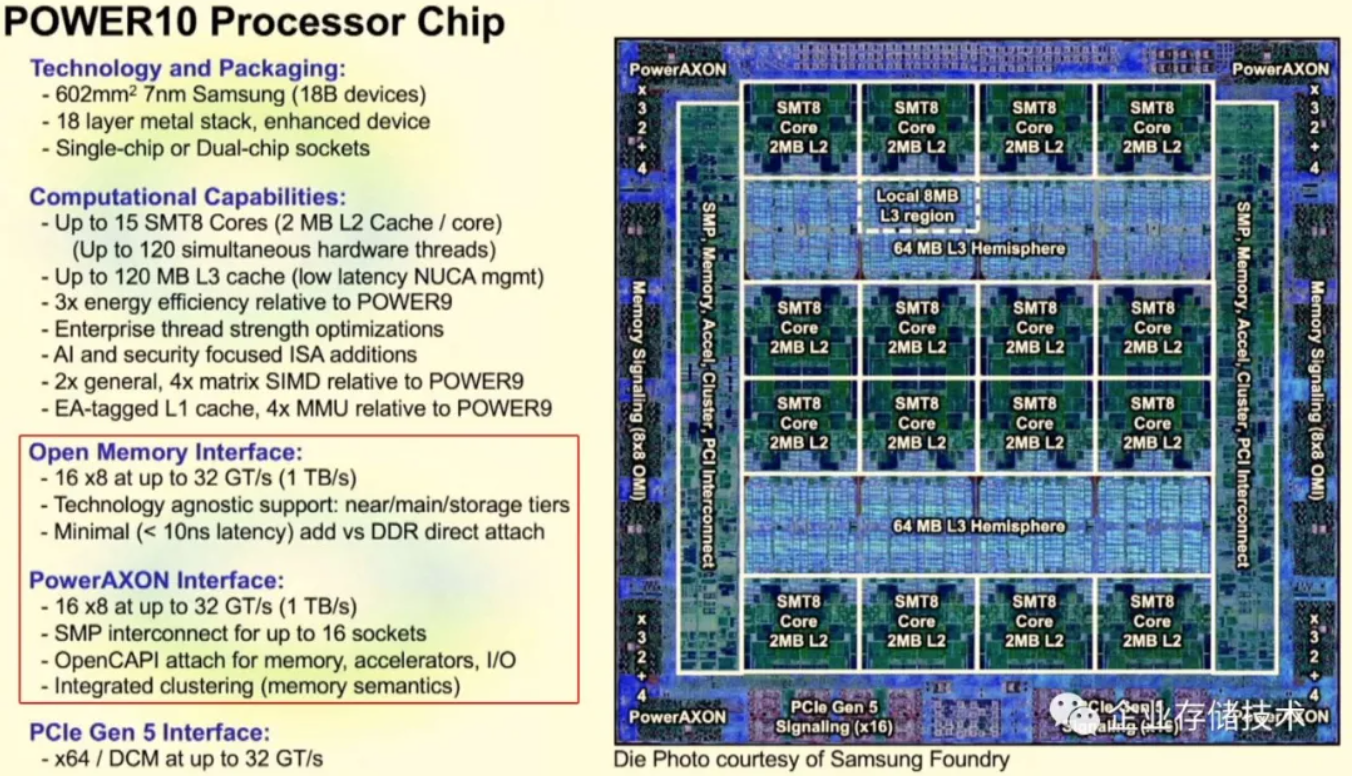

由于前面一张图的POWER10整体结构显示不清楚,所以我再列出几张IBM在去年Hot Chips 2020会议上分享的资料。像什么三星7nm工艺、PCIe Gen5接口我在这里先不研究,除了Open Memory Interface之外,下面也会带大家简单看一下PowerAXON高速互连。

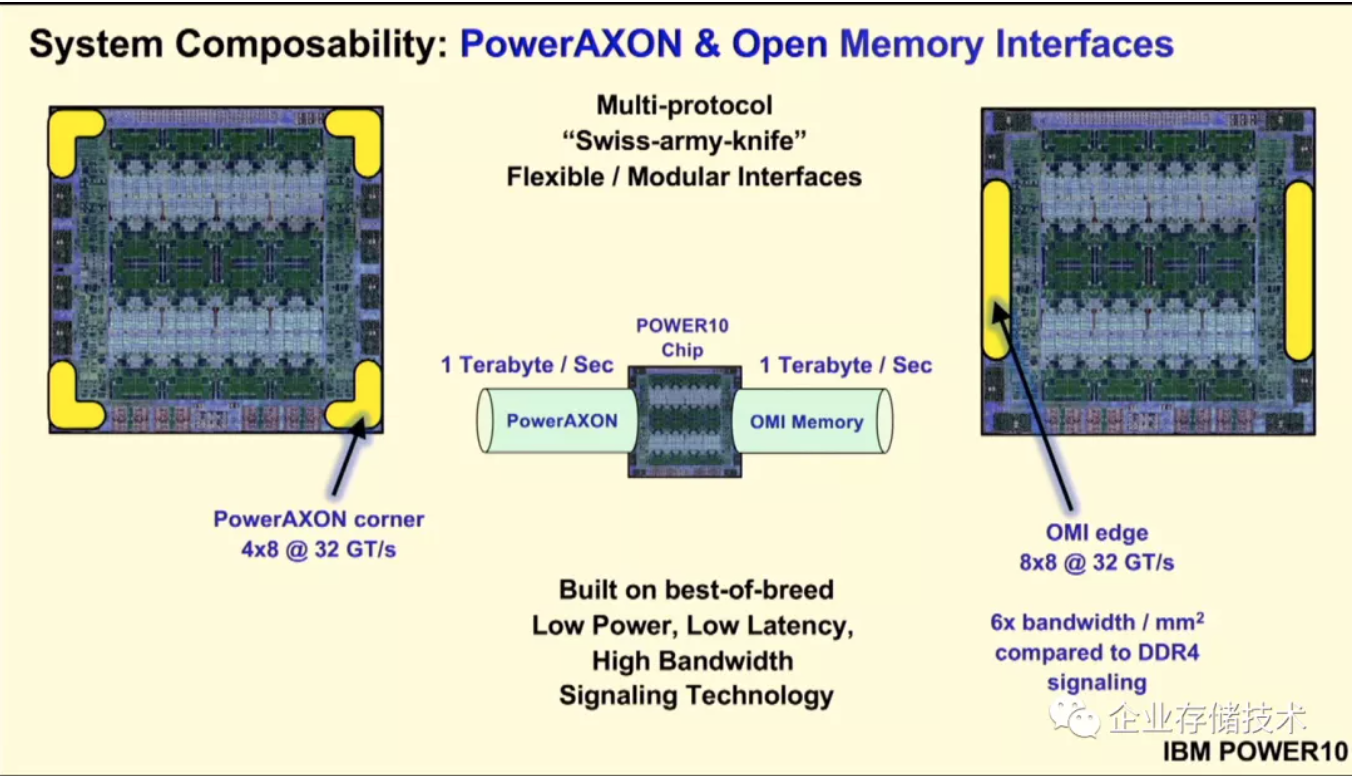

PowerAXON位于POWER10芯片的4个角,而OMI Phy位于左右两侧,它们的总带宽都能达到1TB/s。

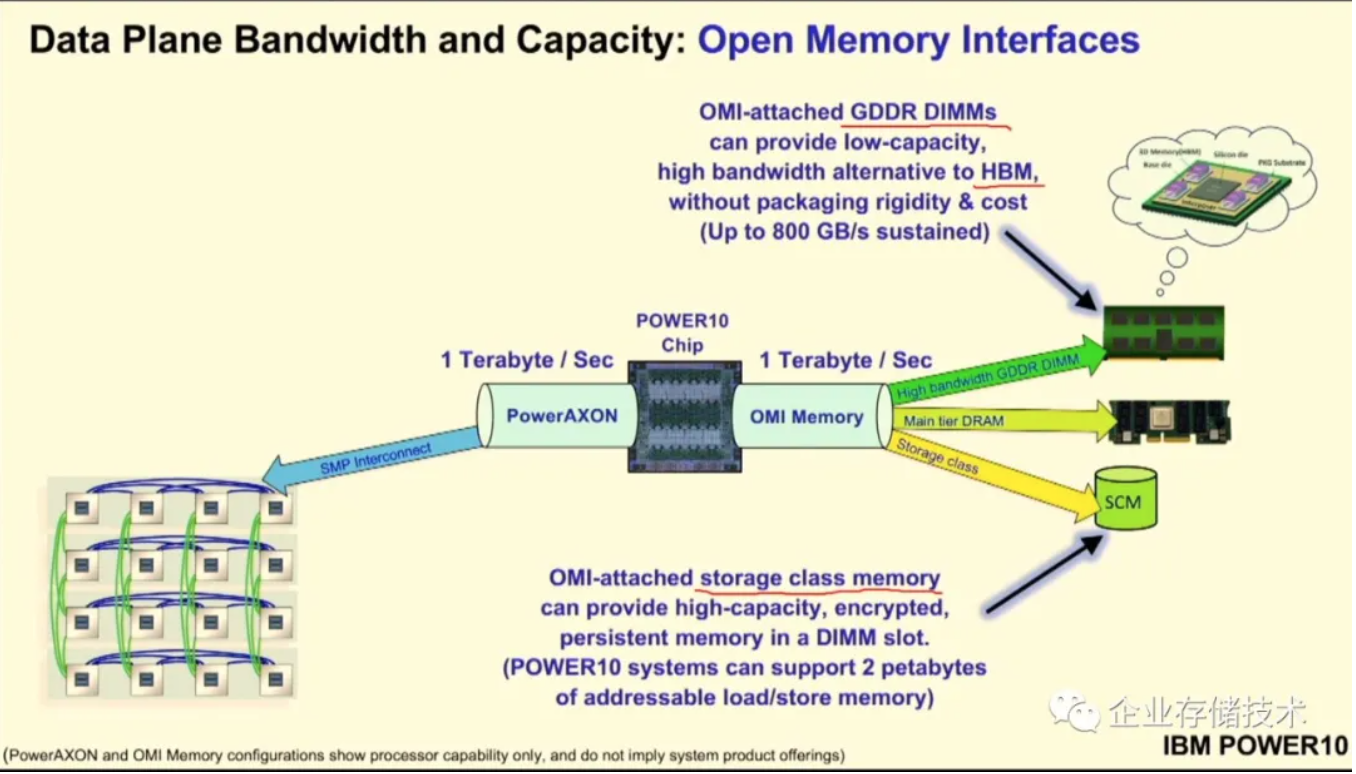

如上图,OMI接口除了用于连接DRAM主内存层之外还有2种用法。一种就是把HBM内存做成GDDR DIMM,不过此时应该要用多个OMI通道连接HBM模组才能匹配其高带宽;另一种是连接SCM(存储级内存),IBM好像没有提是基于Intel 3D XPoint还是具体哪种新型介质,我看在The Next Platform最近的文章中也只是称其为PRAM(持久内存,这里不是相变内存的缩写)。

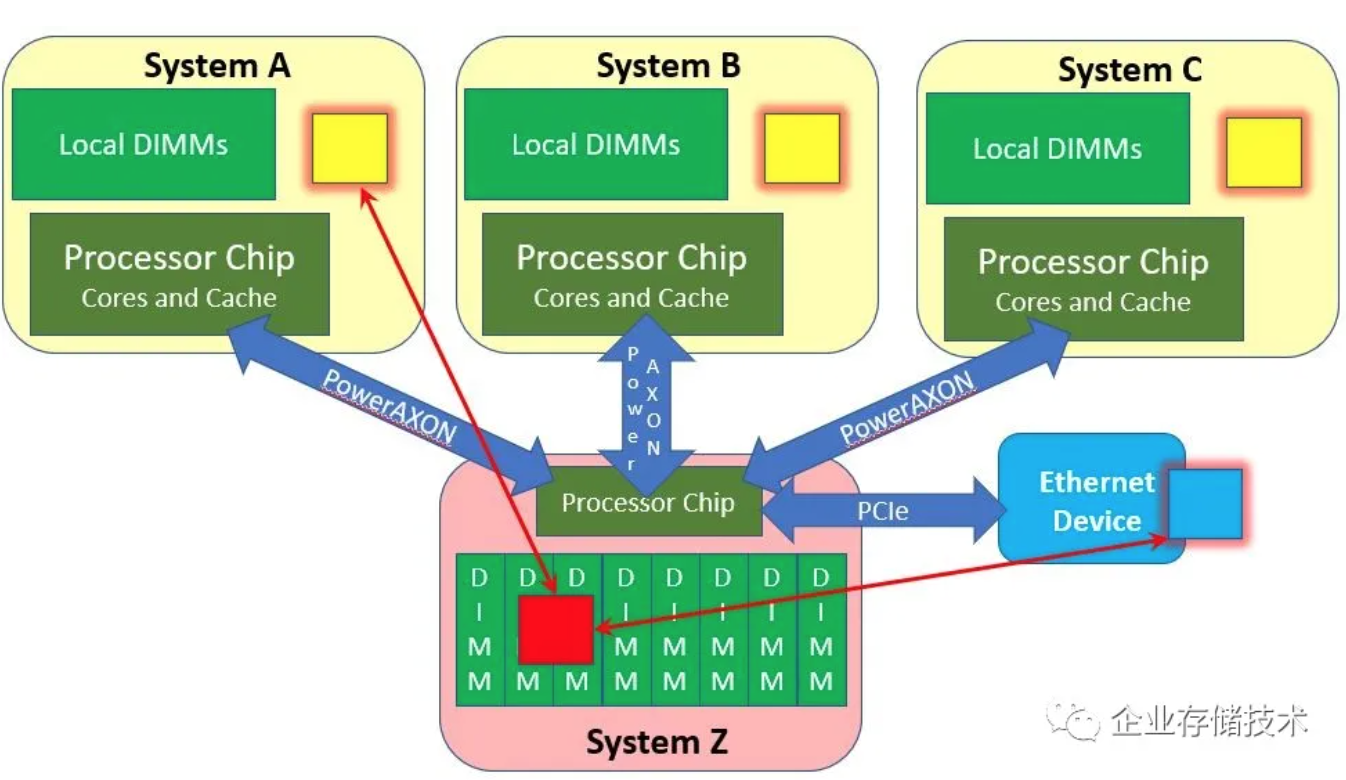

至于PowerAXON,除了可以用于单台服务器内部CPU间SMP连接之外,还可以跑OpenCAPI,或者组建多主机的大内存集群。

如上图,SystemA、B、C和Z(注意了,这里可不是指System z大型机)表示多台POWER10服务器,通过PowerAXON互连之后应该可以实现一致性内存访问。至于PCIe连接网卡的内存访问一致性,IBM看上去不在Intel主导的CXL Board of Directors里面,可能有别的技术来解决吧。

OCP的OAM-HPC新成员:POWER10价格有无吸引力?

IBM与Facebook的合作早在5年前我写《初探OpenPOWER9服务器设计:x86不再寂寞》时就已经有过。虽然OpenPOWER后来不知发展怎样,不过可以说是IBM率先推出PCIe 4.0、8通道内存控制器,还有集成PCH(南桥)这些设计,后来在AMD大获成功的EPYC上也都看到了。一方面赶上Intel前两年有些落后,另外POWER不像AMD那样兼容x86指令集,所以规模也不容易上去。

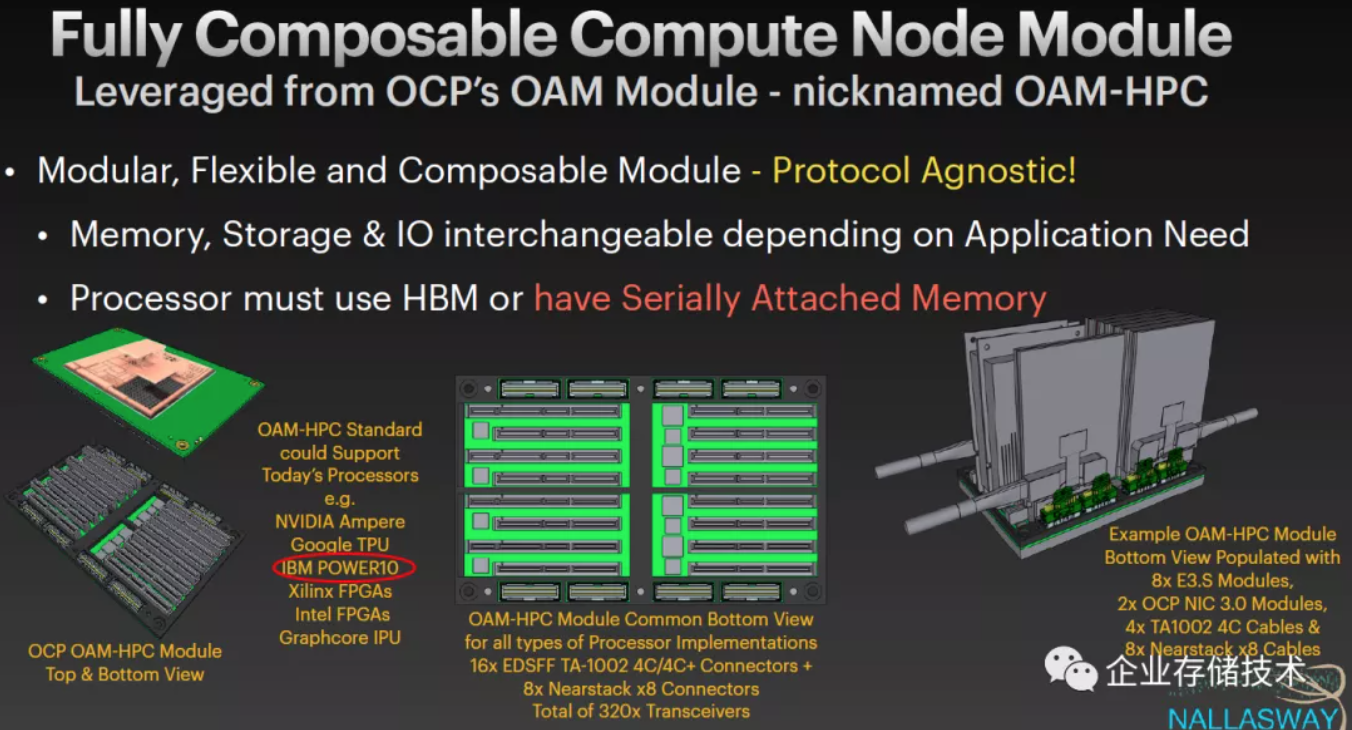

完全可组合的计算节点模块

在之前的文章中,我写过AMD EPYC可能会出现在OCP组织的OAM模块上,看来IBM POWER10也要加入这一阵营。

OCP OAM只定义了物理部分也就是协议无关的,但处理器必须使用HBM(片上内存)或者串行连接内存,毕竟OAM上没有插DIMM内存条的地方。与AMD和IBM不同的是,Intel估计会想把针对HPC的Xe协处理加速器放在OAM上,Xeon CPU暂时没有看到兼容OAM。不过现在有EDSFF接口的CXL DDR5内存模组,如果未来Intel支持只使用CXL主内存(而不插DIMM)的话,技术上也是有可能的。

IBM POWER10与AMD EPYC相比的一个劣势,可能是性价比。我们知道OCP面对的用户群大多在乎这个,而且CPU又不是像NVIDIA GPU那样不太有竞争的产品。

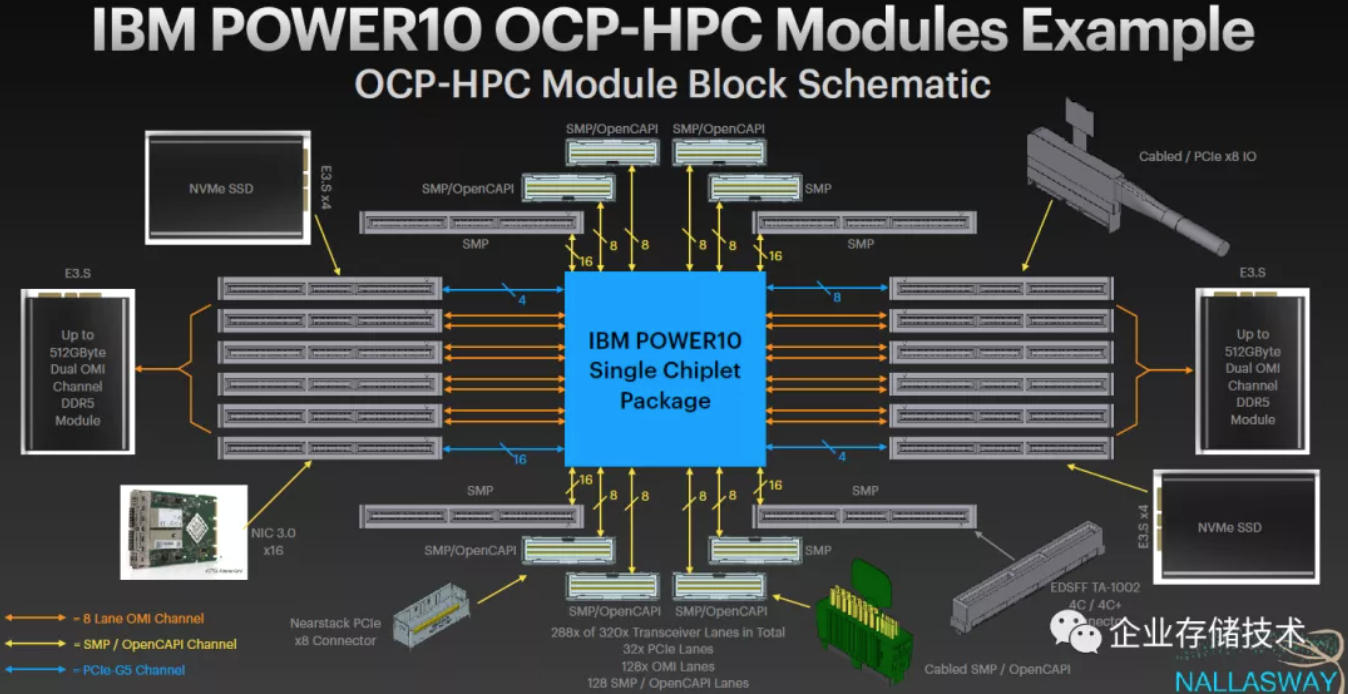

IBM POWER10 OCP-HPC模块示例

POWER10在这里被称为“单Chiplet封装”。我看EDSFF 3英寸的双OMI通道DDR5内存模组,与E3.S的CXL内存模组、NVMe SSD外型上都长得差不多。

Shared Memory OMI Chiplet Buffer:以内存为中心计算?

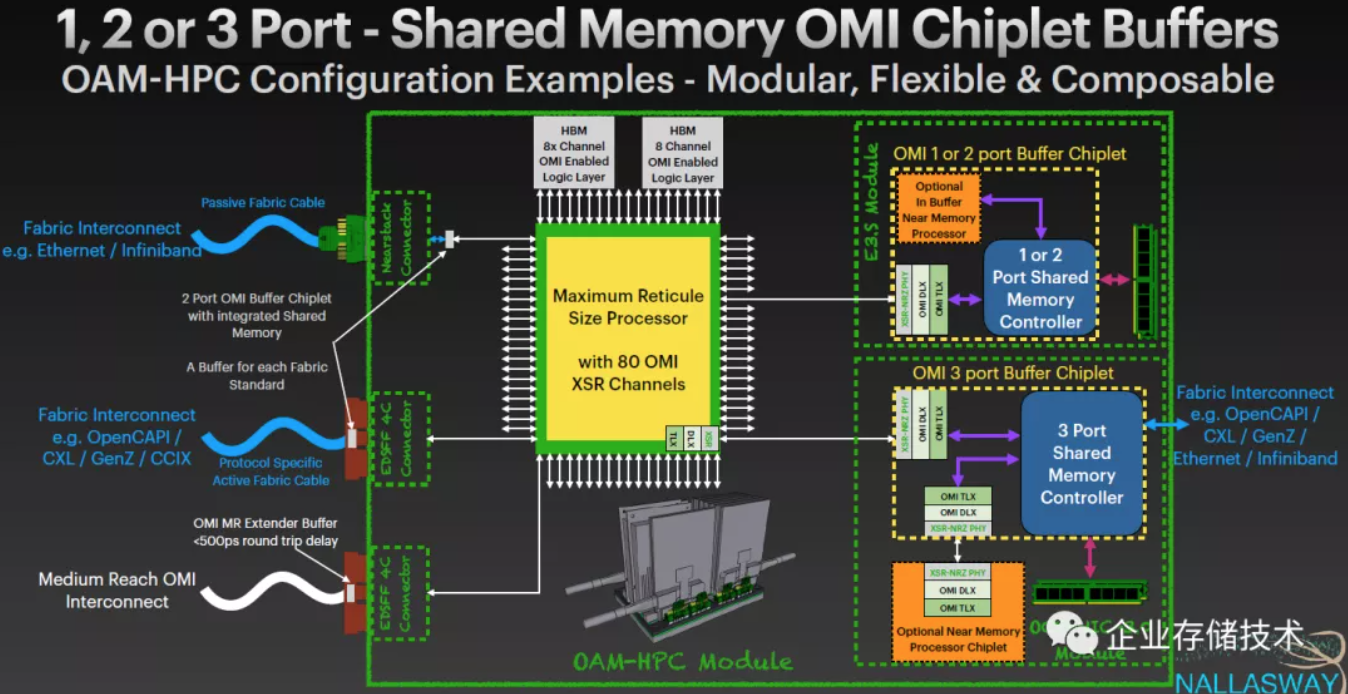

传统的OMI Buffer芯片与CPU之间都是1对1的连接,而上图中的玩法有点意思——支持2-3个端口共享内存的OMI Chiplet Buffers。

具体实现上,比如2端口还是做成E3.S模块,在OMI Buffer芯片上加一个In Buffer Near Memory近内存处理器Die,这样Share Memory Controller控制的DRAM就同时连接到CPU和这个片上处理器。是不是有点存内计算的样子?

OMI 3port Buffer Chiplet则要改用OCP NIC 3.0模块了,因为它增加的第三个共享内存port是Fabric外部网络接口,如OpenCAPI / CXL / Gen-Z / 以太网/ InfiniBand。这样多台服务器的内存之间可以(不经过CPU)直接互连了,未来会发展成以内存为中心计算的非冯诺依曼结构吗?

有点扯远了,上面最后一句是瞎写的,我的技术水平还不够讨论计算机体系结构:)

参考资料:

《ThePower Of Power10’s Memory Inception Clustering》

https://www.nextplatform.com/...

《HotChips 2020 Live Blog: IBM's POWER10 Processor on Samsung 7nm (10:00am PT)》

https://www.anandtech.com/sho...

《DecouplingCompute from Memory, Storage & IO with OMI》,NALLASWAY

结尾处加一个读者调查。看《企业存储技术》时间长的朋友,应该注意到我一般会把文中引用、参考的技术资料以网盘等方式分享出来。不知是不是这个原因,有的同行朋友可能觉得我只是做了一个翻译的事情?我自知无论技术水平、还是英文都无法与许多专家、大牛们相比,以前把相关资料尽量共享给大家,只是觉得我的认识和解读都还有限,希望能给读者朋友进一步的参考和帮助。当然,这样一来自己也就没保留啥“私货”,相当于做公益了吧。今天也想听听大家的反馈建议:

更多意见和建议,欢迎在下面留言或者私信我。谢谢!

作者:唐僧huangliang

原文:https://mp.weixin.qq.com/s/258pPMR-REyCvHI-R-tCiQ

推荐阅读

欢迎关注企业存储技术极术专栏