PHY Interface For the PCI Express, SATA, and USB 3.1 Architectures

Version 4.3

©2007 - 2014 Intel Corporation—All rights reserved.

7.6 Changing Signaling Rate, PCLK Rate, or Data Bus Width

7.6.1 PCI Express Mode

PCIe 速率、PCLK 频率以及数据总线位宽三项配置的调整,仅能够在 PHY 处于 P0 或者 P1 电源状态,以及 TxElecIdle 和 RxStandby 信号置起的情况下进行。上述三项参数中的任意两项的组合可以被同时调整,但是 MAC 不允许只调整其中仅仅一项。(译注:这种情况实际上是做不到的,另外从协议来看,三项参数同时调整也是不可行的)

在 PCLK as PHY Output 模式下,当 MAC 调整三项配置(PCIe 速率、PCLK 频率以及数据总线位宽)中的两项时,PHY 在完成配置更新后,置起一个周期的 PhyStatus 表示更新完成。MAC 在 PHY 通过 PhyStatus 表示本次配置更新完成前,不能够进行后续的操作,包括电源状态转换,置低 TxElecIdle 和 RxStandby 信号,或者开始下一次配置更新。

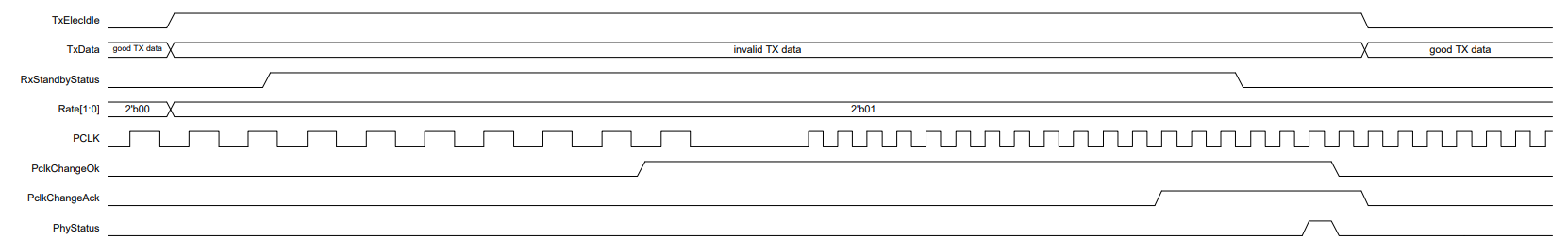

在 PCLK as PHY Input 模式下,配置更新的过程和前一模式相同,唯一的区别在于,MAC 需要知道何时输入 PCLK 时钟频率可以被安全地调整。MAC 只能够在 PHY 置高 PclkChangeOk 信号后,才能调整 PCLK\_Rate 信号和 PCLK 时钟信号频率。

MAC 调整 PCLK 频率后,置起 PclkChangeAck 信号与 PHY 进行握手。PHY 通过置起 PhyStatus 信号一个周期表示收到 MAC 发出的握手信号,随后在 PhyStatus 下降沿置低 PclkChangeOk 信号。注意,PHY 仅在 MAC 调整 PCLK_Rate 时,使用 PclkChangeOk 信号。

MAC 在采样到 PHY 发出的 PclkChangeOk 信号后,置低 PclkChangeAck 信号完成握手。在采样到 PHY 发出的 PhyStatus 高电平后,MAC 也有可能置低 TxElecIdle 和 RxStandby 信号。

随着 LTSSM 状态变化,在几种情况中,PHY 的 PCIe 速率、PCLK 频率、数据总线位宽以及电源状态可能都需要发生变化。一种情况是,LTSSM 转移至 Detect 状态,PHY 在将电源状态从 P0 切换到 P1 之前,(如果需要的话)MAC 必须将速率切换至 2.5 GT/s ,因此需要改变 PCLK 频率或者数据位宽。

另一种情况是,LTSSM 转移至 L2.Idle 状态,PHY 在将电源状态从 P0 切换到 P2 之前,(如果需要的话)同样需要将速率调整到 2.5 GT/s,此时 PHY 的 PCIe 速率、PCLK 频率、数据总线位宽以及电源状态可能都需要发生变化。

一些 PHY 架构可能允许同时改变链路速率以及 PHY 电源状态,涉及到 PCIe 速率、PCLK 频率以及数据总线位宽三项配置的调整。如果 PHY 支持这项特性,那么 MAC 必须在同一个 PCLK 边沿同时调整 PowerDown 信号和 PCLK 频率或者数据总线位宽信号。这种情况可能在 PHY 从 P0 到 P1 或者 P2 的状态改变中发生,电源状态的机制和 7.3 节的描述一致,但此时的完整信号不仅表示电源状态切换完成,也表示PCIe 速率、PCLK 频率或者数据总线位宽调整完成。

7.6.2 USB Mode

翻译暂略

7.6.3 SATA Mode

翻译暂略

7.6.4 Fixed data path implementations

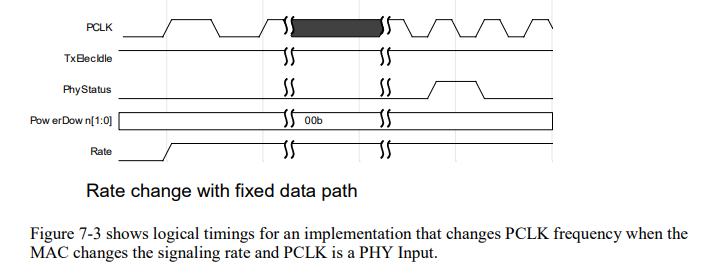

下图展示了 PCLK is a PHY Output 模式下,MAC 通过改变 PCLK ,从而改变速率的信号时序图。

实现通过 PCLK 频率改变,以改变链路速率时,必须在时钟停止后改变 PCLK 频率(如果 PCLK 支持停止的话),以防止使用 PCLK 的计时器溢出。

(译注:原文有些奇怪:Implementations that change the PCLK frequency when changing signaling rates must change the clock such that the time the clock is stopped (if it is stopped) is minimized to prevent any timers using PCLK from exceeding their specifications.)

并且,在 PCLK 频率切换期间,需要保证 PCLK 频率不超过 PHY 支持的最高 PCLK 频率。

从 Rate 信号置起,到 PCLK 频率变化完成的时间间隔,取决于 PHY 的设计实现。这项时序参数会用于置低 TxDataValid 和 RxDataValid 信号,用于在 PCLK 切换期间,停止数据通路传输。

图 7-3a PCLK is a PHY Output 模式下,MAC 通过改变 PCLK ,从而改变速率的信号时序图。(译注:原文图注为 PHY Input mode,但译者觉得这应该是 PHY Output mode 的时序图)

图 7-3b PCLK is a PHY Input 模式下,PCIe 速率从 2.5 Gt/s 变换到 5 Gt/s 信号时序图。

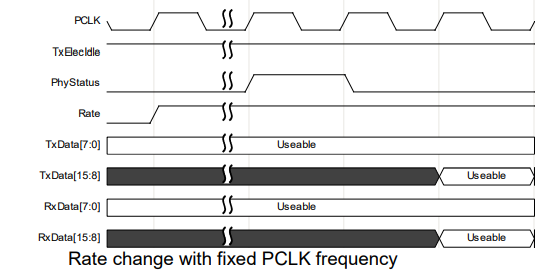

7.6.5 Fixed PCLK implementations

下图展示了 MAC 通过改变有效数据位宽 ,从而改变速率的信号时序图。PCLK 可以在速率变换期间停止。下图中的时序关系,同样可以应用于采用 TxDataValid 和 RxDataValid 信号指示位宽变化的 PCLK 固定速率变换方案。

图 7-4 MAC 固定 PCLK 频率,通过改变数据位宽,从而改变速率的信号时序图。

7.7 Transmitter Margining – PCI Express Mode and USB Mode

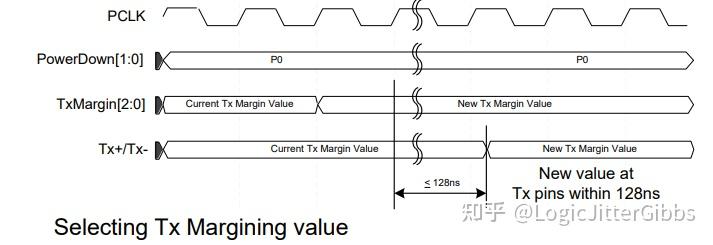

P0 电源状态下,PHY 可以被 MAC 控制改变发送引脚电压。当 MAC 改变其发送的 TxMargin[2:0] 信号时,PHY 必须能在 128ns 内使用新的电压设置发送信号。

MAC 可以选择的 TxMargin[2:0] 数值和链路速率的选择是有限制的,PCIe 和 USB 模式下的具体可选组合参考两者的协议文本。

图 7-7-1 TX Margin 值变化时序图

7.8 Selectable De-emphasis – PCI Express Mode

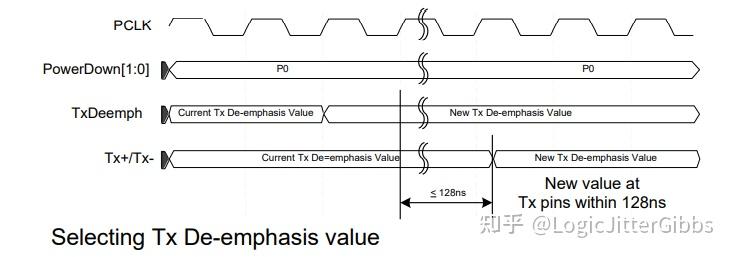

P0 电源状态下,链路速率 5.0GT/s 或者 8.0 GT/s 时,PHY 可以被 MAC 控制改变发送端均衡设置。当 MAC 改变其发送的 TxDeemph 信号时,5.0 GT/s 速率下,PHY 必须能在 128ns 内使用新的电压设置发送信号。而 8.0 GT/s 速率下,PHY 必须能在 256ns 内使用新的电压设置发送信号.

MAC 可以选择的 TxDeemph 数值和链路速率的选择是有限制的,PCIe 模式下的具体可选组合参考协议文本。

在 2.5 GT/s 速率时,MAC 需要保证 TxDeemph 选择 -3.5db 。

图 7-8-1 TxDeemph 值变化时序图

7.9 Receiver Detection – PCI Express Mode and USB Mode

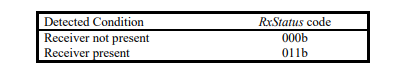

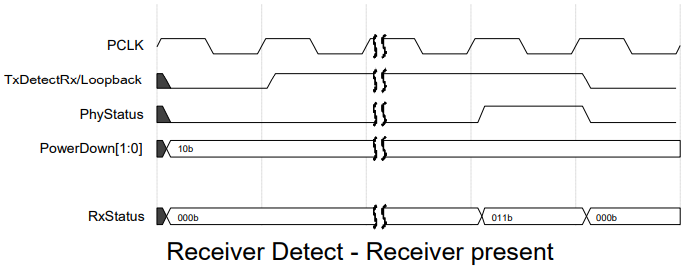

在 PCIe 的 P1 状态和 USB 的 P2、P3 状态中,PHY 能够被 MAC 指示开始接收侦测行为,来探测在链路对端是否有设备。

接收检测中的基本流程是 MAC 通过置高 TxDetectRx/Loopback 信号,要求 PHY 开始接收检测。在 PHY 完成一次接收检测后,置高 PhyStatus 一个周期,并将 RxStatus 信号的值更新为接收检测的结果。

在一次接收检测结束后,PHY 置高 PhyStatus 一个周期,MAC 需要首先置低 TxDetectRx/Loopback,才能开始下一次接收检测,或者其他操作,比如电源状态或者速率转换。

一旦 MAC 发出接收检测的请求后(通过置高 TxDetectRx/Loopback 信号),MAC 必须保持 TxDetectRx/Loopback 信号为高,直到 PHY 完成本次接收检测,置高 PhyStatus 信号为止。

在 USB 模式 PHY P3 电源状态下,完成接收检测后,PHY 置高 PhyStatus 信号,并把检测结果更新到 RxStatus ,一直保持两个信号,直至 MAC 置低 TxDetectRx/Loopback 信号。(译注: USB 模式支持 P3 模式下的接收检测,P3 模式没有 PCLK,所以 PhyStatus 会一直置高,而不是只是持续一个周期)

图 7-9-1 P1,P2 模式下接收检测时序图

7.10 Transmitting a beacon – PCI Express Mode

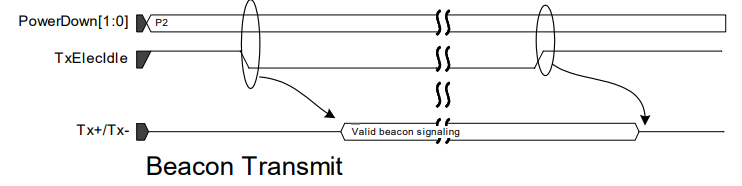

当 PHY 被置于 P2 电源状态后,且 MAC 希望发送一个 beacon 信号,MAC 需要置低 TxElecidle,此后 PHY 应该持续产生有效的 beacon 信号,直至 TxElecidle 信号被置起。而在 PHY 返回 P0 状态之前,MAC 必须将 TxElecidle 信号置起。

图 7-10-1 P2 状态下 PHY 发送 Beacon 信号

7.11 Transmitting LFPS – USB Mode

翻译暂略

7.12 Detecting a beacon – PCI Express Mode

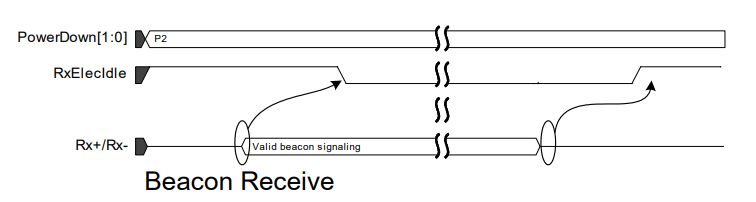

PHY 接收机应当时钟检测线路上的电气空闲状态,除了 PHY 被复位期间。PHY 处于 P2 状态时,当 PHY 置低 RxElecIdle 信号时,代表接收机检测到了线路上发送的 beacon 信号。

图 7-12-1 P2 状态下 PHY 检测到 Beacon 信号,并置低 RxElecIdle 信号

原文: Mindshare

译者: Michael ZZY

校对: LJGibbs

文章来源:https://zhuanlan.zhihu.com/p/511752677

《PCI Express Technology 3.0》翻译系列

- PHY Interface :7 PIPE Operational Behavior 7.1-7.5

- PHY Interface :3 PHY/MAC interface & 4

- PHY Interface 协议翻译: 2 Introduction

- PCI Express Technology 3.0 Chapter 6 流量控制 5-7 节

- PCI Express Technology 3.0:Chapter 6 流量控制 1-4 节

- 《PCI Express Technology 3.0 》Chapter 5 第3 节

- 《PCI Express Technology 3.0》Chapter 5

- PCI Express Technology 3.0:Chapter 1 Background/背景

- PCI Express Technology 3.0:PCIe体系结构概述 2.1 节

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3

更多IC设计技术干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。