译注:本篇译文为 Polling 状态节,但其中欠 Polling.Compliance 次状态的细节部分。这是因为笔者不是很熟悉编码部分,翻译地不太顺利,所以我打算先接着往后翻译,再回头补上这部分。

14.5 Polling State // 轮询状态

14.5.1 简介

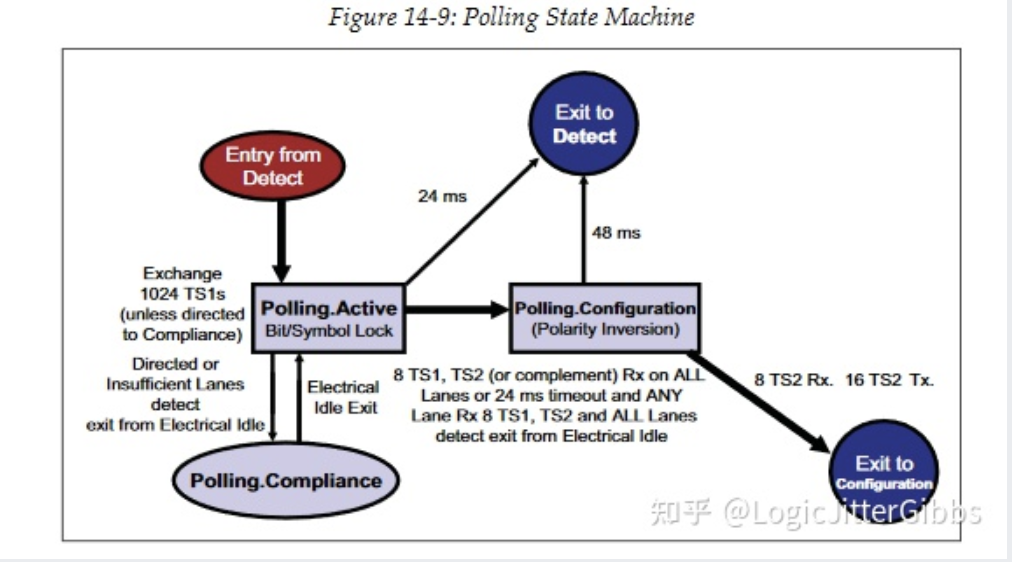

LTSSM 进入轮询状态时,链路处于电气空闲状态,不过,轮询状态期间会在链路两端之间交换 TS1 和 TS2 有序集。轮询状态的主要目的是使链路两端的设备能够听懂对方在说些什么,换句话说,他们需要各自在对方的发送比特流上,建立比特和符号锁定状态,并且解决极性翻转(polarity inversion)恢复之类的事宜。在这些工作完成后,设备们能够正确地接收对方发出的 TS1 和 TS2 有序集。图 14-9 展示了轮询状态的各个子状态。

图 14-9 轮询状态机

14.5.1 Polling子状态细节讨论

14.5.1.1 Polling.Active

Polling.Active 期间

一旦链路双方的共模电压稳定在发送余量(Transmit Margin)域中允许的范围内之后,发送方会发送至少 1024 个连续的 TS1 有序集。因为链路双方退出检测状态的时刻可能不同,所以 TS1 命令序列的交换不是同步的。在 Gen1(2.5GT/s) 速率下,发送 1024 个 TS1 序列花费 64us 。

Active 次状态下,有一些值得注意的细节:

- 必须在 TS1 序列的通道(Lane)和链路编号(Link number)字段中使用填充字符

- 设备需要通告(advertise)自己支持的所有速率,哪怕设备并不打算使用这些速率

- 接收方使用接收到的 TS1 序列实现比特锁定和符号锁定(低于 8GT/s 的速率)或者块锁定(8GT/s 速率)

退出状态进入 Polling.Configuration

在发送方发送完 1024 个 TS1 里最后一个 TS1 序列之后,如果所有检测到的通道都收到了 8 个连续的训练序列(如果存在极性翻转的话,那么收到的就是训练序列的补集),并且这些训练序列满足以下条件之一的话,状态机进入 Polling.Configuration 状态:

- 接收到的 TS1 的链路和通道字段全部被设置为全填充字符(PAD),并且 Compliance Receive 比特设置为 0b (符号 5 的 比特 4)

- 接收到的 TS1 的链路和通道字段都被设置为全填充字符,并且 Loopback 比特设置为 1b (符号 5 的 比特 2)

- 接收到的 TS2 的链路和通道字段都被设置为全填充字符

如果上述条件都没能满足,那么在 24ms 的超时之后,在接收到某个 TS1 之后,已经发送了 1024 个 TS1 序列,只需要任意检测到的通道接收到了 8 个连续的TS1 序列或者 TS2 序列,通道以及链路编号是填充符号,并且满足以下条件之一(译注:其实以下条件和超时前的判断条件一致),那么状态机进入 Polling.Configuration 状态。

- 接收到的 TS1 的链路和通道字段全部被设置为全填充字符(PAD),并且 Compliance Receive 比特设置为 0b (符号 5 的 比特 4)

- 接收到的 TS1 的链路和通道字段都被设置为全填充字符,并且 Loopback 比特设置为 0b (符号 5 的 比特 2)

- 接收到的 TS2 的链路和通道字段都被设置为全填充字符

如果在任意通道上都没有满足上述条件的情况出现,那么如果自进入 Polling.Active 状态以来,有超过预定数量的通道上检测到至少一次退出电气空闲的现象(这是为了防止一个或者多个失效的发送端或者接收端导致链路不能能进行配置),那么也能进入 Polling.Configuration 状态。(译注:原文此处后半句缺失,译文为译者所加)此处提到的预定数量由具体实现决定,此处相较于 1.1 版本的协议做了改动,原先必须检测到所有通道都退出电气空闲。

退出状态进入 Polling.Compliance

如果 Link Control 2 寄存器中的 “Enter Compliance” 比特被设置为 1,那么进入 Polling.Compliance。或者如果在进入 Polling.Active 状态之前,该比特已经被置位,那么将直接从 Active 状态进入 Compliance 状态,不会在 Active 状态中发送任何 TS1 序列。

否则,等待 24ms 后,再次判断进入 Compliance 状态的条件:

- 所有的通道在进入 Active 状态后,都没有检测到对端退出电气空闲状态。(这意味着对端是一个被动测试负载,比如在至少一个通道上挂载了一个测试电阻,将强制使所有通道进入 Compliance 状态。)

- 接收到 8 个连续的 TS1 ,其链路和通道字段全部被设置为全填充字符(PAD),并且 Compliance Receive 比特设置为 1b (符号 5 的 比特 4),并且 Loopback 比特设置为 0b (符号 5 的 比特 2)。

退出状态进入 Detect State

如果在 24ms 之后,没有满足进入 Polling.Configuration 状态或者 Polling.Compliance 状态的条件,那么返回 Detect 状态。

14.5.1.2 Polling.Configuration

在 Configuration 次状态中,发送方停止发送 TS1 序列,转而发送 TS2 序列,TS2 序列中的链路和通道(lane)字段仍然使用填充字段填充。该状态中,发送方转而发送 TS2 的目的是通知链路对端的设备:本方已经做好准备进入状态机中的下一个状态。转而发送 TS2 是为了使链路两端的设备 LTSSM 同步而设计的握手机制。双方设备都无法独自进入下一状态,除非链路两端的设备都准备就绪。开始发送 TS2 序列是通知对端本方准备就绪的方式。所以一旦设备同时发送并且接收到 TS2 序列,就代表本方和对端设备都已经就绪, 设备可以进入下一状态。

Polling.Configuration 期间

发送方在所有识别的通道上发送 TS2 序列,其链路和通道字段使用填充字段填充。并且发送方必须通知对端自己所支持的所有数据速率,即使是那些不打算使用的数据速率。此外,如果有需要的话,每个通道的接收方必须独立地恢复差分输入信号的极性。关于极性恢复的具体内容,可以参见原文 506 的概览章。另外,Transmit Margin 字段必须重置为 000b。

退出状态进入 Configuration 状态

在任意通道上接收到 8 个连续的链路和通道(lane)字段填充的 TS2 序列后,并且从接收到第一个 TS2 序列开始,已经发送了至少 16 个 TS2 序列后,退出 Polling.Configuration 状态进入 Configuration 状态。

退出状态进入 Detect 状态

如果上述条件在 48 ms 的超时后仍未满足,退出 Polling.Configuration 状态进入 Detect 状态。

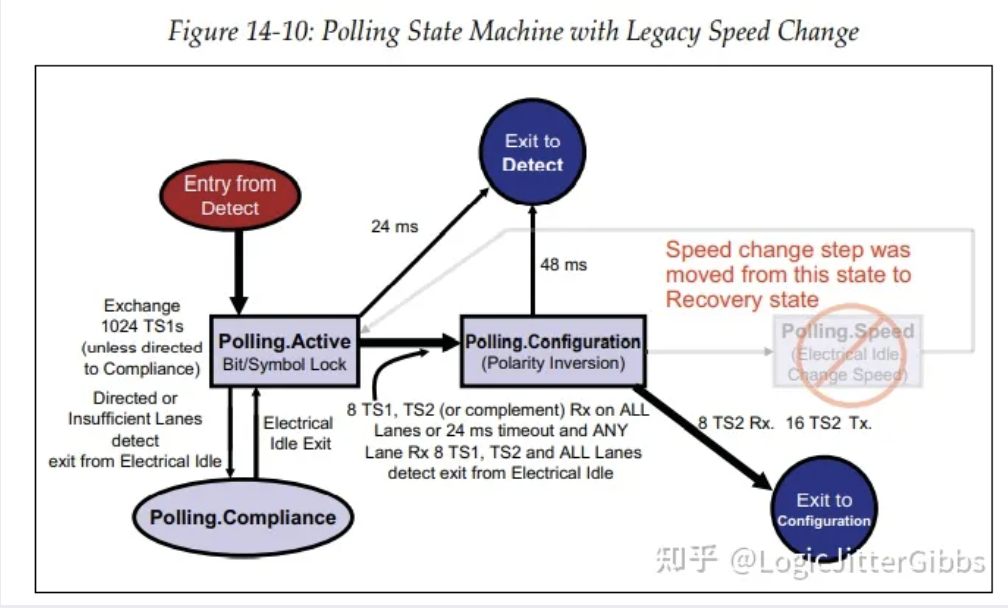

退出状态进入 Polling.Speed 子状态(现已不存在)

此处讨论的情况是一项 1.0 协议历史中的预留设计,Polling 状态下属的次状态在协议 1.0 版本发布之后已经发生了改变。在当时,设计者觉得在未来新的,更快速率出现之后,有必要在 Polling 状态中尽可能快速地切换到最高速率。然后,更高的速率出现之后,设计者意识到相比在第一次静态配置状态中把速率配置到最高速率,不如动态地根据电源管理需求,动态地提高或者降低速率。由于在 Polling 阶段需要清除大量链路的相关配置,所以重新进入 Polling 状态进行动态速率调节是不适合的,因此动态速率调节的功能被移出了 Polling 阶段,而设置于 Recover 阶段中。具体可见原文 528 页的图 14-10。

图 14-10 Polling 状态机,包含历史上的 Polling.speed 次状态

现今,LTSSM 在复位之后会总是会将速率训练为 2.5GT/s,哪怕支持更高的速率。在 LTSSM 状态机进入 L0 状态之后,一旦有更高的可用速率,状态机进入 Recovery 状态,并且尝试将速率训练为双方都支持的最高速率。双方可支持的最高速率会在双方交换的 TS1 和 TS2 序列中体现,所以任意一方都可以通过使自身的状态机进入 Recovery 状态,发起一次速率改变行为。协议中仍然会罗列 Polling.Speed 次状态,但会将其标注为不会进入(unreachable)的状态。

14.5.1.3 Polling.Compliance

Compliance 次状态用于测试。发送方会发送特定的码字组合(pattern),构建一种码间干扰和串扰接近最严重的场景,用于链路信号质量分析。在该次状态中,可以发送两类码字,分别是 Compliance pattern 和 modified compliance pattern。

译注:Polling.Compliance 一节译文暂时从略,因为译者对 PCIe 的电气部分和 Compliance 不是很熟悉。欢迎熟悉相关内容并有兴趣参加翻译的知友参与本节的翻译。

另译注:这节看上去比较短,是因为译者本来准备把 5、6 节放在一起,但是发现实在太长了,超过了知乎读者的承受能力,所以分为了单独的 5、6 两节。

原文: Mindshare

译者: LJGibbs

文章来源:https://zhuanlan.zhihu.com/p/572670988

《PCI Express Technology 3.0》翻译系列

- PCI Express Technology 3.0 链路初始化与训练 7 L0 状态

- PCI Express Technology 3.0 链路初始化与训练 Configuration

- PCI Express Technology 3.0: 链路初始化与训练 3-4 节

- PCI Express Technology 3.0 : 链路初始化与训练 1-2 节

- 《PCI Express Technology 3.0》Chapter 5

- PCI Express Technology 3.0:Chapter 1 Background/背景

- PCI Express Technology 3.0:PCIe体系结构概述 2.1 节

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3

- PCI Express Technology 3.0:PCIe体系结构概述 2.2-2.3 节(完)

更多IC设计技术干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。