常有人问MTE Tag在哪里?

MTE Tag存在于两个地方:

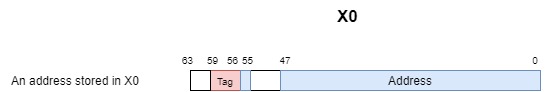

- MTE tag放在访问地址的bit 56:59,比如通过LDR Xm, [Xn]访问内存,Xn里面存放的是访问地址,当MTE使能的时候,真正用于访问内存的地址是bit 0:47(不考虑arm的52bit地址扩展)和bit 55 (bit55用于决定是高虚拟地址空间还是低虚拟地址空间),bit 56:59 这4个bit用于存放该地址的tag

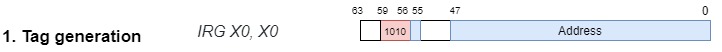

Xn的Tag生成和插入可以IRG,ADDG,SUBG等这些指令来实现:

- IRG Xn, Xn:为Xn中的地址生成一个随机的Tag,并插入到Xn的bit 56:59

- ADDG Xm,Xn,#offset,#Tag or

- ADDG Xm,Xn,#offset,#Tag: 对Xn中的地址进行加减操作,并将指令中的Tag值插入到目的寄存器中

当然软件也可以直接通过一般的指令直接改Xn寄存器的bit 56:59,比如

AND Xn, Xn, #~(0xf<<56)

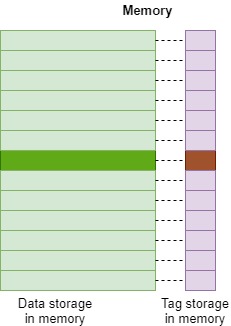

- MTE tag放在内存中(内存可以是cache或是外部内存):

每16-bye的物理地址空间有与之对应的4-bit的Tag存储空间

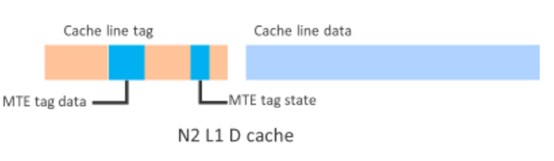

在cache中,可以如下类似方式存储一个cache line(较新处理器Data cache都是PIPT的)对应的Tag:

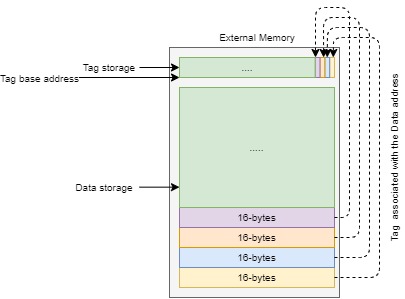

对于外部内存,实际系统中设计上,可以设计为在同一系统内存中大部分内存作为正常的数据存储使用,一部分内存用于存储数据对应的Tag(其关系是4-bit/16-byte, 既Tag的存储空间大小是正常数据存储大小的1/32)。每16-byte的物理内存对可以找到与之对应的4-bit Tag存储物理内存。

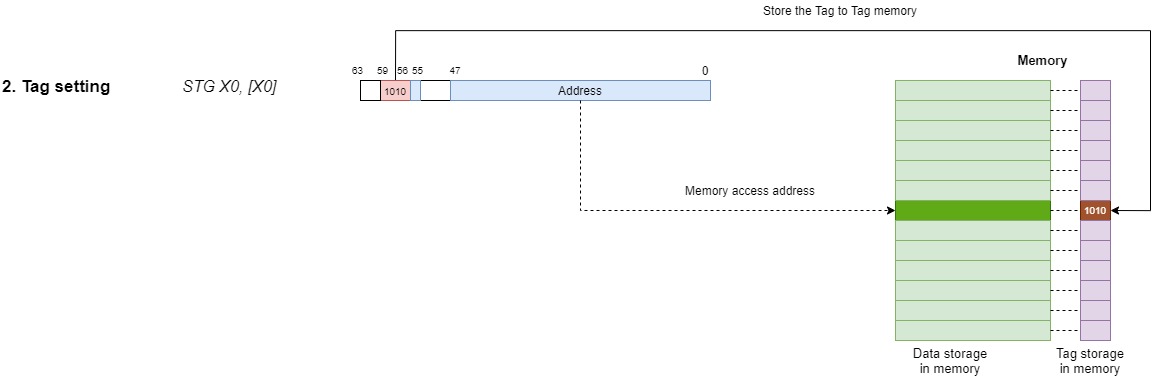

下面通过一实例来演示。

假设访问的地址放在X0中

- 为这个地址产生设置一个Tag,可以通过IRG指令来实现

- 将这个Tag保存到Tag存储内存,可以通过,STG,STGZ, ST2G / STZ2G这些指令来实现

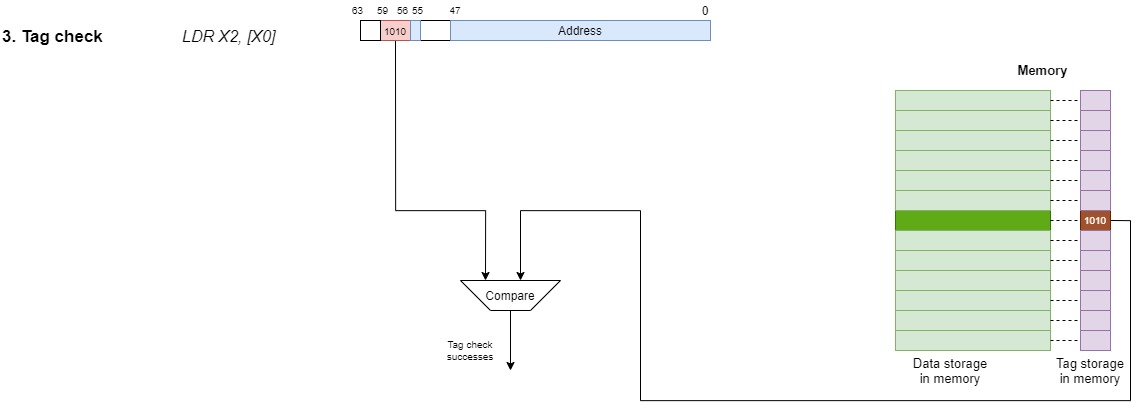

- 对Tagged内存进行load/store访问,这会触发硬件的tag check操作

在这个例子里面X0里面的tag和内存中保存的tag是match的,因此Tag Check成功。

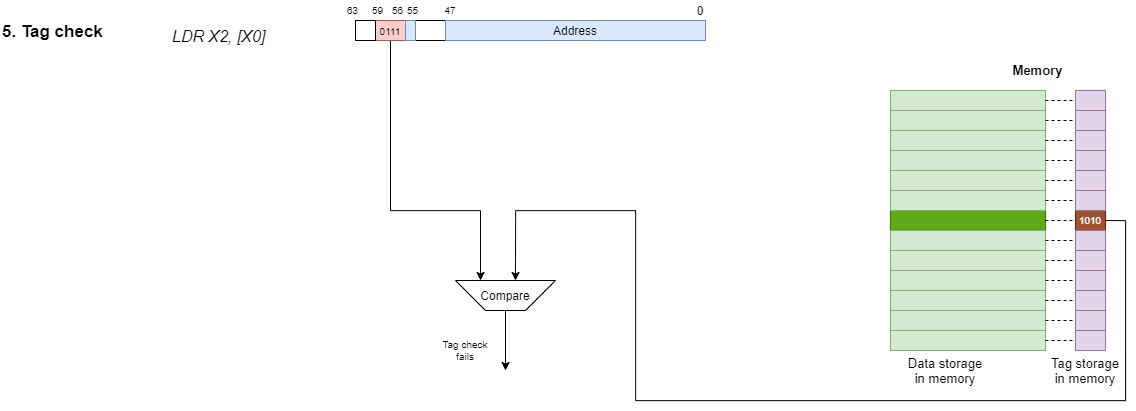

- 通过ADDG指令修改Xn中地址的Tag

- 对Tagged内存进行load/store访问,这会触发硬件的tag check操作

X0里面的tag和内存中保存的tag不match,因此Tag Check失败。

Tag存储和check的示例

以上内容阐述了tag存储和check的基本知识,下面以一个实际的例子来帮助更深入理解。

我们从上面的IRG,STG,LDR/STR等指令可以看出,Tag的存储在软件上看并没有独立的访问地址,对Tag的访问是使用其对应的数据访问地址:

- 如果数据在处理器的cache中,那么其该数据所在的cache line也可以包含数据对应的Tag, MTE Tag check可以在CPU中进行。

- 但如果数据不在cache中(cache的大小有限),那么就需要将数据和Tag存放在系统内存(DRAM)中。那系统如何在系统内存中存放和访问数据和Tag呢?Tag check发生在哪里?

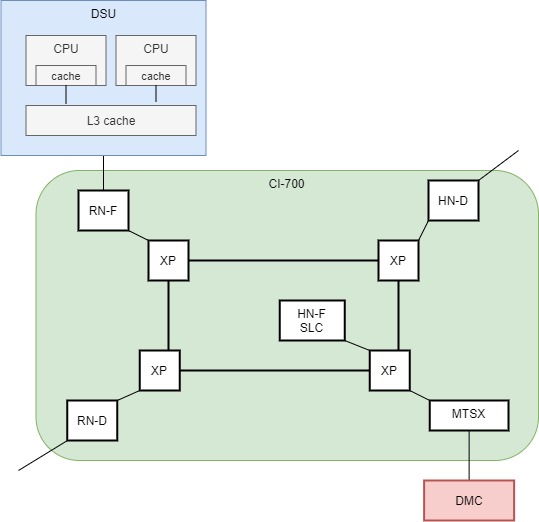

我们以一个使用CI-700的系统为例。

CI-700可以包含支持MTE Tag的system cache, 除此之外,它还可以包含MTSX,而MTSX包含:

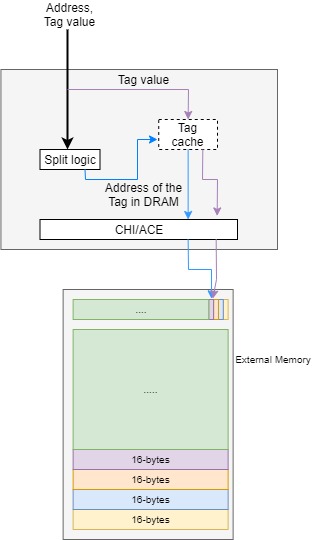

- 支持计算一个访问地址在DRAM中对应的Tag访问地址的split logic, 通过软件设置的Tag_base_address, split logic可以换算出一个地址对对应的Tag在DRAM存放的位置。

- 支持Tag check (Tag 比较)

- 支持对专门只缓存Tag值的MTE Tag cache,这是一个可选的功能。

MTSX split logic可以将CPU发送的Tagged address访问拆分成正常的数据访问和对Tag的访问,从而使DMC不需要区别正常数据访问和Tag访问(DMC对数据还是Tag访问无感,DMC不需要对MTE做特殊的支持)。

以STG X0,[X0]为例,这个指令如果在cache中miss,那么将产生一个TagOps为Update的CHI transaction,传输到MTSX,这个transaction包含放在X0中的数据访问地址和Tag Value。MTSX的split logic负责换算出这个数据访问地址对应的Tag在DRAM中的地址,然后使用这个地址将Tag value更新到DRAM中。

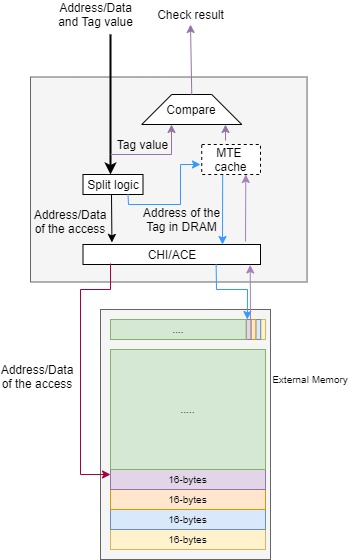

如果一个Tagged address的数据从cache中write back到DRAM中,将产生一个TagOps为Match的CHI transaction, 传输到MTSX, 这个transaction包含数据访问地址,数据值和Tag Value,MTSX的split logic负责其拆分为:

- Tag访问:换算出这个数据访问地址对应的Tag在DRAM中的地址,从这个地址中取出Tag值,然后由MTSX的Tag Compare logic比较取出Tag值和transaction带有的Tag Value。

- 正常数据写操作