✎ 编 者 按

关于仿真里的后门访问,之前的文章《三分钟教会你SpinalHDL仿真中的后门读写》中有做过介绍,其针对的都是针对以SpinalHDL中的代码进行的后门访问。今天来看看当封装了Verilog BlackBox时,在SpinalHDL仿真中如何进行后门访问Verilog代码。

BlackBox代码封装

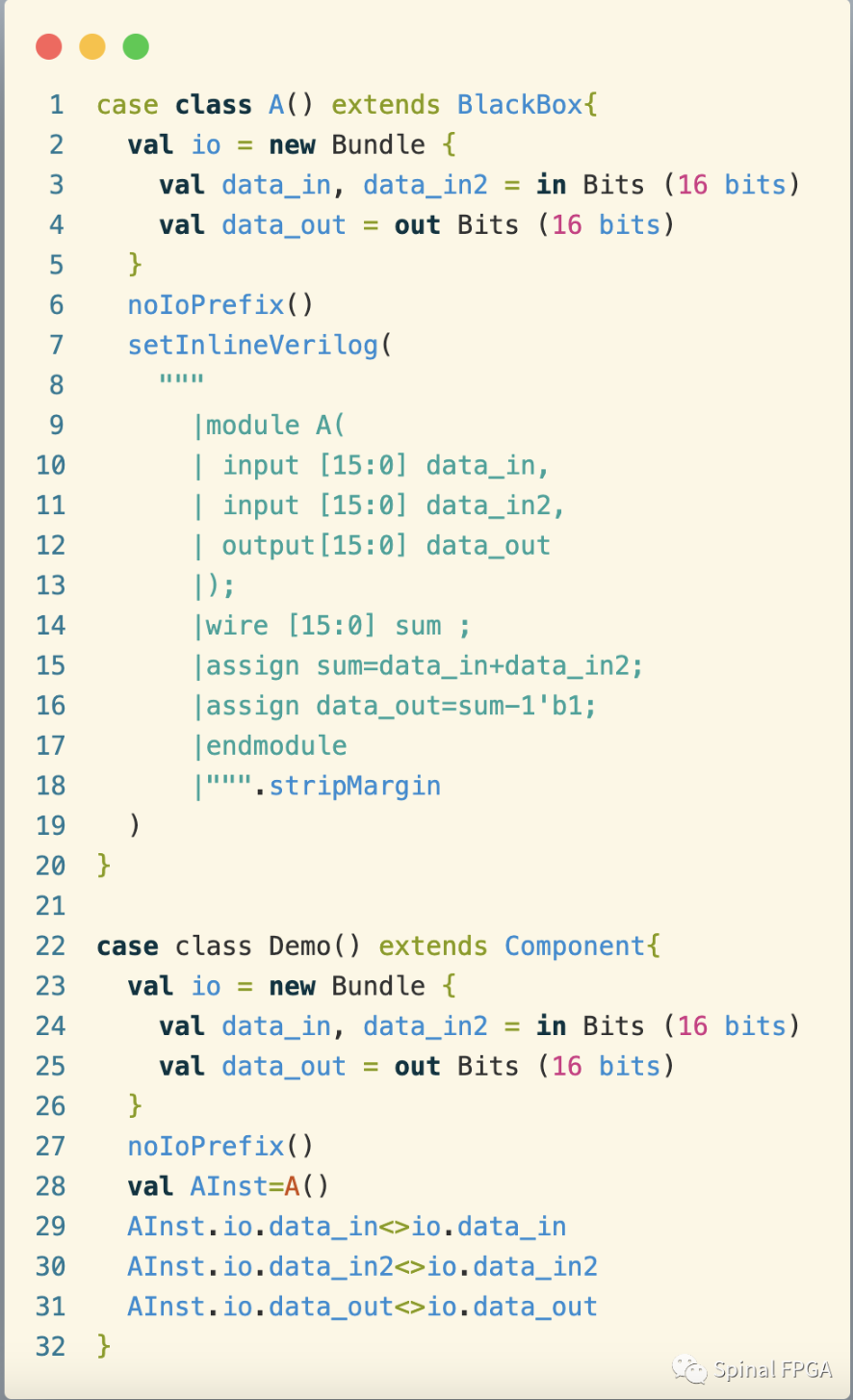

考虑下面的BlackBox代码封装:

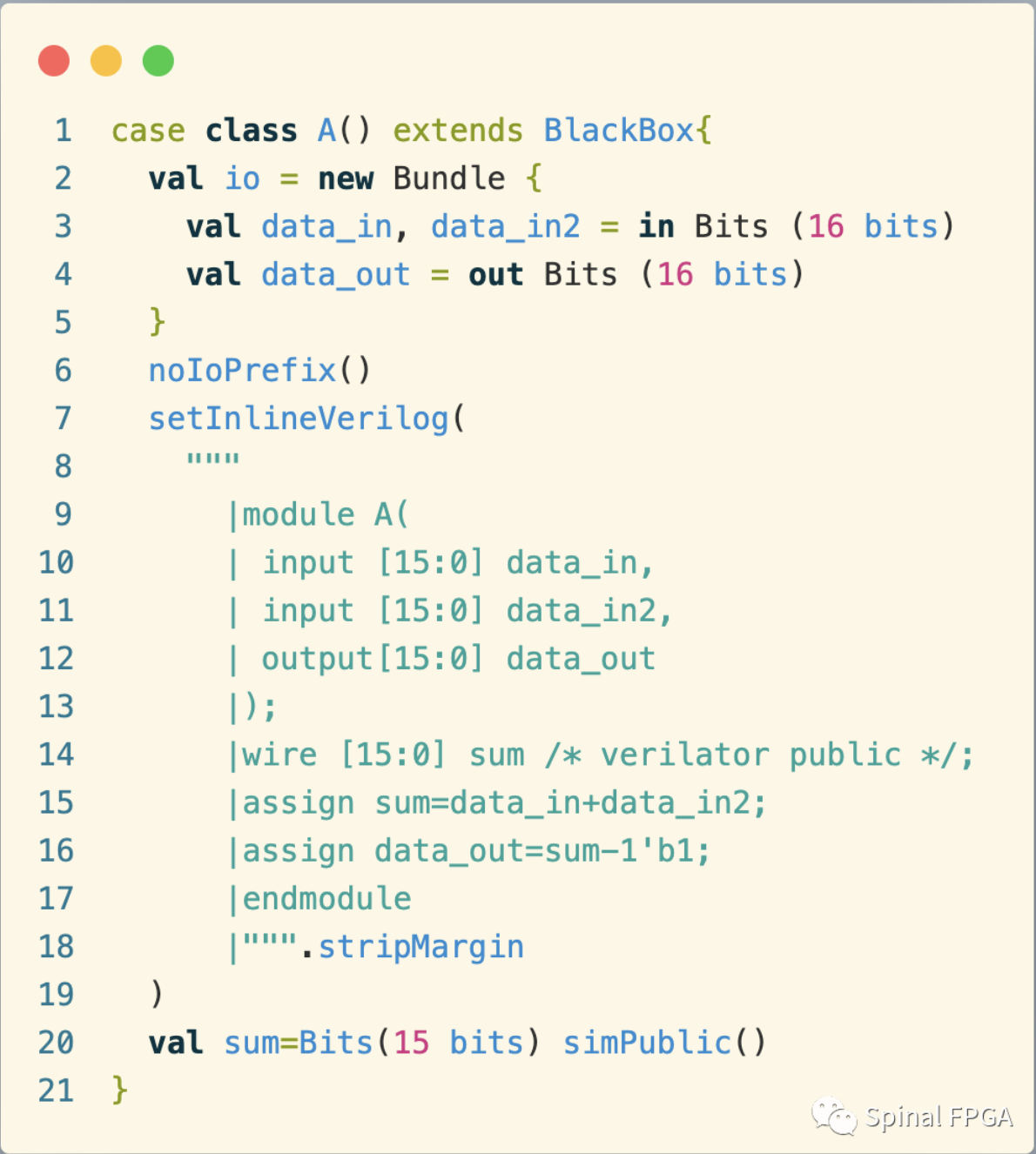

这里我们封装了一个BlackBox A,在Demo中进行例化。如果我们在仿真时如果想要后门访问模块A中的sum,那么直接访问肯定是不行的,这里就需要对BlackBox A稍进行修改:

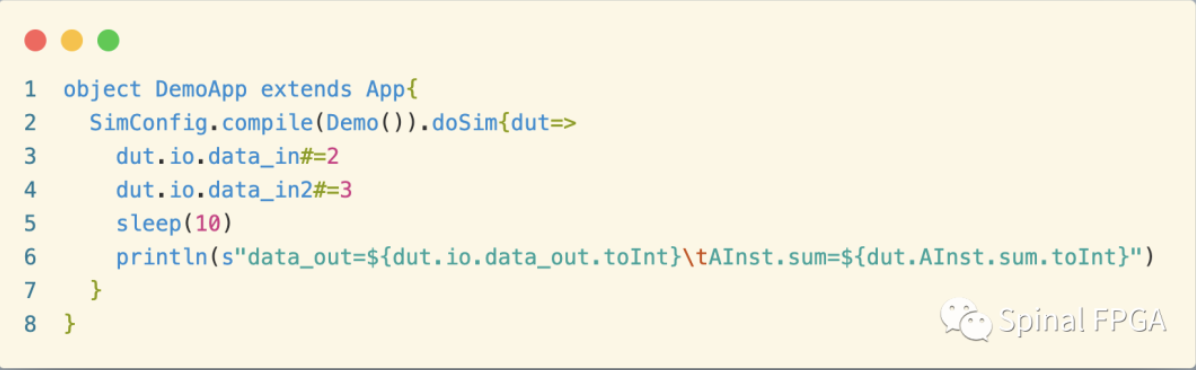

这里需要在A中例化一个sum变量并标注为simPublic,同时在RTL代码中就sum需添加/ verilator public /(注意是添加在分号前)。这样我们可以在仿真中访问A中的sum:

仿真中可以正常访问A中的sum:

[Progress] Verilator compilation done in 4112.984 ms

[Progress] Start Demo test simulation with seed 129114326

data_out=4AInst.sum=5

多层blackbox

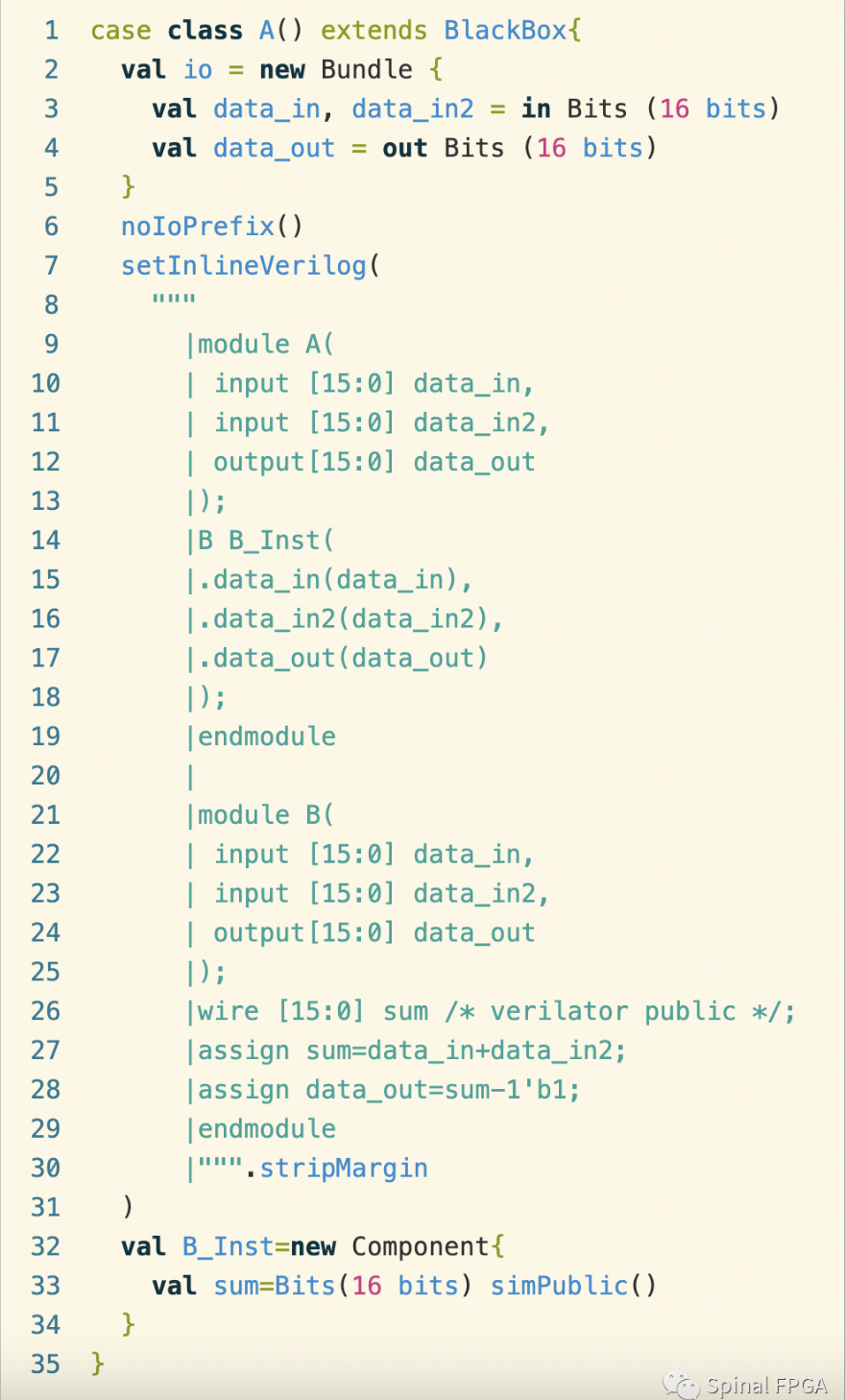

考虑下面的BlackBox:

在BlackBox A中其封装的模块A中有例化了模块B,如果我们想要访问模块B中的sum,那么除了要在sum行添加/ verilator public /外还需要对BlackBox A添加待访问sum的层次结构:

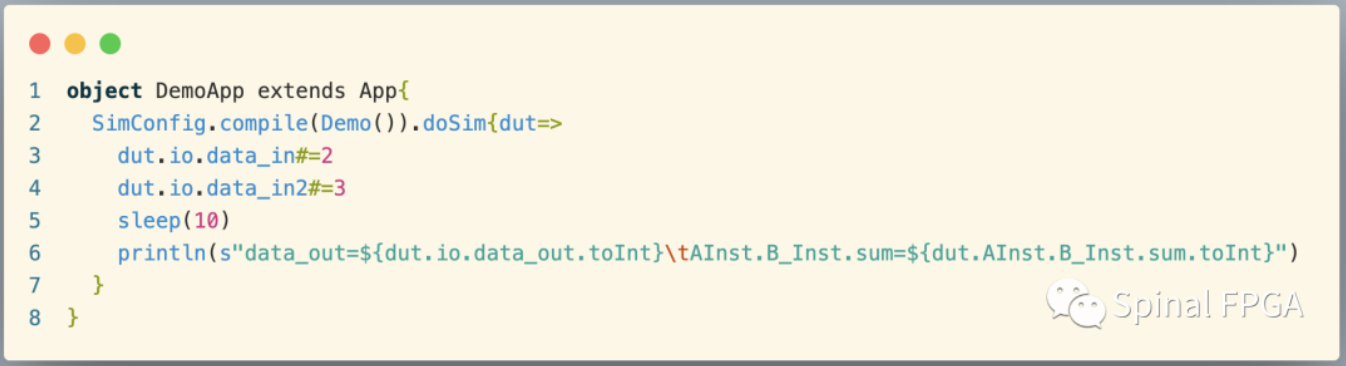

在仿真时可以访问B_Inst中的sum变量:

[Progress] Start Demo test simulation with seed 574035638

data_out=4 AInst.B_Inst.sum=5

[Done] Simulation done in 5.223 ms

写在最后

这里的仿真均采用的是Verilator,关于VCS小伙伴们可以自行探索。

☆ END ☆

作者:玉骐

原文链接:Spinal FPGA

微信公众号:

推荐阅读

更多SpinalHDL技术干货请关注[Spinal FPGA]欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。