一、GIC中断使能

对于外设中断,处理器可以通过:

- 写入GICD_ISENABLERn 寄存器的对应bit来使能该中断。

- 写入 GICD_ICENABLERn 寄存器的对应bit来禁止该中断。

对于SGI中断是否能通过上述两个寄存器来enable和disable,这个由具体的实现( IMPLEMENTATION DEFINED)来定义。

此外写入GICD_ISENABLERn 和GICD_ICENABLERn 寄存器只是控制Distributor是否能将该中断转发到CPU interface,并不会阻止该中断改变状态。比如写入GICD_ICENABLERn 寄存器来disable对应中断,并不能阻止他变成pending状态。

二、设置或清除一个中断的Pending状态

对于外设中断,处理器可以:

- 写入GICD_ISPENDRn寄存器的对应bit来设置中断状态为pending。

- 写入 GICD_ICPENDRn寄存器的对应bit来清除该中断的pending状态。

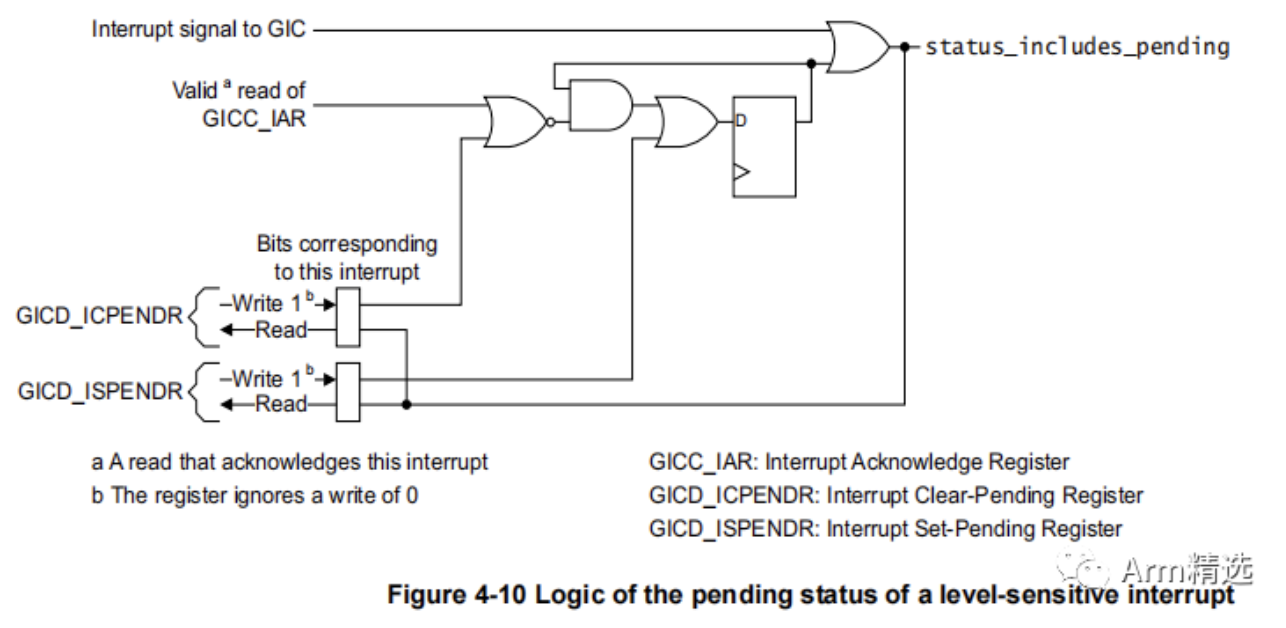

- 对于电平敏感的中断:

- 如果中断信号已经被assert,处理器再写入GICD_ICPENDRn寄存器的对应bit来清除中断将不产生作用。

- 如果处理器通过写入GICD_ISPENDRn来使对应中断状态变为pending,将忽略该中断的硬件信号,并且保留pending状态,不管该中断是被asserted还是deasserted。

包含pending的中断状态有两种:

(1)pending

(2)active and pending

- 对于边沿触发的中断来讲,包含pending的中断状态可以通过写入GICD_ISPENDRn寄存器,或者GIC对该中断信号的assertion来进行锁定。

- 但是对于电平敏感的中断来讲,它的包含pending的中断状态可以通过写入GICD_ISPENDRn寄存器来锁定,但是不能根据传递到GIC的中断信号来锁定。

以下是电平敏感中断的电路逻辑示意图:

此外,对于SGI中断,GIC将忽略对GICD_ISPENDRn和GICD_ICPENDRn寄存器的写入,处理器不能通过写入这些寄存器来改变SGI中断的中断状态。一般情况下,处理器可以通过写入 GICD_SGIR寄存器来使SGI中断变成pending,在GICv2中,SGI的pending状态可以通过直接写入GICD_SPENDSGIRn 和 GICD_CPENDSGIRn 寄存器的对应位来改变。

2.1 Interrupt Set-Pending Registers, GICD_ISPENDRn

GICD_ISPENDRn寄存器提供一个Set-pending bit,对该bit写入1能够将对应外设中断的状态设置为pending,读取对应bit则可以知道该中断是否处于pending状态。

在多处理器系统中,GICD_ISPENDR0(PPI和SGI)寄存器被每个与GIC相连的处理器banked(复用)。

从GICD_ISPENDR0开始,寄存器里每个bit代表一个不同中断ID的中断控制位,比如GICD_ISPENDR0[0]表示控制中断ID为0的中断。

对该寄存器进行读取:

- 读到0:表明对应中断在任何处理器中都不处于pending状态。

- 读到1:

- 对于SGI和PPI中断,当前中断在当前处理器中是pending状态的。

- 对于SPI中断,当前中断至少在一个处理器中处于pending状态。

上文提到过,对于SGI中断,写入GICD_ISPENDRn寄存器的操作将会被忽略,因为SGI有自己的Set-pending寄存器 SGI

Set-Pending Registers, GICD_SPENDSGIRn。对于SPI和PPI中断来讲:

- 写入0:无影响

- 写入1:其效果取决于是边缘触发还是电平敏感中断:

- 边缘触发(Edge-triggered),如果当前中断已经是pending状态,则不受影响;如果之前是inactive状态,则会变成pending状态;如果之前是active状态,则会变成active and pending状态。

- 电平敏感(Level sensitive),如果当前中断已经是pending状态,如果对应中断信号已经被asserted,写操作将不会改变中断的状态,但是该中断信号被deasserted后该中断将仍保持pending状态;如果对应中断未处于pending状态,如果之前是inactive状态,则会变成pending状态;如果之前是active状态,则会变成active and pending状态。

2.2 Interrupt Clear-Pending Registers, GICD_ICPENDRn

GICD_ICPENDRs为GIC支持的每个中断提供一个Clear-pending bit。写入对应中断的Clear-pending位将清除该中断的pending状态。读取该bit位是否为1可以确定中断是否处于pending状态。

对该寄存器进行读取:

- 读到0:表明对应中断在任何处理器中都不处于pending状态。

- 读到1:

- 对于SGI和PPI中断,当前中断在当前处理器中是pending状态的。

- 对于SPI中断,当前中断至少在一个处理器中处于pending状态。

对于SPI和PPI中断来讲:

- 写入0:无影响

- 写入1:其效果取决于是边缘触发还是电平敏感中断:

- 边缘触发(Edge-triggered),如果中断不处于pending状态,则不受影响。如果之前是pending状态,则会变成inactive状态;如果之前是active and pending状态,则会变成active状态。

- 电平敏感(Level sensitive),如果当前中断的pending状态是由于写入GICD_ISPENDRn寄存器导致的:如果之前是pending状态,则会变成inactive状态;如果之前是active and pending状态,则会变成active状态。否则,如果中断信号仍被asseted,中断将保持pending状态。

三、查找处于active或者pending状态的中断

若想知道一个中断是否处于pending状态,可以读取 GICD_ISPENDRn 或者GICD_ICPENDRn寄存器。若想知道中断是否处于active状态,可以读取 GICD_ISACTIVERn 或者GICD_ICACTIVERn,这两个寄存器有Set-active和clear-active 位用来控制中断的active状态。

四、产生SGI中断

处理器可以通过写入GICD_SGIR寄存器来产生一个SGI中断,一个SGI中断可以设置多个目标处理器,并且SGIR寄存器里有目标寄存器列表。GICD_SGIR包括如下优化:

- 只中断写入GICD_SGIR的处理器

- 中断除写入GICD_SGIR的处理器以外的所有处理器

- 来自不同处理器的SGI中断使用同一个中断ID,所以任何目标处理器可以收到来自不同处理器产生的相同中断ID的SGI。但是如果以下条件不同,则任意两个SGI中断的pending状态是独立的:

- 中断ID

- 源处理器

- 目标处理器

在CPU interface中,在任何时候,一次只能有一个特定中断ID的中断处于active状态,这意味着CPU interface不能同时有两个SGI处于active状态,甚至是不同处理器使用相同中断ID的SGI中断发送中断信号到该处理器。

在目标处理器的CPU interface中,通过读取 GICC_IAR寄存器,可以获得中断ID,以及产生该中断的CPU ID,即源处理器ID。中断ID加上源处理器ID,可以让目标处理器获知该中断独一无二的来源。

此外,在多处理器系统中,每个SGI中断的优先级可以为每个目标处理器单独设置,详情可查看 Interrupt Priority Registers, GICD_IPRIORITYRn,中断优先级寄存器。对于每个CPU interface来讲,对于所有优先级相同的,特定中断ID的,处于pending状态的SGI中断,CPU interface序列化地处理它们,具体的系列化处理顺序取决于系统的实现定义(IMPLEMENTATION SPECIFIC.)。

4.1 Software Generated Interrupt Register, GICD_SGIR

处理器写入GICD_SGIR可以产生SGI中断。使用限制:通过写入 GICD_CTLR寄存器来将Distributor的转发功能禁止,是否会影响GICD_SGIR,这个由具体的实现定义( IMPLEMENTATION DEFINED)。以下是GICD_SGIR寄存器的字段分配图:

- [25:24] TargetListFilter:这将决定Distributor如何处理被请求的SGI中断,即要转发到何处:

- 0b00:将中断转发到在CPUTargetList定义的CPU interface中

- 0b01:将中断转发到所有CPU interface中,除了当前请求中断的处理器。

- 0b10:将中断转发到当前请求SGI中断的处理器相连的CPU interface中。

- 0b11:保留

- [23:16] CPUTargetList:如果TargetListFilter的值为0b00,CPUTargetList中将定义Distributor必须被转发到的CPU interface。CPUTargetList中共八个bit,每个bit代表一个处理器。比如CPUTargetList[0]对应CPU interface 0,如果CPUTargetList[0]=1,表明该SGI中断必须转发到CPU interface 0。如果TargetListFilter的值为0b00,并且CPUTargetList也为0,说明Distributor不需要将中断转发到任何CPU interface。

- [15] NSATT:仅在系统包含安全扩展中实现,如果没有实现安全扩展,这个字段将保留。NSATT指定SGI需要的security value:

- 只有当SGI在该CPU interface上被配置为Group 0时,才将SGIINTID字段中指定的SGI转发到指定的CPU interface。

- 只有当SGI在该CPU interface上被配置为Group 1时,才将SGIINTID字段中指定的SGI转发到指定的CPU interface。

- 该字段只可以在安全状态下被写入,只有当指定的SGI中断被配置成group 1时,任何对GICD_SGIR的非安全写入才会生成SGI,并且忽略NSATT的值。

- [3:0] SGIINTID :需要被转发到指定的CPU interface中的SGI中断的中断ID,范围是0到15。

4.2 安全扩展下产生SGI中断

如果GIC实现了安全扩展,通过写入GICD_SGIR寄存器,使得SGI中断转发到指定的处理器,这取决于:

- 写入GICD_SGIR的是Group 0(secure)还是Group 1(non-secure)

- 对于secure写入SGIR,写入 GICD_SGIR的NSATT字段的值。

- 在目标处理器中,特定的中断是否被配置成Group 0(secure)还是Group 1(non-secure)。

GICD_IGROUPR0寄存器中保存了SGI中断的安全状态。在多处理器系统中, GICD_IGROUPR0被每个与之相联的处理器banked(复用),所以系统可以为每个处理器独立设置SGI中断的安全状态。对GICD_SGIR寄存器写一次,可以配置多个目标处理器,对于每个目标处理器,Distributor将决定是否将SGI中断转发到该处理器。

下表展示了Distributor是否可以将SGI转发到指定的CPU interface的真值表:

五、GIC 1-N模型

GIC在多处理器实现中,会使用1-N模型,处理有多个目标处理器的外设中断,比如SPI。这意味着,这意味着,当GIC从其中一个目标处理器识别出一个中断确认时,它将清除所有其他目标处理器上的中断的pending状态。GIC必须确保使用1-N模型处理的任何中断时,只能被一个CPU interface确认,并且所有其他CPU interface都返回一个虚假中断ID。

当目标处理器试图确认中断时,有两种情况会发生:

- 处理器读取 GICC_IAR寄存器,并获得需要被服务的中断的ID。在GICv1中,如果多个处理器读取GICC_IAR寄存器的时间非常接近,可以会有多个处理器会获取到该中断ID。系统必修要求在目标处理器上运行的软件来确保只有一个处理器能进行中断服务程序。一种典型的实现方案是使用共享内存,并且在中断服务程序(interrupt service routine,ISR)中加锁。

- 处理器读取 GICC_IAR寄存器,获取到虚假中断ID:1023。该处理器会从中断服务程序中返回,并且不用写入GICC_EOIR寄存器。读到虚假中断ID,是因为原始的中断不再 处于pending状态,一般是因为有其他目标处理器在处理该中断。

作者:lvy

文章来源:Arm精选

推荐阅读

欢迎关注ARM精选专栏, 欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。