4.5 DLL-off模式

DDR4 SDRAM的DLL-off模式是通过配置MR1寄存器的A0为0来进入的。在此模式中,DLL将不会有任何操作,知道MR1寄存器的A0重新被配置为1。DLL-off模式可在初始化过程中,或者是在初始化完成之后进入。具体可参考4.6节“改变输入时钟频率”。

下面列表中的的DLL-off模式时DDR4 SDRAM的可选操作模式。DLL-off模式中的可使用的最大时钟频率为参数tCKDLL_OFF所限定的。且没有最低时钟频率要求,除了需要满足tREFI的要求(刷新时间间隔)。

由于延迟计数以及时序约束,仅支持MR0寄存器中一种CL值,以及MR2寄存器中一种CWL值,DLL-off模式仅支持CL=10与CWL=9。且一旦进入DLL-off模式,CA奇偶检验功能将不可用。

DLL-off模式会影响读数据时钟与数据选通信号的时序关系tDQSCK。但是不影响tDQSQ与tQH。特别需要注意的是需要将读数据按次序返回给控制时钟域。

对比DLL-on模式,从读命令后的AL+CL个时钟上升沿()后开始计算时间tDQSCK,而DLL-off模式则是从读命令后的AL+CL-1时钟上升沿开始计算时间。

另一个区别在于DLL-off模式中,tDQSCK是不小于tCK的,而且tDQSCKmin与tDQSCKmax都会比DLL-on模式中的大很多。tDQSCK(DLL-off)使用设备商来提供说明。

下图中是DLL-off模式中的读操作时序关系图(CL=10,BL=8,PL=0)

4.6 改变输入时钟频率

DDR4 SDRAM初始化完成之后,在进行大多数普通的操作时要求时钟的相对稳定的。这就意味着一旦时钟频率设定好,就要一直保持着这种稳定状态,在此期间,时钟周期不允许改变,除了时钟的jitter与SSC(展频)。

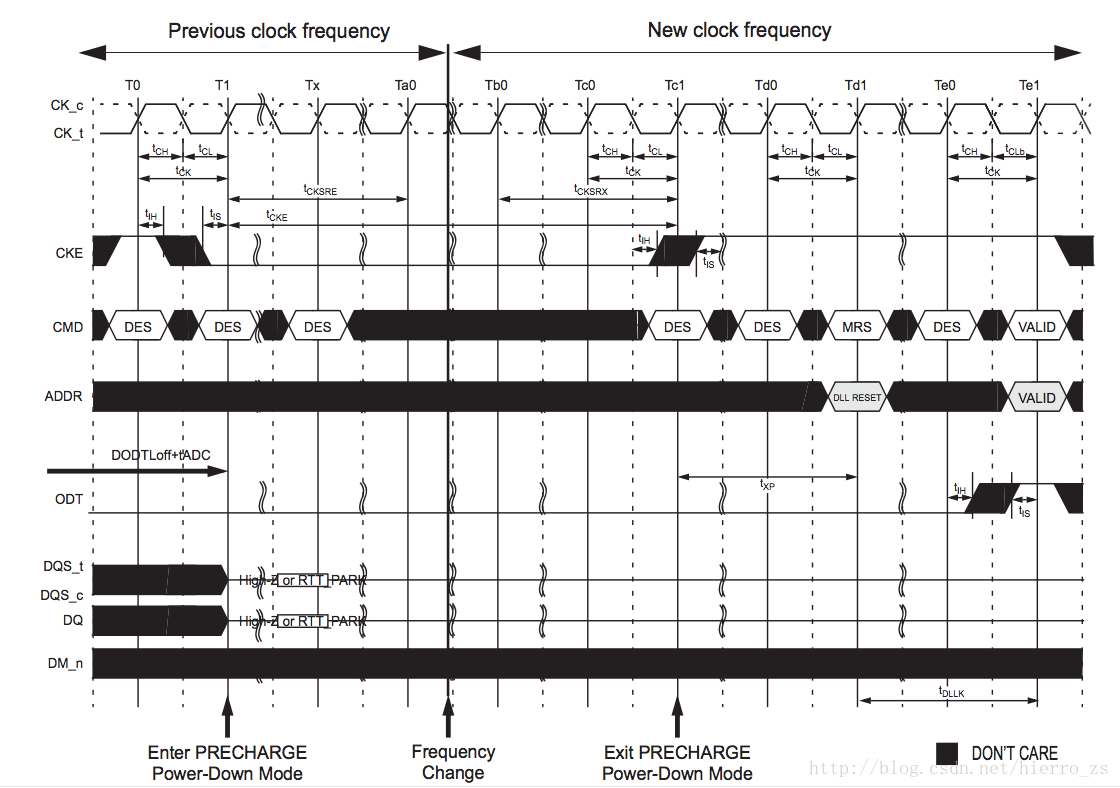

在Self-refresh模式与Precharge Power Down模式下可以让输入时钟频率由当前的稳定状态改变的到另一个稳定状态。除此两种模式以外的时钟频率改变都是不合法的。在第一种情况下,一旦DDR4 SDRAM成功进入Self-refresh模式且已满足tCKSRE时间,那么此时输入时钟的频率就不需要关心了。一旦不关心输入时钟的频率,那么就可以改变输入时钟频率,需要注意的是必须在tCKSRX时间之前提供新的输入时钟。如果进入Self-refresh模式仅仅是为了改变输入时钟的频率那么进入与退出的时序要求需要满足4.27节“Self-refresh操作”中的要求。但是,由于DDR4 DLL的锁定时间范围是从597nCK(1333MT/s)到1024nCK(3200MT/s),所以需要为新的时钟频率配置相应的模式寄存器值。

NOTE :

- tCKSRE与tCKSRX都是Self-refresh模式中的参数,但是他们的值在此处也是可以适用的。

- 如果在进入Precharge Power-Down模式之前通过配置模式寄存器来时能了RTT_Nom阻抗特性,那么在整个过程中ODT都必须保持低电平以保证确保RTT是处于关闭状态。若在进入Precharge Power-Down模式之前通过配置模式寄存器已经禁止了RTT的功能活着DRAM的ODT信号的输入无效已是能,那么就意味着RTT将一直保持关闭状态。

- 如果RTT_PARK已经禁止货ODT输入缓冲也没有无效,那么在这种状态下ODT的值就不关心了

4.7 Write Leveling

为了达到更好的信号完整性,DDR4 SDRAM存储模块采用了拓扑结构的命令、地址、控制信号以及时钟。拓扑结构有利于减少根节的数量及其长度,同时也带来了DIMM上每个DRAM之间的时钟与选通信号的飞线偏移时间。这就导致控制器很难去保证tDQSS、tDSS与tDSH的要求。因此,DDR4 SDRAM就支持采用一种名叫“write leveling”的功能,来使得控制器能够补偿该偏移时间。该功能并不是在每一个DDR4 SDRAM系统上都是必须的,比如说在主机能够很好的维持tDQSS、tDSS以及tDSH时间的情况下。

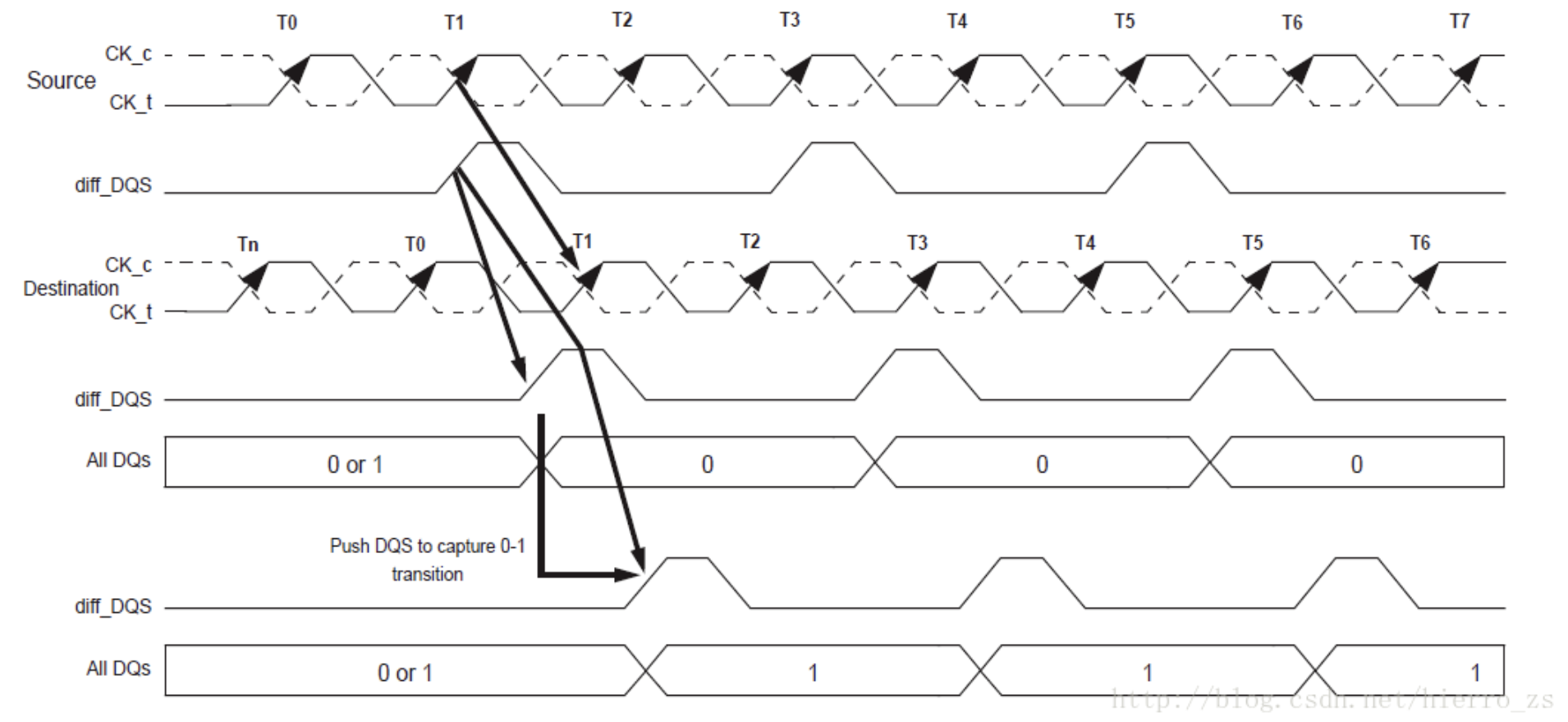

存储控制器可使用“write leveling”功能,并补偿DDR4 SDRAM的DQS差分信号与CK差分信号之间的关系。存储控制器需要再leveling过程中将调整DQS差分信号的延迟,从而使DRAM的接口上的DQS差分信号与CK差分信号的两个上升沿对齐。同时DRAM通过DQ总线异步返回由DQS差分信号的上升沿采样的CK差分信号值。控制器需要重复性的调整DQS差分信号的延迟,知道检测到DQ总线上出现一个0到1的跳变。通过这种调整,就可以满足tDQSS的要求,此外tDSS与tDSH也需要被满足。唯有通过调整到适合的DQS差分信号周期与jitter才能满足实际的tDQSS要求。根据实际应用中的tDQSS,为了满足“AC时序参数”中tDSS以及tDSH的要求,实际上的tDQSL与tDQSH都会比“AC时序参数”中要求的限制要小一些。概念上的时序图如下所示。

在Write Leveling过程中,由控制器驱动的DQS差分信号必须由DRAM上相应的rank来终结,同样的,DRAM驱动的DQ信号也必须由控制器来终结。

无论x4、x8、x18,所有数据位都需要加载Leveling的反馈给控制器。在x16设备中,两个bytelane都需要单独进行Leveling。因此,每个bytelane都需要有一套单独的反馈机制。上半区的数据需要反馈上半区diff_DQS与CK的关系,同样,下半区的数据需要反馈下半区diff_DQS与CK的关系。

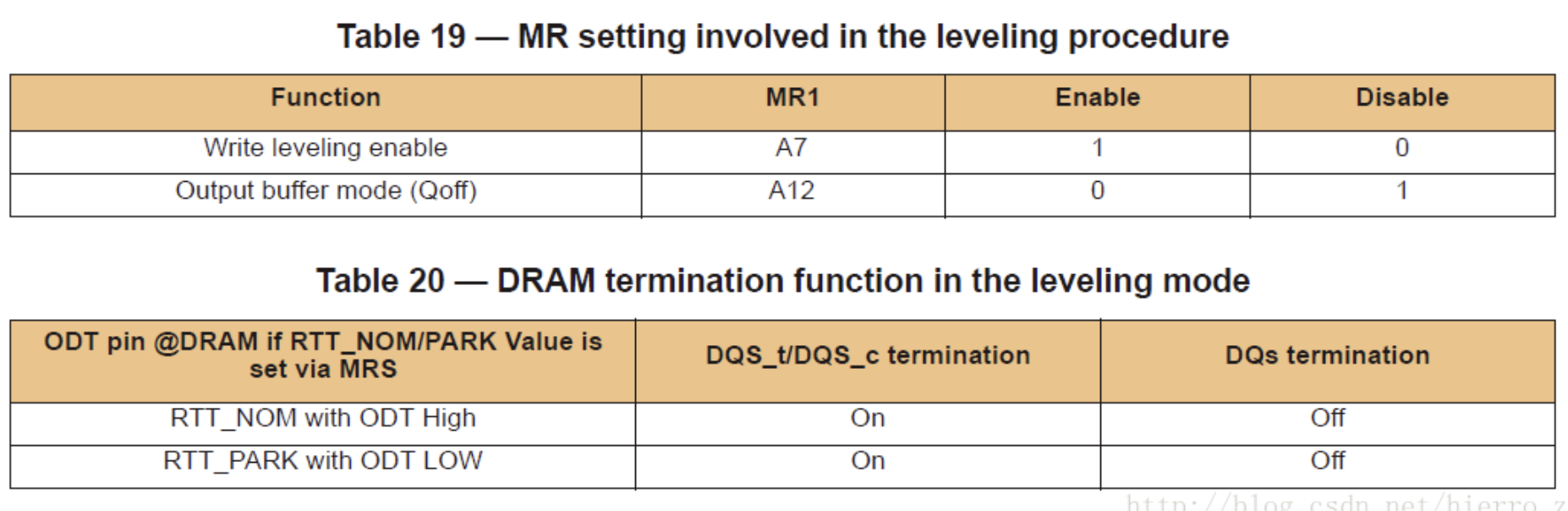

4.7.1 Write Leveling模式中RAM的设置与DRAM终结电阻的功能

通过配置MR1寄存器的A7位为1来进入Write Leveling模式,并通过将此位拉低为0来退出Write Leveling模式。需要注意的是,在Write Leveling模式中,仅有DQS_t/DQS_c的终端电阻是收ODT引脚控制来进行开启与关闭的,与普通操作是由区别的。

NOTE 1 在Write Leveling模式中若输出缓冲是禁止的(MR1[bit A7] = 1 with MR1[bit A12] = 1),那么所有的RTT_Nom与RTT_PARK的配置都是允许的;若输出缓冲是开启的(MR1[bit A7] = 1 with MR1[bit A12] = 0),那么RTT_Nom与RTT_PARK仅有TBD是可用的。

4.7.2 流程描述

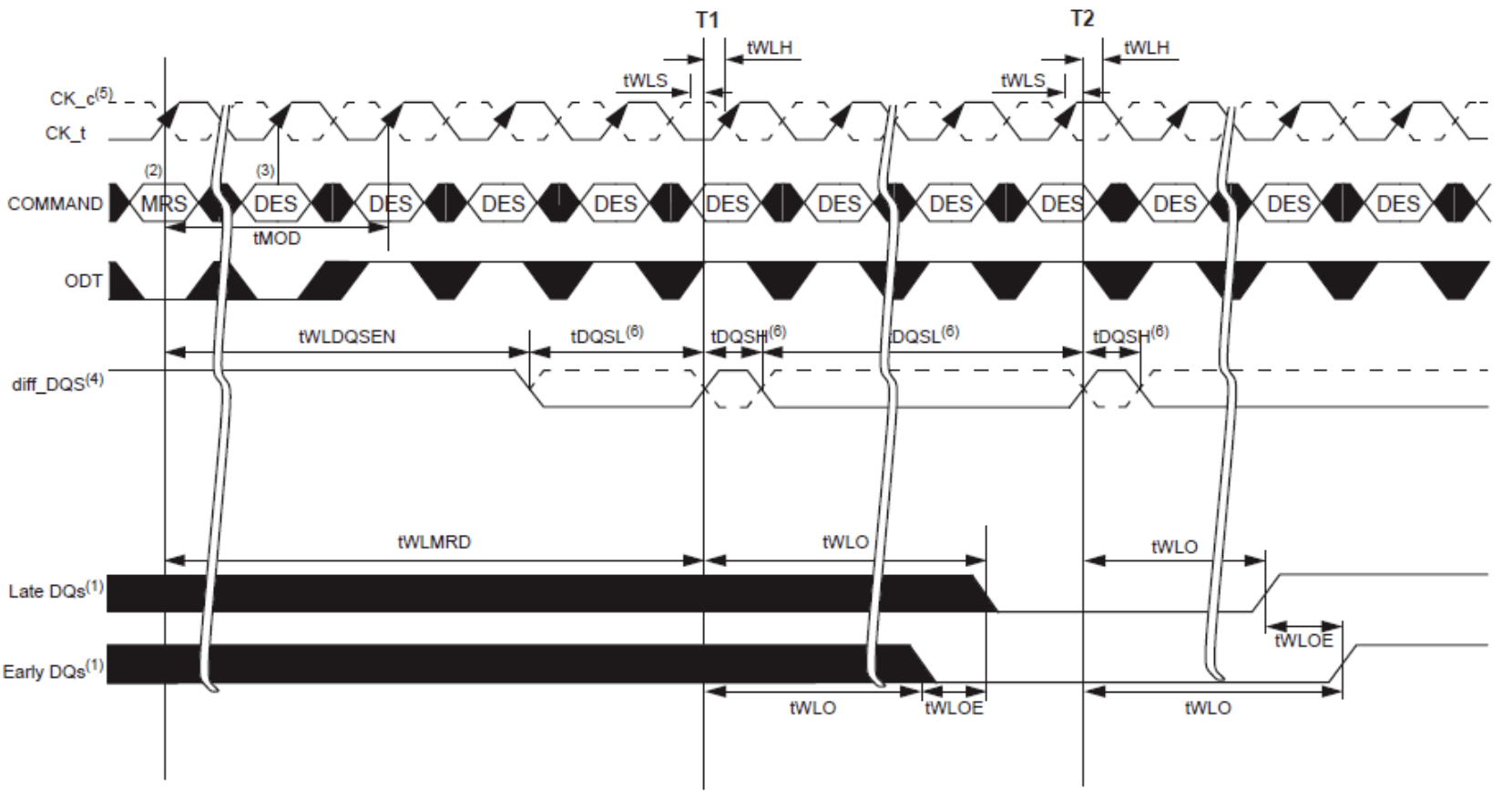

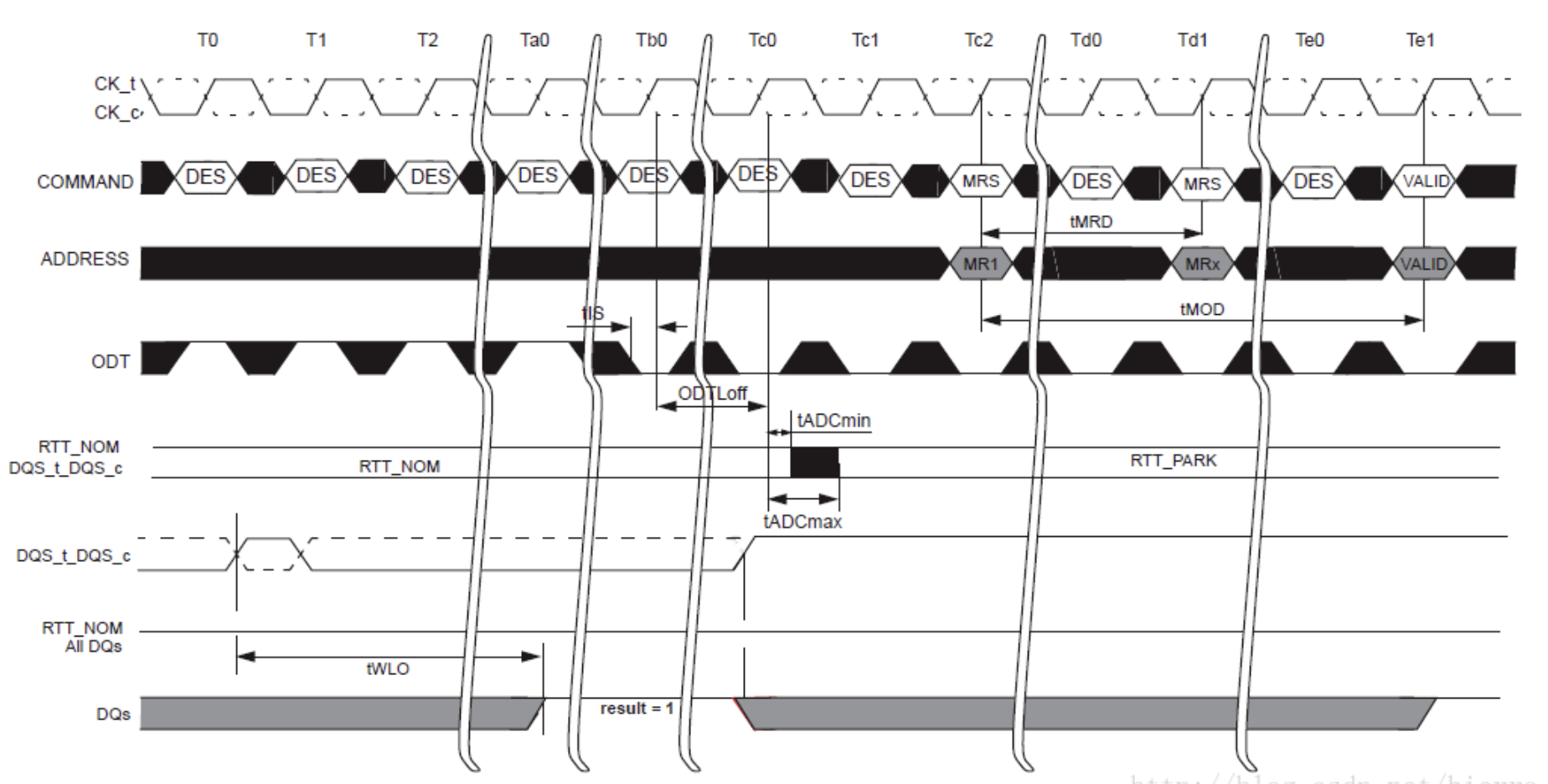

存储控制器通过配置MR1寄存器的A7为1来启动Write Leveling(以下简称WL)。一旦进入WL模式,DQ引脚就会进入未定义的驱动模式。在WL过程中,仅有DESELECT命令可以发送,就像修改Qoff(MR1[12])位以及退出WL(MR1[7])位的命令允许被发出来。当退出WL模式时,MRS命令在改变MR1[7]的同时,也会更改A12-A8与A2-A1。由于在控制层面每次仅使能一个RANK,所有其他Rank的输出将会被禁用,通过设置MR1[12]为1,可达到此目的。控制器会在tMOD时间后将ODT信号置1,此时DRAM已经准备好接受ODT信号。

在设置好DRAM的DQS_t与DQS_c的ODT阻值之后,控制器会将这一对差分信号分别置为低电平(DQS_t)与高电平(DQS_c),且需满足tWLDQSEN的时间条件。在tDQSL与tWLMRD之后控制器会将DQS与DQS#信号加上一个单个,同时DRAM采用这对差分信号来采用CK-CK#,此时CK-CK#是由控制器来提供的,时序参数tWLMRD(max)是由控制器来确定的。

DRAM通过DQS_t与DQS_c#采样CK-CK#之后,在tWLO时间后,会将采用结果反馈至所有DQ信号上。每一根DQ信号线都能提供WL的反馈。在第一次采样过程之后,DRAM剩余的DQ位被稳定地驱动至低电平。在DQ的输出时,tWLOE时间内是允许DQ为不定态的。tWLOE的意义是,在一次传输中,从最早跳变一位的跳变DQ开始,到最晚一位DQ跳变的时间。这些DQ为不需要DQS_t与DQS_c来进行选通。控制器会自行决定采样DQ,并增加或减少DQS_t与DQS_c的延迟,在若干时间后运行一下次的DQS_t与DQS_c脉冲。一旦0->1跳变被检测到,控制器就会锁定此DQS_t与DQS_c的延迟,此时该设备的WL已完成。

NOTE 1 DDR4 SDRAM通过所有DQ引脚来反馈WL

NOTE 2 MRS:加载MR1寄存器来进入WL模式

NOTE 3 DES:Deslect命令

NOTE 4 diff_DQS为(DQS_t与DQS_c)的差分叠加数据。时序参考点为零点穿越处。DQS_t为实线,DQS_c为虚线。

NOTE 5 CK_t/CK_c:CK为实线,CK_c为虚线显示

NOTE 6 DQS_t与DQS_c需要满足tDQSH与DQSL所限制的最小脉冲宽度,以完成一个正常的写请求。最大脉冲宽度则是由系统确定。

4.7.3 退出Write Leveling模式

以下序列描述了如何退出WL模式:

- 在最后一次选通信号的上升沿之后(见T0),停止驱动选通信号。此时,DQ将为无驱动状态,并保持此状态至MR命令之后的tMOD时间(见Te1)。

- 将ODT拉低,并保持低电平,此时tIS需要满足。(见Tb0)

- 当关闭Rtt后,使用MRS命令将WL模式关闭。(见Tc2)

- 在tMOD时间后,可向DRAM发送其他命令 。(见Td1)

原文:CSDN

作者:hierro_sic

相关文章推荐

- JESD79-4 第4章 SDRAM命令描述与操作(4.1-4.4)

- JESD79-4 第3章 功能描述

- JESD79-4 第2章 DDR4 SDRAM 的引脚封装与寻址

- DDR 学习时间:学习 Micron DDR4 TN-40-07: DDR4 功耗估算 (2)

- DDR 学习时间 (Part C - 1):DFI 协议简介、演进和协议下载

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。